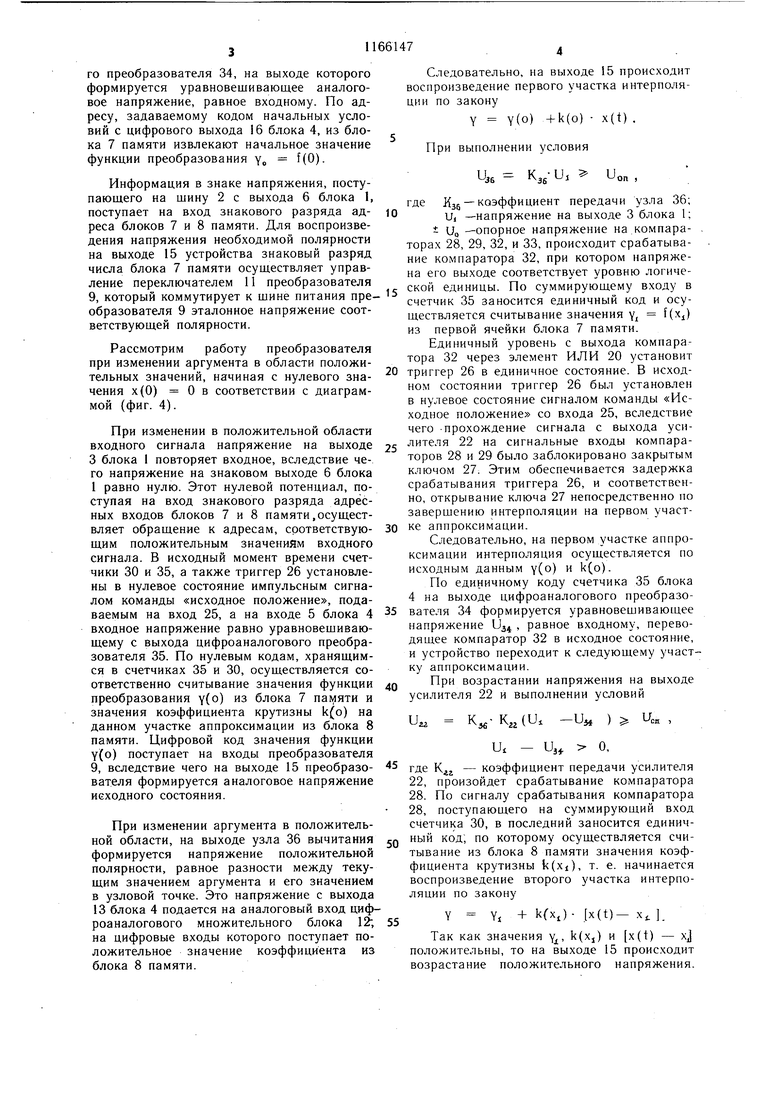

ми - соответственно к суммирующему и вычитающему входам счетчика, информационный вход и цифровой выход которого являются соответственно входом начальной установки и цифровым выходом блока

аналого-цифрового преобразования, а выходы компараторов являются соответственно выходами прибавления и вычитания единицы младщего разряда блока аналогоцифрового преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный преобразователь | 1986 |

|

SU1403078A1 |

1. ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок аналого-цифрового преобразования, подключенный цифровым выходом к адресному входу первого блока памяти, соединенного выходами разрядов с цифровым входом цифроаналогового преобразователя, подключенного выходом к первому входу выходного сумматора, второй вход которого . соединен с выходом цифроаналогового множительного блока, подключенного цифровым входом к выходам разрядов второго блока памяти, а аналоговым входом - аналоговому выходу сигнала рассогласования блока аналогоцифрового преобразования, отличающийся тем, что, с целью повышения точности преобразования знакопеременных сигналов, в него введены счетчик, дешифратор нуля, компараторы, усилитель, формирователи импульсов, триггер, элементы ИЛИ, ключ и блок выделения модуля и знака входного сигнала, соединенный входом с шиной ввода аргумента преобразователя, выходом знака сигнала - со знаковыми разрядами адресных входов первого и второго блоков памяти, а выходом модуля сигнала - с информационным входом блока аналого-цифрового преобразования, подключенного входом начальной установки к шине задания начальных условий преобразователя и к входу haчальной установки счетчика, выходами прибавления и вычитания единицы младшего разряда - к первому и второму входам первого элемента ИЛИ, а аналоговым выходом сигнала рассогласования - к входу усилителя, соединенного выходом с сигнальным входом ключа и с входом первого формирователя импульсов, подключенного выходом к третьему входу первого элемента ИЛИ, соединенного выходом с установочным входом триггера, вход обнуления которого соединен с выходом второго элемента ИЛИ, а выход - с управляющим входом ключа, подключенного выходом к первым входам перi вого и второго компараторов, соединенных вторыми входами с шинами ввода разнопоСП лярных опорных напряжений, а выходами - соответственно с суммирующим и вычитающим входами счетчика, подключенного цифровым выходом к адресному входу второго блока памяти, причем второй элемент ИЛИ соединен первым .входом с входом приведения в исходное состояние преобразователя, а вторым входом - с выходом дешифО5 ратора нуля, подключенного входами к выС5 ходам разрядов первого блока памяти, кроме его знакового разряда. 2. Преобразователь по п. 1, отличающий4 ся тем, что блок аналого-цифрового преобразования содержит узел вычитания, два компаратора, счетчик и цифроаналоговый , преобразователь, подключенный цифровым входом к выходам разрядов счетчика, а выходом - к первому входу узла вычитания, второй вход которого соединен с информационным входом блока аналого-цифрового преобразования, а выход - с аналоговым выходом сигнала рассогласования блока аналого-цифрового преобразования и с первыми входами компараторов, подключенных вторыми входами к щинам ввода разнополярных опорных напряжений, а вь1хода

1

Изобретение относится к автоматике и вычислительной технике и может найти при,менение в гибридных вычислительных системах и в специализированных устройствах обработки информации.

Целью изобретения является повышение точности преобразования знакопеременных сигналов.

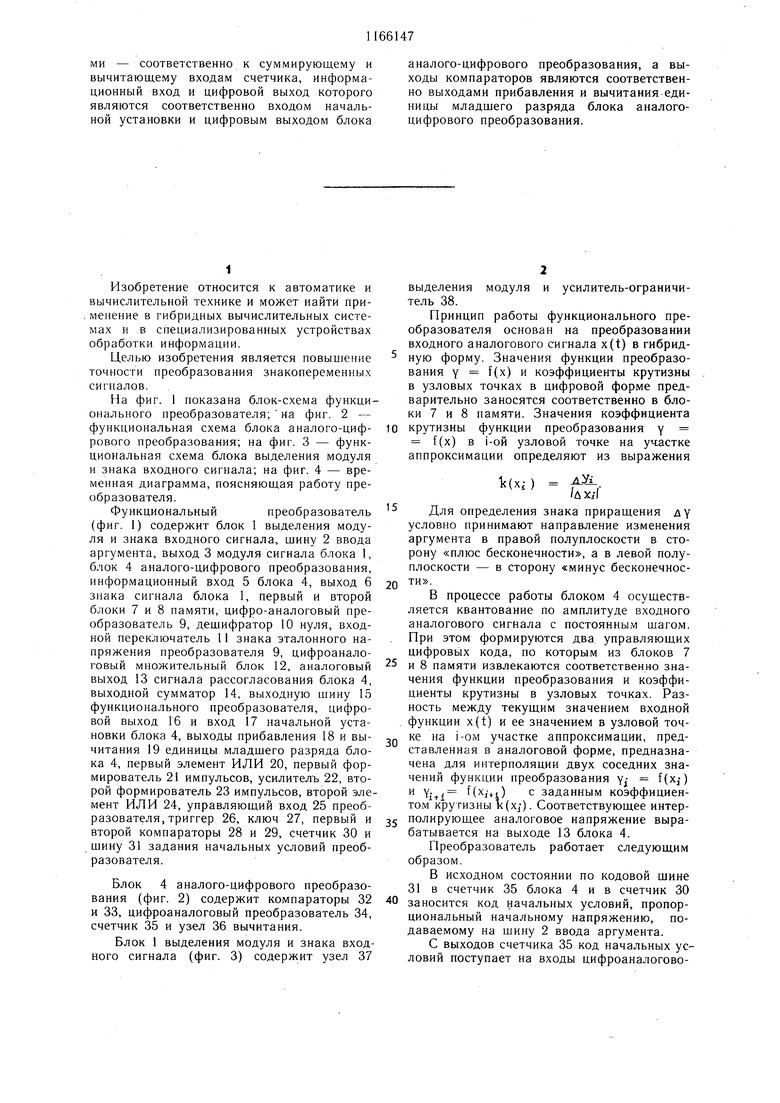

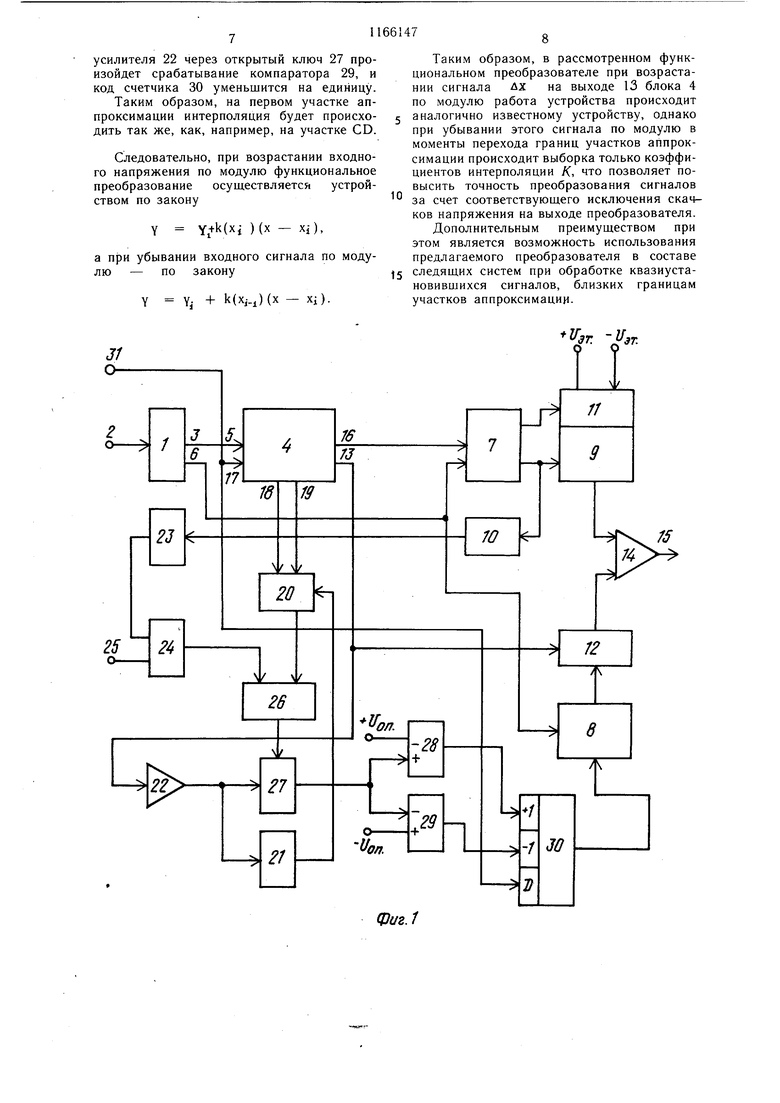

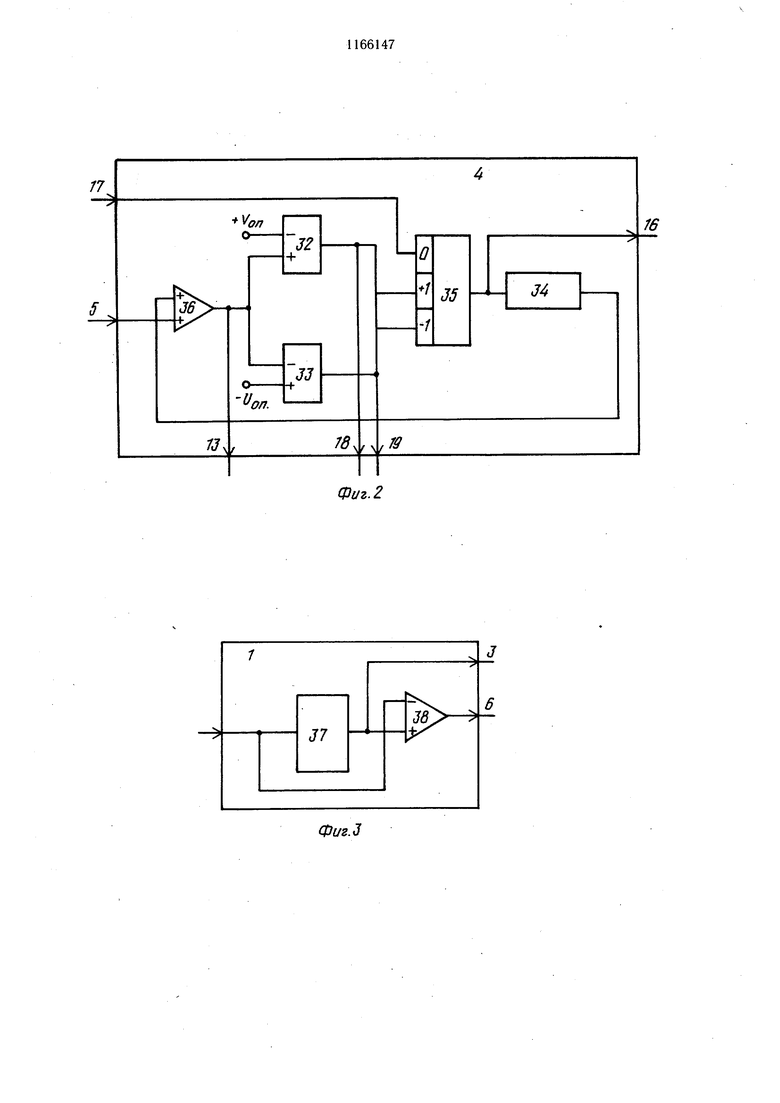

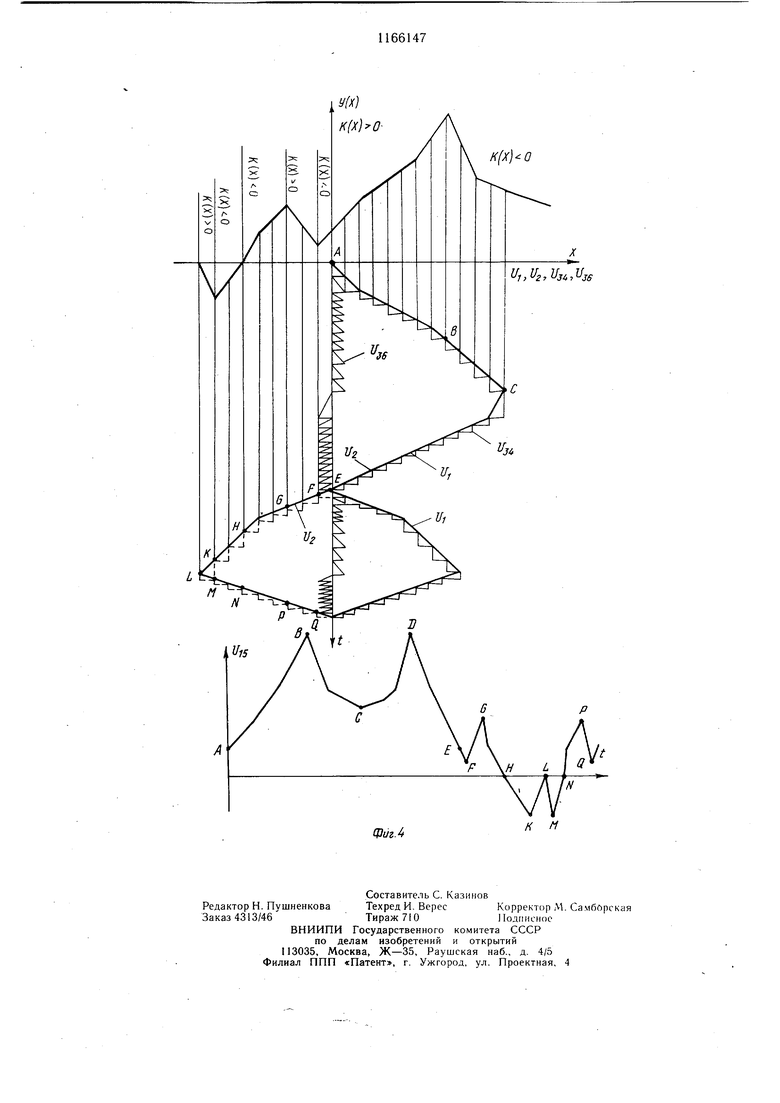

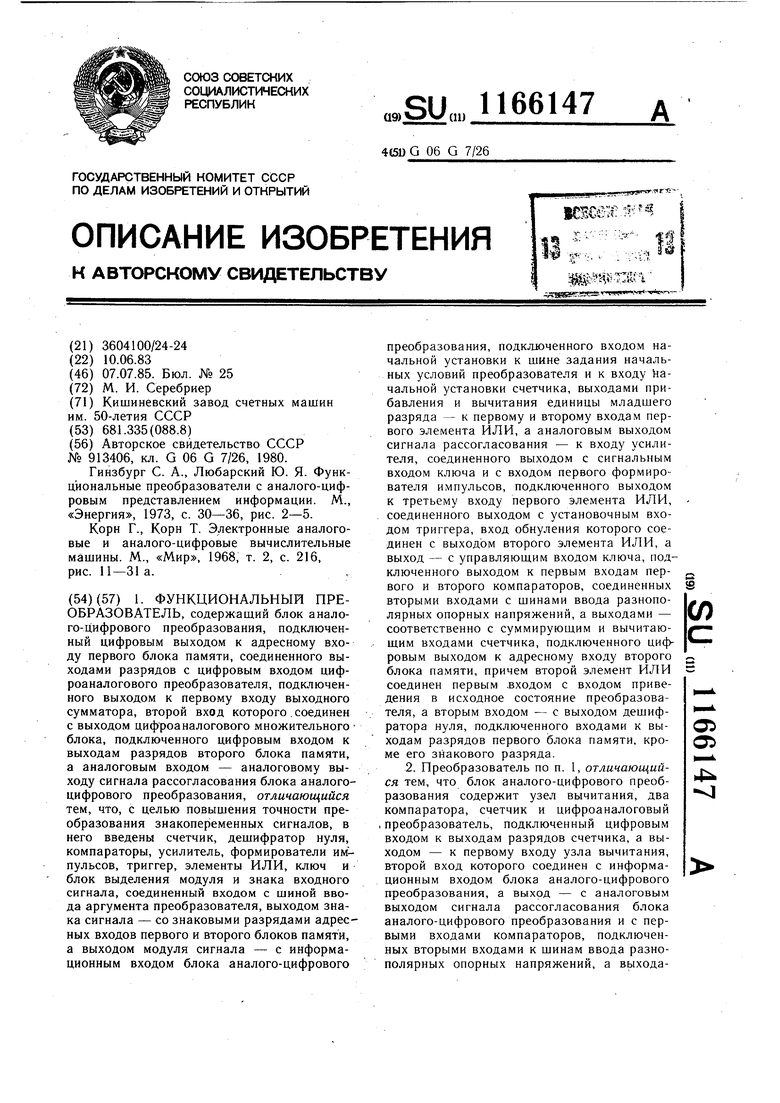

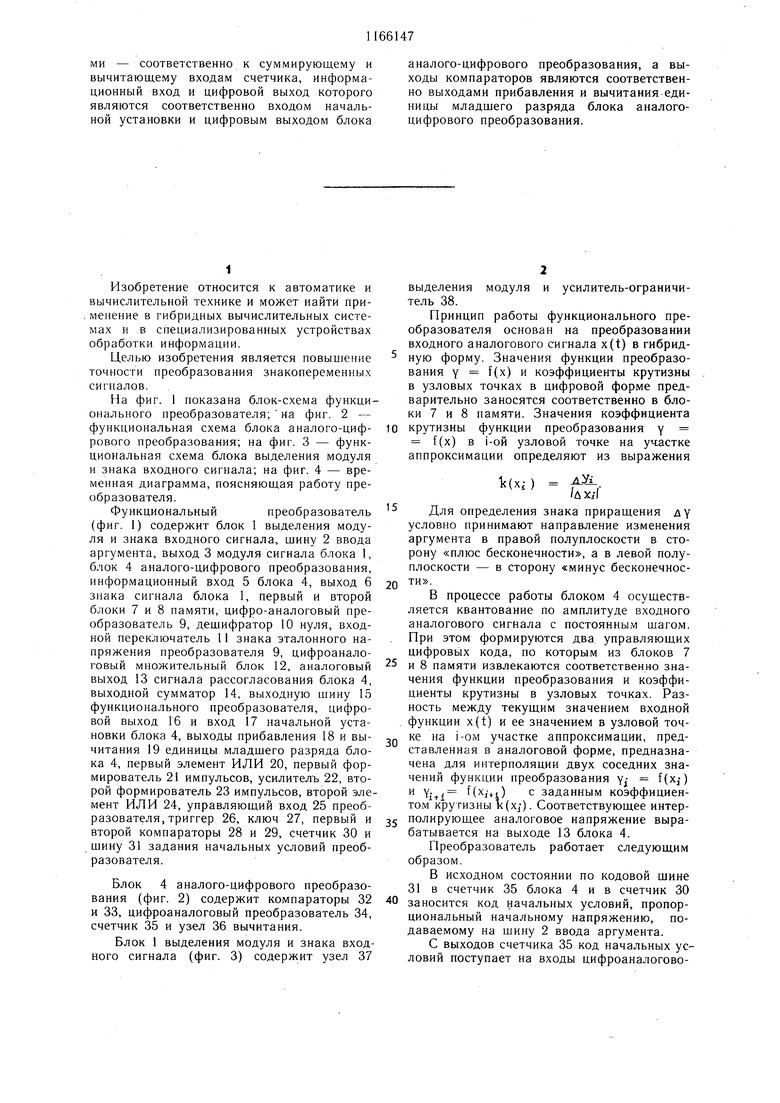

На фиг. 1 показана блок-схема функционального преобразователя; на фиг. 2 - функциональная схема блока аналого-цифрового преобразования; на фиг. 3 - функциональная схема блока выделения модуля и знака входного сигнала; на фиг. 4 - временная диаграмма, поясняющая работу преобразователя.

Функциональныйпреобразователь

(фиг. 1) содержит блок 1 выделения модуля и знака входного сигнала, щину 2 ввода аргумента, выход 3 модуля сигнала блока 1, блок 4 аналого-цифрового преобразования, информационный вход 5 блока 4, выход 6 знака сигнала блока 1, первый и второй блоки 7 и 8 памяти, цифро-аналоговый преобразователь 9, дещифратор 10 нуля, входной переключатель 11 знака эталонного напряжения преобразователя 9, цифроаналоговый множительный блок 12, аналоговый выход 13 сигнала рассогласования блока 4, выходной сумматор 14, выходную щину 15 функционального преобразователя, цифровой выход 16 и вход 17 начальной установки блока 4, выходы прибавления 18 и вычитания 19 единицы младщего разряда блока 4, первый элемент ИЛИ 20, первый формирователь 21 импульсов, усилитель 22, второй формирователь 23 импульсов, второй элемент ИЛИ 24, управляющий вход 25 преобразователя, триггер 26, ключ 27, первый и второй компараторы 28 и 29, счетчик 30 и щину 31 задания начальных условий преобразователя.

Блок 4 аналого-цифрового преобразования (фиг. 2) содержит компараторы 32 и 33, цифроаналоговый преобразователь 34, счетчик 35 и узел 36 вычитания.

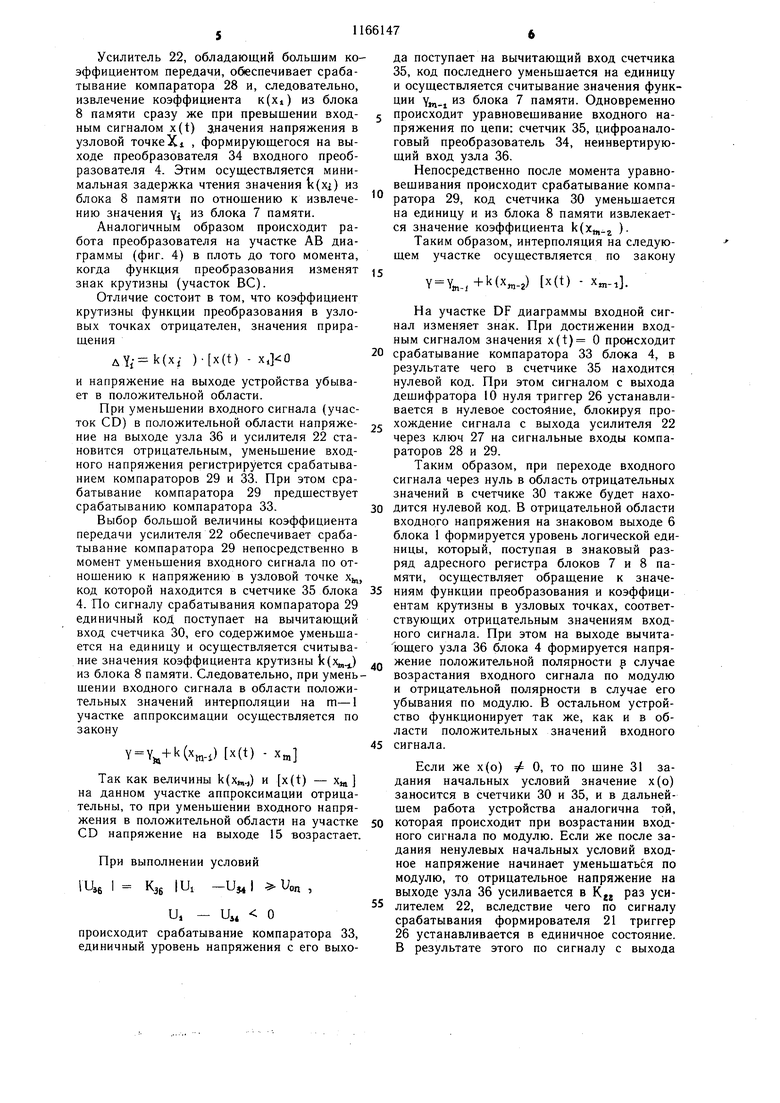

Блок 1 выделения модуля и знака входного сигнала (фиг. 3) содержит узел 37

выделения модуля и усилитель-ограничитель 38.

Принцип работы функционального преобразователя основан на преобразовании входного аналогового сигнала x(t) в гибридную форму. Значения функции преобразования Y ЧХ-) и коэффициенты крутизны в узловых точках в цифровой форме предварительно заносятся соответственно в блоки 7 и 8 памяти. Значения коэффициента

крутизны функции преобразования у f(x) в i-ой узловой точке на участке аппроксимации определяют из выражения

1(Х) .. /Д ХУ1

Для определения знака приращения лу условно принимают направление изменения аргумента в правой полуплоскости в сторону «плюс бесконечности, а в левой полуплоскости - в сторону «минус бесконечнос™ В процессе работы блоком 4 осуществляется квантование по амплитуде входного аналогового сигнала с постоянным щагом. При этом формируются два управляющих цифровых кода, по которым из блоков 7

и 8 памяти извлекаются соответственно значения функции преобразования и коэффициенты крутизны в узловых точках. Разность между текущим значением входной функции x(t) и ее значением в узловой точке на i-OM участке аппроксимации, представленная в аналоговой форме, предназначена для интерполяции двух соседних значений функции преобразования у Цх/) и У, f(xj-ti) с заданным коэффициентом крутизны к(х). Соответствующее интерполирующее аналоговое напряжение вырабатывается на выходе 13 блока 4.

Преобразователь работает следующим образом.

В исходном состоянии по кодовой щине 31 в счетчик 35 блока 4 и в счетчик 30

0 заносится код начальных условий, пропорциональный начальному напряжению, подаваемому на щину 2 ввода аргумента.

С выходов счетчика 35 код начальных условий поступает на входы цифроаналогового преобразователя 34, на выходе которого формируется уравновешивающее аналоговое напряжение, равное входному. По адресу, задаваемому кодом начальных условий с цифрового выхода 16 блока 4, из блока 7 памяти извлекают начальное значение функции преобразования Уо - f(0).

Информация в знаке напряжения, поступающего на шину 2 с выхода 6 блока 1, поступает на вход знакового разряда адреса блоков 7 и 8 памяти. Для воспроизведения напряжения необходимой полярности на выходе 15 устройства знаковый разряд числа блока 7 памяти осуществляет управление переключателем 11 преобразователя 9, который коммутирует к шине питания преобразователя 9 эталонное напряжение соответствующей полярности.

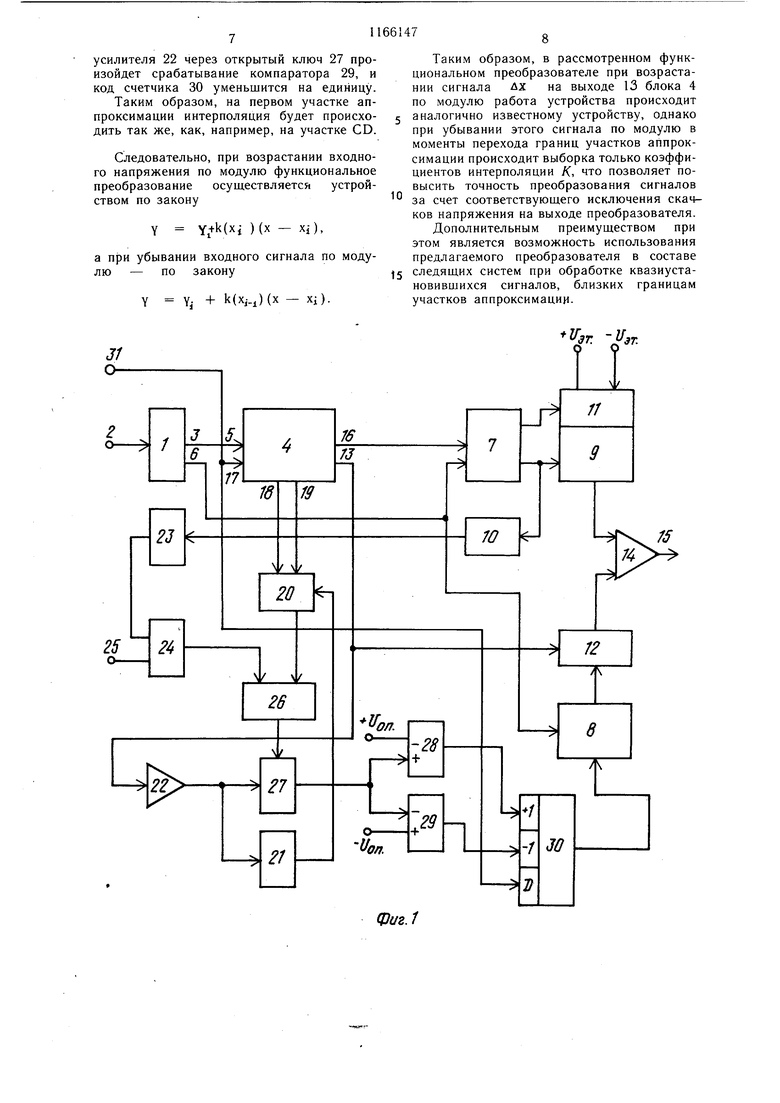

Рассмотрим работу преобразователя при изменении аргумента в области положительных значений, начиная с нулевого значения х(0) О в соответствии с диаграммой (фиг. 4).

При изменении в положительной области входного сигнала напряжение на выходе 3 блока I повторяет входное, вследствие чего напряжение на знаковом выходе 6 блока 1 равно нулю. Этот нулевой потенциал, поступая на вход знакового разряда адресных входов блоков 7 и 8 памяти,осуществляет обращение к адресам, соответствующим положительным значениям входного сигнала. В исходный момент времени счетчики 30 и 35, а также триггер 26 установлены в нулевое состояние импульсным сигналом команды «исходное положение, подаваемым на вход 25, а на входе 5 блока 4 входное напряжение равно уравновешивающему с выхода цифроаналогового преобразователя 35. По нулевым кодам, хранящимся в счетчиках 35 и 30, осуществляется соответственно считывание значения функции преобразования у(о) из блока 7 памяти и значения коэффициента крутизны k(o) на данном участке аппроксимации из блока 8 памяти. Цифровой код значения функции Y(O) поступает на входы преобразователя 9, вследствие чего на выходе 15 преобразователя формируется аналоговое напряжение исходного состояния.

При изменении аргумента в положительной области, на выходе узла 36 вычитания формируется напряжение положительной полярности, равное разности между текущим значением аргумента и его значением в узловой точке. Это напряжение с выхода 13 блока 4 подается на аналоговый вход цифроаналогового множительного блока 12; на цифровые входы которого поступает положительное значение коэффициента из блока 8 памяти.

Следовательно, на выходе 15 происходит воспроизведение первого участка интерполяции по закону

Y Y(O) +k(o) x(t) .

При выполнении условия

и

Кз,-и,

on )

где Кзб коэффициент передачи узла 36; и, -напряжение на выходе 3 блока 1; ± UQ -опорное напряжение на компараторах 28, 29, 32, и 33, происходит срабатывание компаратора 32, при котором напряжена его выходе соответствует уровню логической единицы. По суммирующему входу в счетчик 35 заносится единичный код и осуществляется считывание значения у f(x) из первой ячейки блока 7 памяти.

Единичный уровень с выхода компаратора 32 через элемент ИЛИ 20 установит триггер 26 в единичное состояние. В исходном состоянии триггер 26 был установлен в нулевое состояние сигналом команды «Исходное положение со входа 25, вследствие чего -прохождение сигнала с выхода усилителя 22 на сигнальные входы компараторов 28 и 29 было заблокировано закрытым ключом 27. Этим обеспечивается задержка срабатывания триггера 26, и соответственно, открывание ключа 27 непосредственно по завершению интерполяции на первом участке аппроксимации.

Следовательно, на первом участке аппроксимации интерполяция осуществляется по исходным данным у(о) и k(o).

По единичному коду счетчика 35 блока 4 на выходе цифроаналогового преобразователя 34 формируется уравновешивающее напряжение Uj, равное входному, переводящее компаратор 32 в исходное состояние, и устройство переходит к следующему участку аппроксимации.

При возрастании напряжения на выходе усилителя 22 и выполнении условий

и К,«-Кгг(и. -UM ) оя ,

и, - УЗ. О,

где - коэффициент передачи усилителя 22, произойдет срабатывание компаратора 28. По сигналу срабатывания компаратора 28, поступающего на суммирующий вход счетчика 30, в последний заносится единичный код, по которому осуществляется считывание из блока 8 памяти значения коэффициента крутизны k(xi), т. е. начинается воспроизведение второго участка интерполяции по закону

у у, + k(xj- x(t)- х .

Так как значения у,, k(Xj) и x(t) - xj положительны, то на выходе 15 происходит возрастание положительного напряжения. Усилитель 22, обладающий большим коэффициентом передачи, об1еспечивает срабатывание компаратора 28 и, следовательно, извлечение коэффициента K(XI) из блока 8 памяти сразу же при превышении входным сигналом x(t) значения напряжения в узловой точкеXi , формирующегося на выходе преобразователя 34 входного преобразователя 4. Этим осуществляется минимальная задержка чтения значения k(xi) из блока 8 памяти по отношению к извлечению значения Vi из блока 7 памяти. Аналогичным образом происходит работа преобразователя на участке АВ диаграммы (фиг. 4) в плоть до того момента, когда функция преобразования изменят знак крутизны (участок ВС). Отличие состоит в том, что коэффициент крутизны функции преобразования в узловых точках отрицателен, значения приращенияAY,--k(x,- )(t) - х,0 и напряжение на выходе устройства убывает в положительной области. При уменьшении входного сигнала (участок CD) в положительной области напряжение на выходе узла 36 и усилителя 22 становится отрицательным, уменьшение входного напряжения регистрируется срабатыванием компараторов 29 и 33. При этом срабатывание компаратора 29 предшествует срабатыванию компаратора 33. Выбор большой величины коэффициента передачи усилителя 22 обеспечивает срабатывание компаратора 29 непосредственно в момент уменьшения входного сигнала по отношению к напряжению в узловой точке Xj, код которой находится в счетчике 35 блока 4. По сигналу срабатывания компаратора 29 единичный код поступает на вычитающий вход счетчика 30, его содержимое уменьщается на единицу и осуществляется считывание значения коэффициента крутизны 1(Хв,) из блока 8 памяти. Следовательно, при уменьшении входного сигнала в области положительных значений интерполяции на m-1 участке аппроксимации осуществляется по закону Y (xjn.,) x(t) - х„ Так как величины k(xin.j) и x(t) - х на данном участке аппроксимации отрицательны, то при уменьшении входного напряжения в положительной области на участке CD напряжение на выходе 15 возрастает. При выполнении условий Шб I - Кзб lUi -и„| Uon , и, - Uj4 О происходит срабатывание компаратора 33, единичный уровень напряжения с его выхода поступает на вычитающий вход счетчика 35, код последнего уменьшается на единицу и осуществляется считывание значения функции из блока 7 памяти. Одновременно происходит уравновешивание входного напряжения по цепи; счетчик 35, цифроаналоговый преобразователь 34, неинвертируюший вход узла 36. Непосредственно после момента уравновешивания происходит срабатывание компаратора 29, код счетчика 30 уменьшается на единицу и из блока 8 памяти извлекается значение коэффициента k(Xa,2 ) Таким образом, интерполяция на следующем участке осуществляется по закону Y Ye,j+l(x.2) x(t) - . На участке DF диаграммы входной сигнал изменяет знак. При достижении входным сигналом значения x(t) О происходит срабатывание компаратора 33 блока 4, в результате чего в счетчике 35 находится нулевой код. При этом сигналом с выхода дещифратора 10 нуля триггер 26 устанавливается в нулевое состойние, блокируя прохождение сигнала с выхода усилителя 22 через ключ 27 на сигнальные входы компараторов 28 и 29. Таким образом, при переходе входного сигнала через нуль в область отрицательных значений в счетчике 30 также будет находится нулевой код. В отрицательной области входного напряжения на знаковом выходе 6 блока 1 формируется уровень логической единицы, который, поступая в знаковый разряд адресного регистра блоков 7 и 8 памяти, осуществляет обращение к значениям функции преобразования и коэффициентам крутизны в узловых точках, соответствующих отрицательным значениям входного сигнала. При этом на выходе вычитающего узла 36 блока 4 формируется напряжение положительной полярности р случае возрастания входного сигнала по модулю и отрицательной полярности в случае его убывания по модулю. В остальном устройство функционирует так же, как и в области положительных значений входного сигнала. Если же х(о) О, то по шине 31 задания начальных условий значение х(о) заносится в счетчики 30 и 35, и в дальнейшем работа устройства аналогична той, которая происходит при возрастании входного сигнала по модулю. Если же после задания ненулевых начальных условий входное напряжение начинает уменьшаться по модулю, то отрицательное напряжение на выходе узла 36 усиливается в Kjj раз усилителем 22, вследствие чего по сигналу срабатывания формирователя 21 триггер 26 устанавливается в единичное состояние. В результате этого по сигналу с выхода усилителя 22 через открытый ключ 27 произойдет срабатывание компаратора 29, и код счетчика 30 уменьшится на единицу. Таким образом, на первом участке аппроксимации интерполяция будет происходить так же, как, например, на участке CD. Следовательно, при возрастании входного напряжения по модулю функциональное преобразование осуществляется устройством по закону Y (X( ) (х - xj), а при убывании входного сигнала по модулю - по закону Y Yj + l(Xj-J(x - xi).

фиг.1 Таким образом, в рассмотренном функциональном преобразователе при возрастании сигнала ДХ на выходе 13 блока 4 по модулю работа устройства происходит аналогично известному устройству, однако при убывании этого сигнала по модулю в моменты перехода границ участков аппроксимации происходит выборка только коэффициентов интерполяции /(, что позволяет повысить точность преобразования сигналов за счет соответствующего исключения скачков напряжения на выходе преобразователя. Дополнительным преимуществом при этом является возможность использования предлагаемого преобразователя в составе следящих систем при обработке квазиустановивщихся сигналов, близких границам участков аппроксимации. гОг -иэт.

V/

ол

16

35

78

13

i

Фиг. 2

37

Фиг.З

t/o .X

| Авторское свидетельство СССР № 913406, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гинзбург С | |||

| А., Любарский Ю | |||

| Я | |||

| Функциональные преобразователи с аналого-цифровым представлением информации | |||

| М., «Энергия, 1973, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Корн Г., Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины | |||

| М., «Мир, 1968, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-07-07—Публикация

1983-06-10—Подача