(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1986 |

|

SU1429169A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1278976A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| Оперативное запоминающее устройство | 1978 |

|

SU788173A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Запоминающее устройство | 1979 |

|

SU873276A1 |

| ИЕРАРХИЧЕСКАЯ СИСТЕМА АССОЦИАТИВНОЙ ПАМЯТИ | 1992 |

|

RU2025795C1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310307A1 |

. , I

Изобрете1гае относится к,области запоминающих устройств.

Одно из известных ассоциативиых за- . поминающих устройств (АЗУ) построено в виде матрицы ассоциативной пакяти на отдельных ассоциативных ячейках jiayflTH, непосредственно в которых возможно выполнение операции сравнения i. Это позволяет выполнять операцию сравнения заданных признаков с признаками -всех хранящих ся в устройстве слов одновременно и по всему объему запоминающетч устройства.

В этом устройстве каждое новое CIIOBO поступает на входные шины АЗУ и, в случае отрицательного результата сравнения, записывается в запоминающее устройство по адресу, код которого задан на адресные шины АЗУ от счетчика адреса через дешифратор адреса.

Необходимость собствениой схемы сравнения Ш1Я каждой ячейки памяти приводит к тому, что АЗУ, построенное на отцёй5ьHf.ix ассоциативных $гчейках памяти, имеет больию) объем оборудования,--.л -:-;

Из известных устройств наиболее близКИМ техническим рещёнйем к данному изобретению является ассоциативное запоминающее устройство, содержащее счетчик, выходы которого подключены ко входам до щифратора, а вход - к одному из выходов блока управления и управляющему входу адресного накопителя, и шины опроса 2. Недостатком этого устройства является невысокое быстродействие обусловленное последовательным опросом.

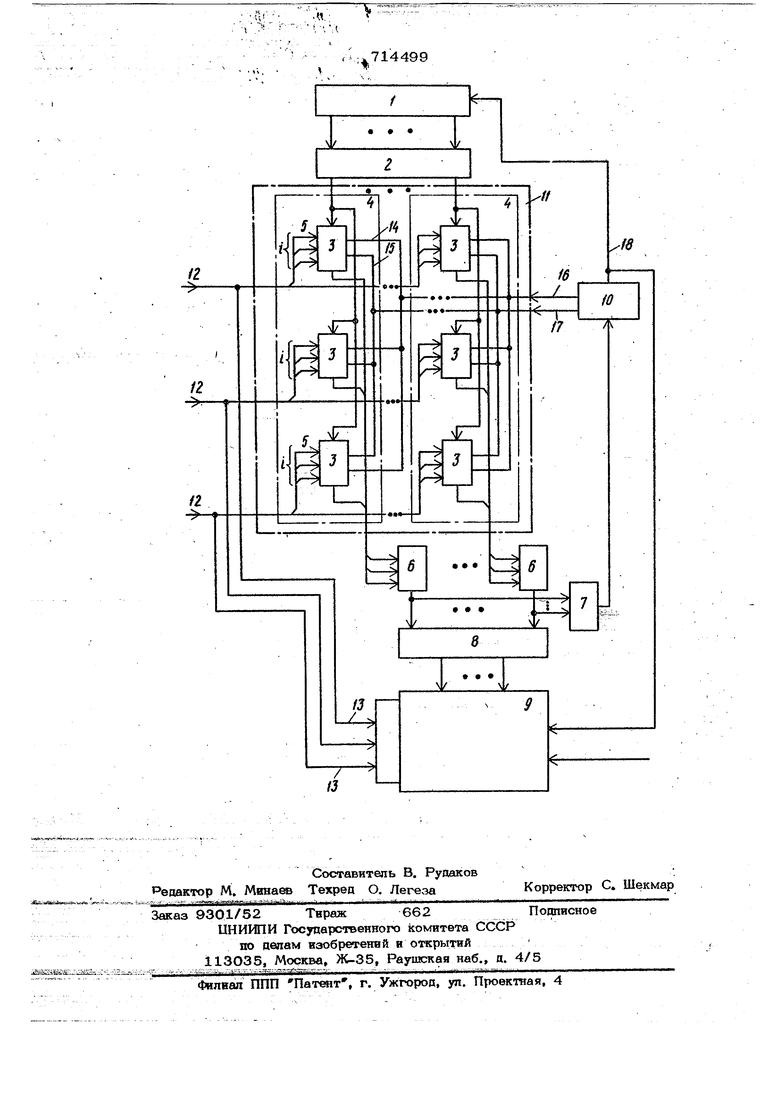

Целью настоящего изобретения является повышение быстродействия устройства. Это достигается тем, что устройство содержит оперативные накопители, шифратор и.элементы И и ИЛИ, причем адресные щины оперативных накопителей одноименных разрядов подключены к шинам опросп, входные шины оперативных накопителей к соответствующим выходам дешифратора, управляющие шины оперативных накопителей соединены с другими шлходами блока управления, а выход. onopaTHBtif.ix накопителей подключены ко входам; соответст1.у - -3 - , элементов И, выиэды которых соеди нены со входами элемента ИЛИ и шифрат)ра, выходы которых пошшючены соответ ственно ко входу блока управления и вко дам аиресногч накопителя,. ( На чертеже изображена блок-схема прещюженного устройства. Устройство содержит счетчяк 1, дешифратор 2, оперативные накопители 3 Ъбъёдйненньге в числовые линейки 4 с адресными итнамй 5, элементы 6 И, элемент 7 ИЛИ, цдафратор 8, адресный нако. ШЕтель 9, блок 10 управления. Числовые лнкейки 4 образуют ассоннативный накопктеяь 11. Адресные iimHbJ S накопителей 3 ймеяиык; разрядов подключены к шинам 12 Шро За ё6язаиньш с шинами 13 нако пителя 9s уарйБЛйвзаий вход которого соедйнея с одаим нз выйоиев блока 10 управлений. Входные яшны накопитшей 3 Шщшгочёны Е соответствующим вьиаэдам дешифратора 2 уяраэпйющие цатны 14 и 15 йаксйштепей 3 соецтаены ;с друГИт га йыходамй бйока 10, BMxom fHdKC nHTenefi 3 01шжб8мейяьтх ЧИСТОВЫХ лйяеек 4 пбйкпйя.е|Ш ко входам соответствующих srte« ментов 6 И, выходы которых соедйнейы со еходамн элемента 7 ИЛИ и иягфратора 8, выходьг которых подключены cooTv. ве члдаекйО ко вхойу блоки управления 10 к входам накопители 9, Устройство работает спейукчцим образом,.; : -„- --- ,; ..:---. .--; В случае ОТС5ГТСУГВЙЯ обращения к асшайатйвному ;запомййающе ;4у устройству чзчетчшс 1 находится в таком состоянии, что формирует через дешифратор 2 ло-гйчеокую 1, йьааваемую на вход оче1 да Ой свобо1шой Линейки 4 ассоциативного накопители 11, выполненной, иапря Titep, на интеграпьиьгх микросхемах типа онератйвного ЗУ с органазашей 3 ойнораэряймых слов Входное fcnuso постуяает на шшы 12 ; и с Н0Х на нданы 13 накопителя 98 на nititbi 5 пчнеек 4 ассоциативио1м накопигеля 11, Шаиь 12 усяовно разделены йа участки по -1 шйи s кАжаом. так;ой у Гйёт6кнбэавнсШоВ й| зЯч годает адрес на сзоОТБётствутощий накопн - тепь 3 каждай пкнейкй 4. Так, первый .участок, вокашчаютий -i первых шин 12, задает p fjpfsea аараллельно на все первые иакопктелк 3 каждой линейки 4 (верхние иа чертеже н г. д Кроме того, при поступлении вховного слова начинает работу Ю ynpaiafti&79 ..4 ния, в котором запускается микропрограмма, действующая в течение цикла обработки одного. вхо дного слова. По команде, сформированной на выхои. де 16 блока 10 управле1тя, происходит опрос всех накопителей 3 ассоциативного накопителя 11, т.е. сравнение признаков происходит по всему объему запоминающего устройства одновременно. Если информация поступила первично то ни в одной линейке 4 не будет такого состояния, чтобы на всех ее выходах были логические I, обозначающие совпадение поступившей информации с.ранее записанной. На всех выходах элементов 6 И будут, поступающие на входы элемента 7 ИЛИ логические О, Ko opBie формируют на ее выходе логический О. По нему блок 10 управления на выходе 17 формирует команду Запнсь, разрешающ5та запись логической 1, поступившей с выхода деишфрачора 2 на вход очередной свободаой лйнейкя 4, в каждый накопитель 3 линейки 4 по адресам, заданным на шинах 12. После записи, произведенной в оперативные накопители 3 ассоциативного накопителя : 11, с выхода 16 блока 10 управления снова поступает команда опроса иопрайягоает линейки 4 :по тем же адресам, в результате чего на всех выходах линейки 4, куда была произведена запись, появятся логические 1, поступающие йа входы соответствующего элемента 6 И. На выходе этого элемента формируеТся логическая 1, которая одновременно с логическими с выходов остальных элементов 6 И поступает на входы ши4ч атора 8 и формирует на его выходах поступающий на адресные входы накопителя 9 код адреса, по которому должна быть записана входная информация в накопитель 9. К мрмейту установки кода адреса на . адресных входах .накопителя 9 блок 10 управления формирует на выходе 18 команду, по которой происходит запись входной информации в накопитель 9. По этой зке команде с выхода 18 производится сдвиг счетчика 1 на единицу с целью подготовки очередной свободной линейки 4 ассоциативного накопителя 11 к приходу новой входной информации. При повторном поступлении входной информации в результате опроса ассоциативного накопителя 11 но адресам, заданным входной информацией, на всех выходах ли- . нейкй 4, куна ранее была записана эта информация, появляются логические I формир5гющие 1 на выходе соответствующего элемента 6 И. Эта I поступает на вход элемента 7 ИЛИ и приводит к появлению логической 1 на его выходе, которая поступает на вход блока 10 управ ления и запрётдает формирование комйнй г Запись в накопители 9 и 11 и запрет сдаига счетчика 1. Кроме того, уровень логической 1 на выходе одного элемента 6 Ни уров-. ни логических О ва выходах остальяых элементов б И поступают на шифратор 8 и формируют на ei выходе кой айреса, по которому была записана входная ниформация, что дает, при необходимости, возможность ее считываний при подаче команды считывания на накопитель 9. Параллельный опрос яозволя:ет cjmieci венно увеличить быстродействие АЗУ по сравнению с «рототийом. Кроме того, описанное устройство позволяет уменьшить йотреблвемую мощность за счет исагользовавдя огЕбратйвных запоминающих устройсте, построенных иЕа транзисторах и вьшускае мых промыаиевностью в интегральном исполнении, в то время, как в прототипе используются фер ритовые сердечники, работающие с больши ми токами перёмагннчивания. Формула изобретен а я Ассоциативное заломинающее устрой тво, содержащее счетчик, выходь ,996 го подключены ко входам дешифратора, а вход к одному из выходов блока управления и управляющему входу адресного накопителя, и шины опроса, отличию щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит оперативные накопители, шифратор и элементы Ни ИЛИ, причем адребные шины оперативных накопителей одноименных разрядов подключены к шинам опроса, входные шины оперативных накопителей - к сортветствукштм выходам дешифратора, управляюягае 11шны оперативных накопителей соединены с другими выходами блока управления, а выходы оперативных накопителей подключены ко входам соответствующих гшёментов И, выходы которых соединены со входами элемента ИЛИ и шифратора, выходы которых подашючейы соответственно ко входу бло-, ка управления и входам адресного накоmrens, ( . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 513393, ки. G-li С 15/00, 09.08,73/ 2. Ли Си Кен, Проектирование и применение постойнных ассоциативных за- f поминающих устройств, серия Приборы В устройства радиоэлектронной техники : :и автоматики . Л,, 1972 с, 3-10 (про-, тотнп.

. ; 714499

Авторы

Даты

1980-02-05—Публикация

1977-05-19—Подача