I

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство, содержащее дешифратор, связанный с адресным регистром, регистр адресов отказов, триггеры перекоммутации цепей и элементы И . Принцип работы устройства заключается в том, что фиксируют адрес отказавшей группы ячеек, сравнивают текущий адрес программы с адресом отказавшей группы ячеек и при их совпадении производят обращение по адресу, код которого получают сложением по модулю два кодов адресов программы и обратного кода адреса отказавшей группы ячеек.

Недостаток этого устройства заключается в том, что уже при единственном отказе группа ячеек, код адреса которой 111...11, становится резервной, т. е. эффективная емкость запоминающего устройства значительно падает. В случае же отказа ячейки, находящейся внутри группы, и модификации ее адреса может произойти потеря ранее записанной информации в ячейке, теперь работающей на подмену. Кроме того, если количество отказавших ячеек больше числа

в группе 111... 11, то это приводит к полному отказу.

Наиболее близким техническим решением к данному изобретению является запоминающее устройство с самоконтролем, содержащее адресный накопитель, подключенный к дешифратору, ассоциативный накопитель, шифратор и входной регистр, соединенные с блоком управления, и счетчик дефектны.х ячеек памяти 2.

Недостатком этого устройства является низкое быстродействие, обусловленное необходимостью многократного суммирования. Действутельно, в случае наличия в адресном накопителе массива последовательно расположенных неисправных ячеек памяти, требуется последовательное формирование и перебор их адресов, с целью определения адреса очередной исправной, ячейки памяти, допускающей к себе обращение (механизмом этого и является многократное суммирование) .

Целью настоящего изобретения является

повышение быстродействия запоминаюп1,его устройства.

Указанная цель достигается тем, что устройство содержит регистр обращений, пре ;орач(,.;; чодо. лиммутаГИ) ;i Ъ|Л;.:ч;;н Г;,: J и HJiti. iipH4C;v; пходы комм /тато);| пол. ключеиь; r():; :u44--riv:iiHO х оь лолад/ с ,тчи1-;;; Л фскгП 11х п; :-Ол и;-мнтг, )лО,.1.:и)1 и ;;;Г: -|-;);1 );;|.1(Л1::;; и viiiOMV и;: ыхслои сИЧпi:l:;;Ti.(H4) П Л Я. ;i :Я,1ЧО..,;,:;.; ::i П1;ТС.ЛЯ, уЛ)МВЛ5 {;п1||и Ki)lOj) СлеЛЛMCii с выходол Xi.ieveiiTa И уп 1авл;|10 иим входом респстра обращений, другие пыходы ассоциативпогл) лакопителя г.од.к.гю ид1Ы к икгЬормациокным входям регистпа оппап:, и пл.-им ixi ( 11ре(.бр;)ао1 ;гг;;дя , другие у;ходы кг)Т( соедил1: 1,1 с выходалЛ- ;)е;лсг()а обращений, ьыходь :рсо6рс ;к;л;;тедя колоч Г1ол,х.л очснь; к р.хс.дам шифратора, выходы KOiopoi-o спедипепь

с ОДНИМ; ЛЗ ВХОЛ.О г1Лел ОЛГО| 1ЛИ. ЧРУ-ЛР

входы котор лх iiojuaiiOLipiibi к ; ыхода:л входHOio регистра, а выхо.аь- - -. вxoдa ; /ieiai-ubрятора, яхопь; элемента Н :од| д1оче:1ы к

иямят п блока vnr;aR;:eHi:s:.

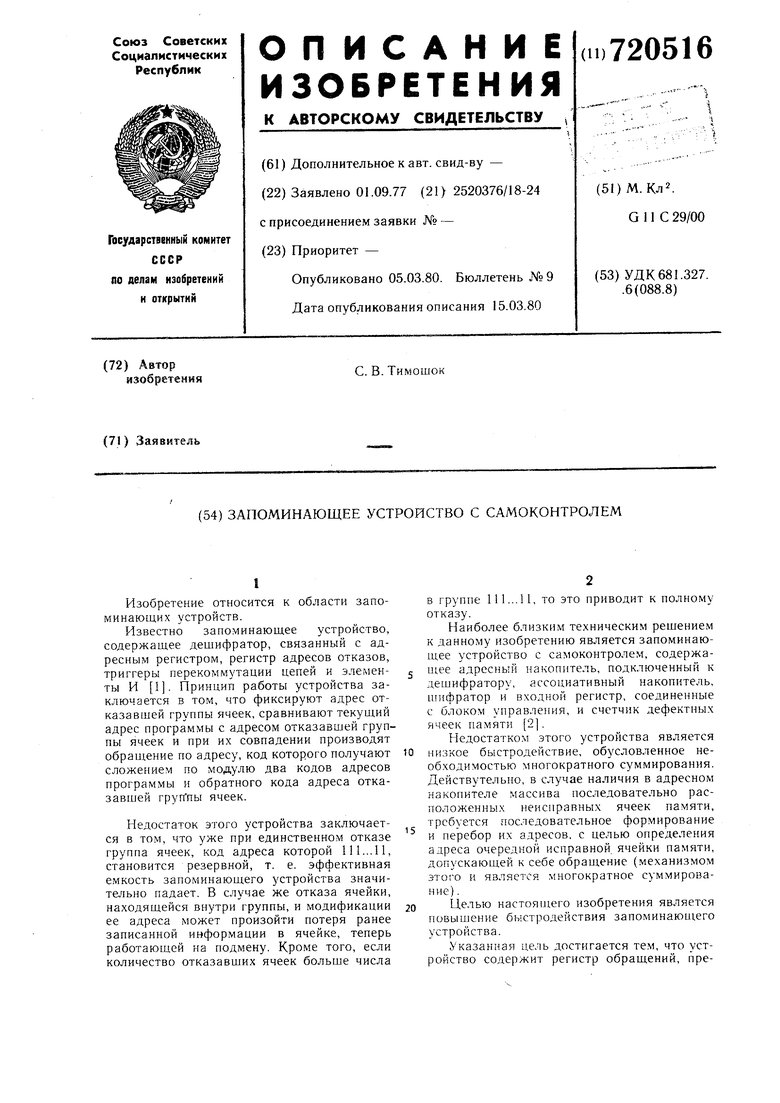

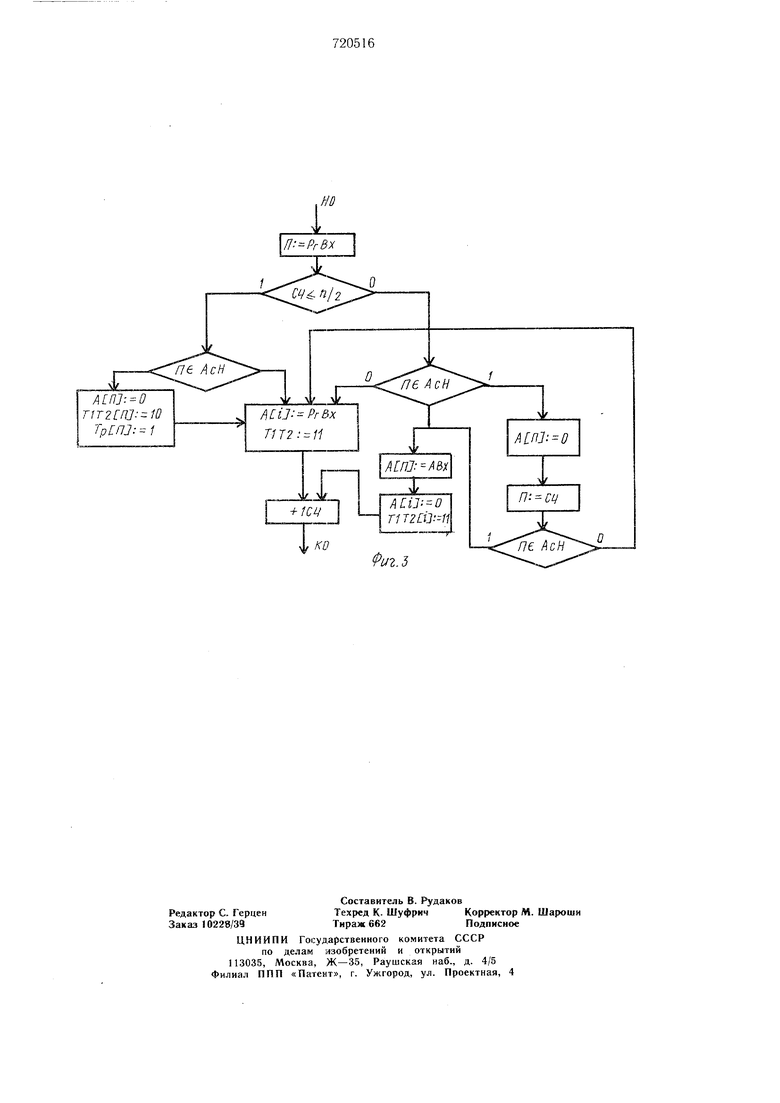

На (риг. j нрпвсде1:а ;:тг:улстуркаи cxevia нреддюжснного устройетна; на фих И одна иа воз 1ожль Х exeiv: ком 1утато;)а; па фнг. 3 -- ал -оритм эабо -ы устройетва н iieжиме адантйл):.

Уетройет 5о еодегдкит зесоциатишад наконите.мь , адрееный лакогнггедь 2. л;1ок И у: раилспия, комл утатор 4, входл ой per иетп 5 ллдиисрратор (;, sJievieiiTib ИЛИ 7, регистр о обраи1,сдЛ1Й, лрсобразоватедв 9 ксаизв. лиаЗ ратор К), счетчик 11 дефектных ячеек п :-:;лел1е т М 12.

Х()Д|, i;() (.|)а 4 чол.ключен,: еоогнегс воиио к вь ходам ечегчика И. neiiOTfu 5, блока 3 я ола: ;.av иа 0)холов имкоп;; -|я fi ahixOyuji ----- к а л(Ьо:)малл;ои1-и-.М аходам иаколлтед , улравдуаоший хат которого соедииен с выходол: элемента 11 12 и уи)а15ляюа1и VS входом ixaaieTpa 8. ;apvaa-ie В1.1ХОДЫ лаконитедя I иодкдктчены к лнсюрмацио11Н1)1м входам рслактра rS и од: им лв входов ирсобг)аз(,ли 9 ко;,ов, Д)угла входы которого coeaTiFiein е выхолоди DO Л1Стра о. Вр 1ходы нрсобразоватедя Э кодоа 1н:)дключены к входам :лифратора 10, выхс;ды которого ео;дт ие; Ы е одиими иа ах;)дов эдел:ентов ИЛИ 7, друаие ходы KOTOpbix ;кллк:1ючень к В1)1ходах peiiseTDa 5, а вы холь; к входам де1НИ()ратора 6. Входы эдемоита И 12 1и)дкд10чены к .здпнм и: вход,ов счотч -;ка 1 1 и блока 3.

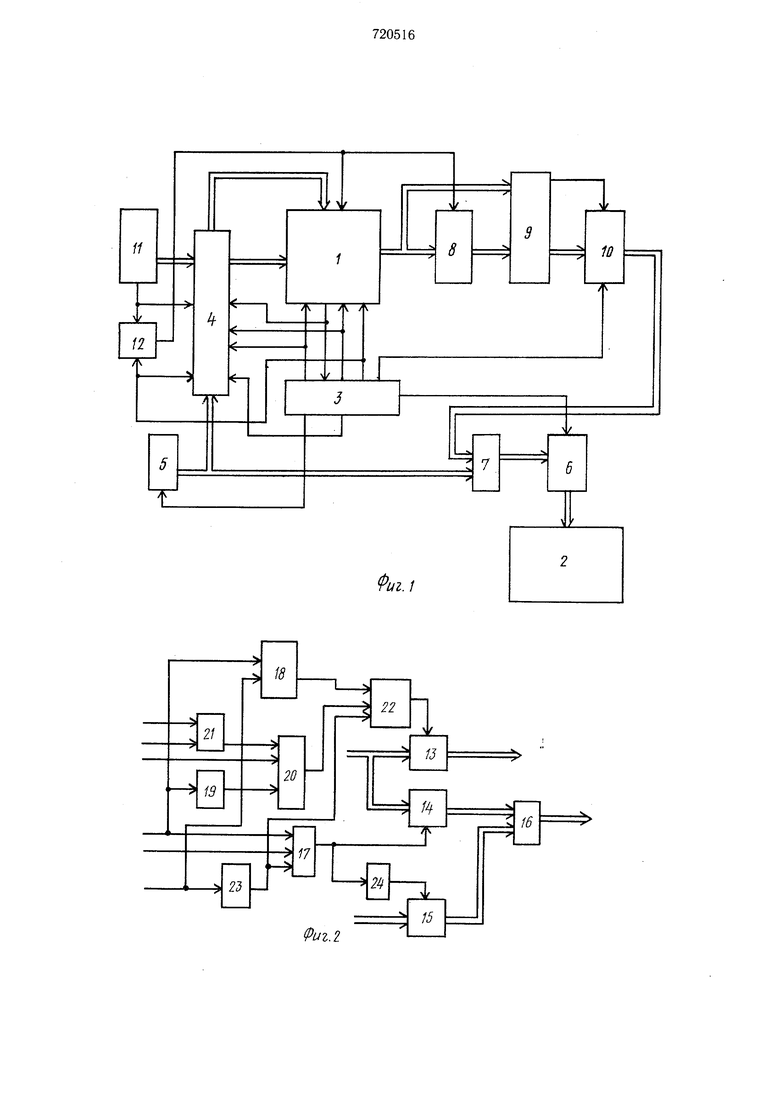

Коммутатор 4 сод.ержит з.теиепты ti 13 15, эдемснтв ИЛИ 16 а 17, ,1ем(Л1т И ; элемент ИН 19, элемент И 2(а трл: гер 21, элемент ИЛИ-НЕ 22, фооуиповатедь 23 имнудьсо и эде ;е11Т Не 24.

Заионика10И1,ее удгройетво ; аботоег ::.i дующим образом.

В начальном соето51лни к ячейки ассоциативного накопителя иослслова-едаио записаны адреса ячстк адресис;го на1 они|-едя 2 от п/2 до л (п число ячеек адрес1И)-о наконитедя 2), в с клчнк Н занисан ко;;

Д(еда п, |рн1ге)Ь) регистра обрагнсник, кажд|-,л лз 1 отг;ри1х иоста1;,тси в соответствие одаои из ячеек ассоииатл-;вио1 о накопителя 1. vcTaiiOB. iciib: is нулевое еоегояние (цени гачал1)Ной тaчoвки уед()Вно ле показаны). ;и:еониат лли ||; чако1иг1Ч :И) работает п л-ух режимах за1Д1еи. 1 иервом режиме гЯ)б):|)аете ячейка а с со и,дативного на копите.тя 1, содержимое которой сов гадает с |р)изнак)м иа -eixi Bxo;i.ax (таки.м призиако.м яв..:1яслч:я а.т1)сс ячейю: адресло о iaкoлитeдя 2). Во BTi.MTo.M выбирается очере.алая свобод.иая ячейка асд:о1и-1а Д1вного , 1. Онредедение занятости ячейки асссмдативного 1 акогд)те:1я 11г.рокзводится i;o ладичию единиц в вспомогательных триггерах Т1 и Т2 (не исжазанв) этой ячейки (в иеходиом еоетоялии |i:irj-epT, Ti ... 79 iicex ческ обиулякп я;. У-с;- i .-обсуччых ячеек П :о1 3г;од1 ея i ерзоиачадь;г:} до с(.:хл н/2. а затер.: но СОТ;..ИИИ10 1рИ геров Т , О л ..О ячейки п/-. Таким обпазоло с.тсмза ji а(.с;л1иа гч;лан .: акол:-:; 1 а Де еле.з дони1Й

а,:рес: Т I 2;(а i

( rioMOHUio K.iMT)OJHar.OH л;х и,.Л каким-дпбо ло лч-1х; еноеобол; оисёдсдхетея

лз клеек ассои.иат;зиозо |д;: 1питедя I з еоотвечствии с а;ггоиитм;1М. ноказаиидм я фк1 3, где li - физиак в.-дк)р;Д1 из ассоциативного лака;л-:те,д i (a.Tjiec РЧСЙКИ адpe aajro на; оците..1я 2;, ;ЧЛ| -- я л-ика аес:;;цла 1Д-1Н -д)г ) лaкoиигfx.я 1, . ио дпизлаку ;Д Apj с..:чередааз e;i;)6a.M-a;: аесодаатизиогч; гакоиитедч ; н 72 |п| -TpBiaCBb залятч)сти ячейки с .1 гл р 1Д Д);-ла-ср регистра В об ал1епия (но доказал, (Ч)ОП:;етст У1О1иий ячейке ( Д;изнаКОУ1 и. Т и Т2 i iтдаглд), зааязаст;;

одегтедиой свобо.тдой .

О еоотзепзггвми с -л и м а: 1-оритмом ара гд1изиаку ассои.ла ааконители ; ие|)воиала. )|Г:че:запва::Л ея :д:а1н,;аи€ пходтюгл) рег1-;с ра о. К сЛли-кз -е.т1 ii счетчике h занисаа ио.а бодынии. п/2 1в этом е.зуиае да вь;хс1тс прлгудгчхет

логический иудз;, и, ее..г; ix-Ci дргза.ак есть в ассо атизио 1 -1ако -и ге.ме д то на лкдгс; лризи;|; а залие);за1стся аудч. юиггеп залято.-ти ТI этой ячсй;д .Зт;-а1азд1;ваетс5: а еост(яиие 1, (рнггср Т2 - а cocioai- e 0. триггер пегиетра 8 обпаи1длд а -- :i сосД) 1. оатем сер(;дной свободиой я1ДЙ1 е ариспаапастс ; зиаччл-н-е вхоД|Д;го оегле д а 5. а (Д: Tpiirreijb занятг е-; л Т1 и 12 /crajiaB/кялое П -/MeaBaiae гея иа единг1Ч. (л(сде.чнис дсе оисдации .;. 1 1 иоуся также ii в том сдучае, когда ир-;зиак 0|с г;лз-а,ет ; аееоа.лативиом накоиаГе д- i В ,

iFiv; -:;V циативном накопителе 1, то на месте признака записываются нули, затем признаку присваивается значение счетчика 11 и, если новый признак отсутствует в ассоциативном накопителе 1, то очередной свободной ячейке присваивается значение входного регистра 5, а ее триггерам занятости Т и Т2 - значение 1; после этого состояние счетчика И уменьшается на единицу. Последние две операции выполняются также в случае отсутствия старого признака в ассоциативном накопителе 1. Если же ячейка, в которой записан код, равный текуш,ему коду счетчика 11, есть в ассоциативном накопителе I, то ей присваивается значение входного регистра 5, триггерам Т1 и Т2 - значение 1, а содержимое счетчика уменьшается на единицу. (Эта цепь не показана). Таким образом, если содержимое счетчика И равно точно п/2, то в ассоциативном накопителе I встречаются слова двух видов: адрес .1 1 и(Ь) 00...OJ 1 (с) При пояр.лелии очередного отказа в ячейках адресного накопителя 2 (содержимое счетчика 11 становится меньшим, чем п/2) ячейки ассоциативного накопителя 1, содержащие слова вида (с), считаются свободными и в них записываются адреса очередных отказавших ячеек. При этом слова вида (с) преобразуются в слова вида (Ь). Если количество отказов станет равным количеству ячеек в адресном накопителе 2, все триггеры Т1 и Т2 оказываются установленными в состояние 1, а в левых частях слов вида (а) оказываются записанными адреса или нули (обращение к ячейке с нулевым адресом считаем запрещенным). Дальнейшая адаптация становится невозможной и наступает отказ заноминаюндего устройства. Запись единицы в триггер Т2 осуществляется только во втором режиме. В перво.м режиме триггер 2 блокируется нулевы.м сигналом с выхода элемента И 12, поступающим на вход маскирования ассоциативного накопителя I, или обнуляется, если этот сигнал равен логической единице. Этим же сигналом разреп ается установка в сотояние СОО1 ветствуюшего триггера регистра 8 обращения, В,бираемого по наличию логической ,ы на отвечающем ему выходе ассоциативного накопителя 1. Наличие едини 1ы н трип-ере регистра 8 обращения свидетельствует о том, что эта ячейка ассоциативного .накопителя I используется при количестве отказов большем, чем п,2, т. е. это является признаком того, что адаптация производится уже не за счет ячеек «старшей а за счет ячеек «младшей половины адресного накопителя 2 («старшая половина содержит ячейки от п/2 до п, «млад,шая - от i до Г1/2 - i ). Следовательно, л,ля адаптации используются последовательно старшие ячейки адресного накопителя 2, причем, в процессе работы могут происходить отказы ячеек в произвольной последовательности и отказ устройства наступает только в случае выхода из строя всех его п ячеек. Таким образом, работа устройства при адаптации отличается когда количество отказавших ячеек не превьпиает п/2 и когда число отказавших ячеек больше п/2. В первом случае ячейка ассоциативного накопителя I, содержащая адрес неисправной ячейки адресного накопителя, обнуляется, и этот адрес записывается в очередную свободную ячейку, определяемую в соответствии с вышеизложенным; на место адреса исправной ячейки адресного накопителя 2. Во втором случае «старшая половина адресного накопителя 2 оказывается заполненной адаптируемой информацией и дальнейшая адаптация производится за счет «младшей половины запоминаюп.1его устройства. При этом ячейка ассоциативного накопите.1н 1, содержащая адрес неисправной ячейки, обнуляется, и этот адрес записывается или в ячейку ассоциативного накопителя 1, содержащую текущий адрес «м,1аднаконителяшеи половины адресного счетчику 1I). (этот адрес определяется по ячейку ассопли в очередпую свободную содержащую нули циативного накопителя в адресной части. Работа устройства осуществляется под воздействием управляющих сигналов, вырабатывае.мых блоком 3 управления. При фиксации факта отказа ячейк.и памяти с выхода б.,тока 3 правления выдается сигнал на входной регистр 5, под воздействием которого адрес отказавшей ячейки поступает на входы элементов ИЛИ 7 и на входы коммутатора 4. Ком.мутатор 4 предназначен для подключения выходов счетчика I 1 или входного регистра 5 к признаковым входам ассоЦ 1ативного накопителя 1, и для подключения вы -одов регистра 5 к инфор ационным входам ассоциат1 вного накопителя 1 в соответствии с а.-1го 111тмом, показанным на фиг. 3 Зптем блок 3 управления - последовательно выдает сигнал записи по первому ког(1рый поступает на входы ассоциативного накопителя 1, коммутатора 4 и на вход э.чемеата И 2, с которого зате.м выдается сотPOiCiHx 1ои1ий сигнал на вход маскироняния ассоциативпого накопптеля 1 и вход разрсысипя зап;1си в регистр 8 обрандения. По си гнал П1)оисх0л1ит запись на :G адреса, пр 1сутствуюп1,его па признакоВлодах ассоциативного накопителя . ор.маци.и с его информационных входов, л;, чае отсутствия такого адреса в ассогнвном накопителе 1 с его выхода на ibi коммутатора 4 и на вход блока 3 управления выдается соответствующий сигFio сигналу заиисп. соответстБуюи ел;} рому режиму, .троисходит запись в очере, сБободн 10 ячейку информаци;1 с инормационных входов ассоциативного наопителя 1.

Об око1 чаиии режима адаптации свидетельствует сигнал, поступающий с выхода блок 3 yiipafjjiOHHfl ма вход коммутатора 4. При обращении к адресному накопителю 2 запрашипаемый адрес поступает на входной регистр 5. ( блока управления 3 выдается сигнал, который разрешает поступление это1п адреса на входы элементов ИЛИ 7 и входы коммутатора 4. Затем с блока 3 управления выдается сигнал опроса, который поступает на вход ассоциативного накопителя : К па вход коммутатора 4, вследствие чего зипрашиваеный адрес с коммутатора 4 поcivriaer па Е1ризнаковыс входы ассоциативного накопителя 1. Если запрашиваемый адрес отсутствует в ассоциативном накопителе L то с управляюпгего выхода его выдается :сигнал, по которому блок 3 управления разрешает декодирование деншфратором 6 кода входного регистра 5 и производит выборку ячейки по запрашиваемому адресу из :,дресиого нако1п-ггеля 2. Если занрашиваемый адр|ес записан в ассоциативном накопителе 1 то возбуждается соогветствую1п,ий его выход а с управляющего выхода накопителя 1 сигнал ие выдается. Тогда блок 3 управления занрепгйет выдачу кода с входного регист; ра 5. Логическая единица с возбужденного выхода накопителя 1 поступает на преобразователь 9. Преобразователь 9 представляет сгюой гфостейцзий шифратор, преобразую ций унитар( входной код в количестве возбужденных выходов. В случае обращения к ячейке асссциативного накопителя I, ригrfp регистра 8 обращения которой усгановлон в состояние i. с выхода преобразователя 9 выдается логический ноль, в противном с.тучае логическая единии,а, которые поступают ма вход шифратора 10. Шифратор 10 преобразует количество логических е,1ипиц -на возбужденных 1нимах преобразо:вателя 9 в обратный дзоичг ый код, к которому в качестве старшего разряда добавляется единица или ноль (адреса ячеек«старшей и «младигей половин запоминающего устройсчва от.личаются наличие 4 единицы илг; нуля в старшем разряде).

После формирования шифратором 10 ад.аптированного адреса адресного накопите .ля- 2, б.лок 3 управ.гения выдает сигпал, который разре1нает прохождение кода адреса через элементы ИЛИ 7 на входы деши(Ьратора 6. Де1пифратор 6 па сигналу с 6jjoK a 3

унразления производит выборку ячейки по сформированному адресу из адресного накопителя 2.

Описанное устройство может найти применение в вычислительной технике при построении надежной памяти больщой емкости. Применение такого устройства позволяет повысить быстродействие запоминающего устройства, упростить автоматическую адаптацию устройства к возникающим в процессе работы отказам.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее адресный накопитель, подключенный к дещифратбру, ассоциативный наконитель, шифратор и входной регистр, соединенные с блоком управления, счетчик дефектных ячеек па.мяти, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит регистр обраш,ений, преобразователь кодов, коммутатор и элементы И и ИЛИ, приче.м входы коммутатора подключены соответственно к выхода.м счетчика дефектных ячеек памяти, входного регистра, блока управления и одному из выходов ассоциативного накопителя, а выходы - к информационным входа.м ассоциативного накопителя, управляющий вход которого соединен с выходом эле.мента И и управляющим входом регистра обращений, другие выходы ассоциативного накопителя годключены к информационны.м входам регистра обращений и одним из входов преобразователя кодов, другие входы которого соединены с выходами регистра обращений, выходы преобразователя кодов подключены к входа.м шифратора, выходы которого соединены с одними из входов элементов ИЛИ, другие входы которых подключены к выходам входного регистра, а выходы - к входам дешифратора, входы элемента И гюд О1Ючены к одни.м из выходов счетчика дефектных ячеек памяти и блока управления. Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР Ло 1900Э7, кл. G 11 С 7/00, 19&5.

2.у вторсхое свидетельство СССР

№ 332498, кл. G П С 15/00, 1970 (прототип).

иг.1 0 П Т 2 : 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU477463A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО^ei^- | 1972 |

|

SU332498A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

Авторы

Даты

1980-03-05—Публикация

1977-09-01—Подача