Изобретение относится к импульсной технике, в частности к устройствам с двумя устойчивыми состояниями.

Цель изобретения - уменьшение потребляемой мощности, повышение быстродействия и уменьшение занимаемой площади при реализации на кристалле.

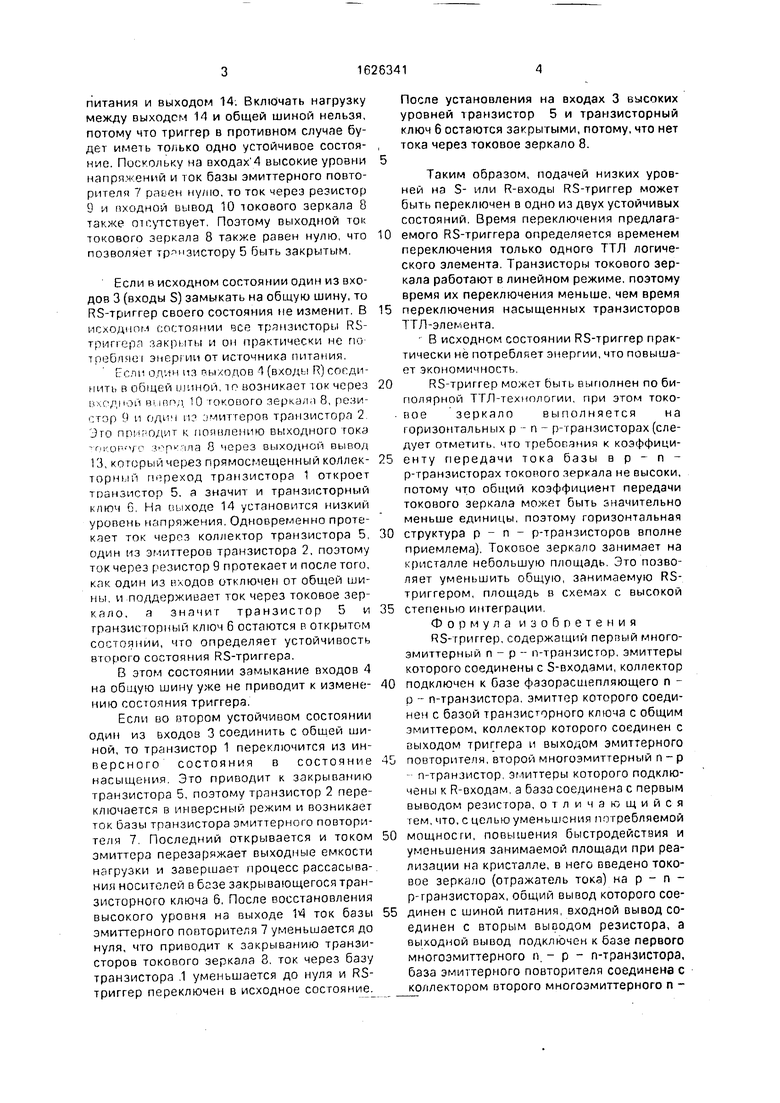

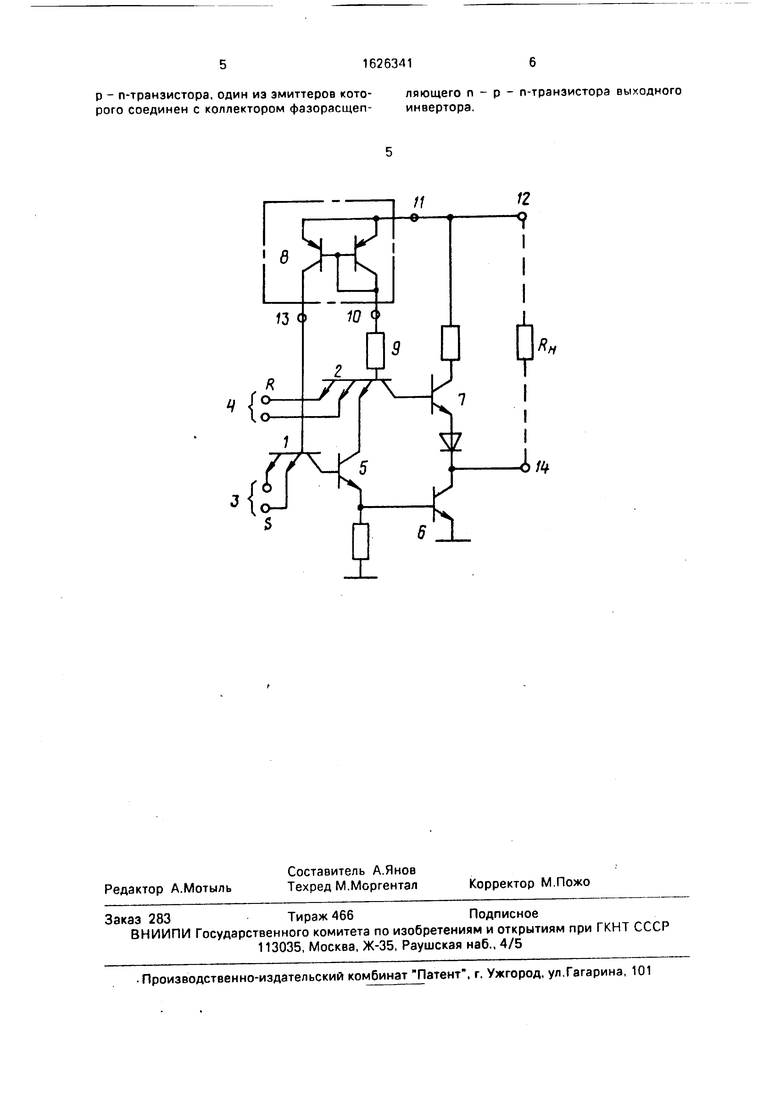

На чертеже приведена принципиальная электрическая схема RS-триггера

RS-триггер содержит первый и второй многоэмиттерные п - р - п-транзисторы 1,2, эмиттеры которых соединены соответстве- но с S-входами З и R-входами 4, фазорас- щепляющий п - р - п-транзистор 5, ключ с общим эмиттером 6 и эмиттерный повторитель 7 на п - р - n-транзисторе, токовое зеркало 8 на р-п- р-транзисторах, коллектор транзистора 6 соединен с одним из эмиттеров транзистора 2, коллектор которого соединен с базой транзистора 7, база транзистора 2 через резистор 9 соединена с

входным выводом 10 токового 3C|-Kanj 8 общий вывод 11 которого соединен с шиной 12 питания, а выходной вывод 13 токооого зеркала 8 соединен с базой транзистора 1, эмиттер транзистора 5 соединен с базой транзисторного ключа 6 Komei-тор ютсро- го соединен с выходом 14 RS-триггера и выходом эмиттерного повторитепя RS-триггер работает следующим образом.

Допустим, в исходном состоянии на входах 3 и 4 высокие уровни напряжений, а транзистор 5 и транзисторный ключ б закрыты и на выходе 14 высокий уровень напряжения. Однако тока базы эмиттерного повторителя 7 практически нет, поэтому нет и -тока эмиттера, так как транзистор 6 закрыт, Это возможно только в том случае, если нагрузка включена между шиной 12

о го о со

4

--А

питания и выходом 14. Включать нагрузку между выходом 14 и общей шиной нельзя, потому что триггер в противном случае будет иметь только одно устойчивое состояние. Поскольку на входах 4 высокие уровни напряжений и ток базы эмиттерного повторителя 7 оаьен нулю, то ток через резистор 9 и пходной вывод 10 токового зеркала 8 также отсутствует. Поэтому выходной ток токового зеркала 8 также равен нулю, что позволяет транзистору 5 быть закрытым.

Если в исходном состоянии один из входов 3 (входы S) замыкать на общую шину, то RS-триггер своего состояния не изменит. В

исходном состоянии все транзисторы RS- закрнты и он практически не по тпебпчег энерши от источника питания.

Если один из пы/.одов 1 (входы R) соединить в общей тиной, то возникает шк через M /I, В .во, 10 токового яеркалг 8, рези- г.гор 9 и одич и .геттеров транзистора 2 Зто пш Г-одит к появлению выходного гокэ гч оп-ч с р ла 8 через выходной вывод 13, который через прямосмещенный коллекторный переход транзистора 1 откроет транзистор 5. а значит и транзисторный ключ 6 На пиходе 14 установится низкий уровень напряжения. Одновременно протекает ток черпз коллектор транзистора 5, один из эмиттеров транзистора 2, поэтому ток через резистор 9 протекает и после того, как один из нчодов отключен от общей шины, и поддерживает ток через токовое зеркало, а значит транзистор 5 и транзисторный ключ 6 остаются в открытом состоянии, что определяет устойчивость второго состояния RS-триггера.

В этом состоянии замыкание входов 4 на общую шину уже не приводит к изменению состояния триггера.

Если во втором устойчивом состоянии один из входов 3 соединить с обшей шиной, то транзистор 1 переключится из инверсного состояния в состояние насыщения Это приводит к закрыванию транзистора 5, поэтому транзистор 2 переключается в инверсный режим и возникает ток базы транзистора эмиттерного повторителя 7 Последний открывается и током эмиттера перезаряжает выходные емкости нагрузки и завершает процесс рассасывания носителей в базе закрывающегося транзисторного ключа 6, После восстановления высокого уровня на выходе 14 ток базы эмиттерного повторителя 7 уменьшается до нуля, что приводит к закрыванию транзисторов токового зеркала 3. ток через базу транзистора 1 уменьшается до нуля и RS- триггер переключен в исходное состоян ле.

После установления на входах 3 высоких уровней транзистор 5 и транзисторный ключ 6 остаются закрытыми, потому, что нет тока через токовое зеркало 8.

Таким образом, подачей низких уровней на S- или R-входы RS-триггер может быть переключен в одно из двух устойчивых состояний. Время переключения предлага0 емого RS-триггера определяется временем переключения только одного ТТЛ логического элемента. Транзисторы токового зеркала работают в линейном режиме, поэтому время их переключения меньше, чем время

5 переключения насыщенных транзисторов ТТЛ-элемента.

В исходном состоянии RS-триггер практически не потребляет энергии, что повышает экономичность

0RS-триггер может быть выполнен по биполярной ТТЛ-технологии, при этом токовое зеркало выполняется на горизонтальных р - п - р-транзисторах (следует отметить, что требования к коэффици5 енту передачи тока базы в р - п - р- транзисторах токового зеркала не высоки, потому что общий коэффициент передачи токового зеркала может быть значительно меньше единицы, поэтому горизонтальная

0 структура р - п - р-транзисторов вполне приемлема). Токовое зеркало занимает на кристалле небольшую площадь. Это позволяет уменьшить общую, занимаемую RS- триггером, площадь в схемах с высокой

5 степенью интеграции

Формула изобретения RS-григгер, содержащий перпый много- эмиттерныи п - р - n-транзистор, эмиттеры которого соединены с S-входами, коллектор

0 подключен к базе фазорасщепляющего п - о - n-транзистора, эмиттер которого соединен с базой транзисторного ключа с общим эмиттером, коллектор которого соединен с выходом триггера и выходом эмиттерного

5 повторителя, второй многоэмиттерный п - р л-трандистор эмиттеры которого подключены к R-входам, а база соединена с первым выводом резистора, отличающийся гем, что, с целью уменьшения потребляемой

0 мощности, повышения быстродействия и уменьшения занимаемой площади при реализации на кристалле, в него введено токовое зеркало (отражатель тока) на р - п - р-гранзисторах, общий вывод которого сое5 динен с шиной питания, входной вывод соединен с вторым выводом резистора, а выходной вывод подключен к базе первого многоэмиттерного п. - р - п-транзистора, база эмиттерного повторителя соединена с коллектором второго многоэмиттерного п 516263416

р - n-транзистора, один из эмиттеров кото- ляющего п - р - п-транэистора выходного рого соединен с коллектором фазорасщеп- инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Троичный триггер на ТТЛ-инверторах | 1989 |

|

SU1727197A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

Изобретение относится к импульсной технике, в частности к устройствам с двумя устойчивыми состояниями. Цель изобретения -уменьшение потребляемой мощности повышение быстродействия и уменьи. ение занимаемой площади при реализации на кристалле. RS-триггер содержит первый и второй многоэмиттерные п - р - п-транзисторы, фазоинвертирующий п - р - п-трян- зистор, транзисторный ключ с общим эмиттером, эмиттерный повторитель и резистор. Введение токового зеркапа (отражателя тока) на р - п - р-транзисторэх позволяет уменьшить потребляемую мощность за счет ее снижения в единичном состоянии увеличить быстродействие за счет уменьшения задержки цепи обратной связи и уменьшит ь занимаемую площадь при реализации на кристалле, так как токовое зеркало занимает небольшую площадь. 1 ил (Л С

| Синхронный @ -Триггер | 1985 |

|

SU1336208A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Алексеенко А.Г., Шапурин И И Микросхемотехника | |||

| - М.: Радио и связь, 1982, с.199, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1991-02-07—Публикация

1989-02-27—Подача