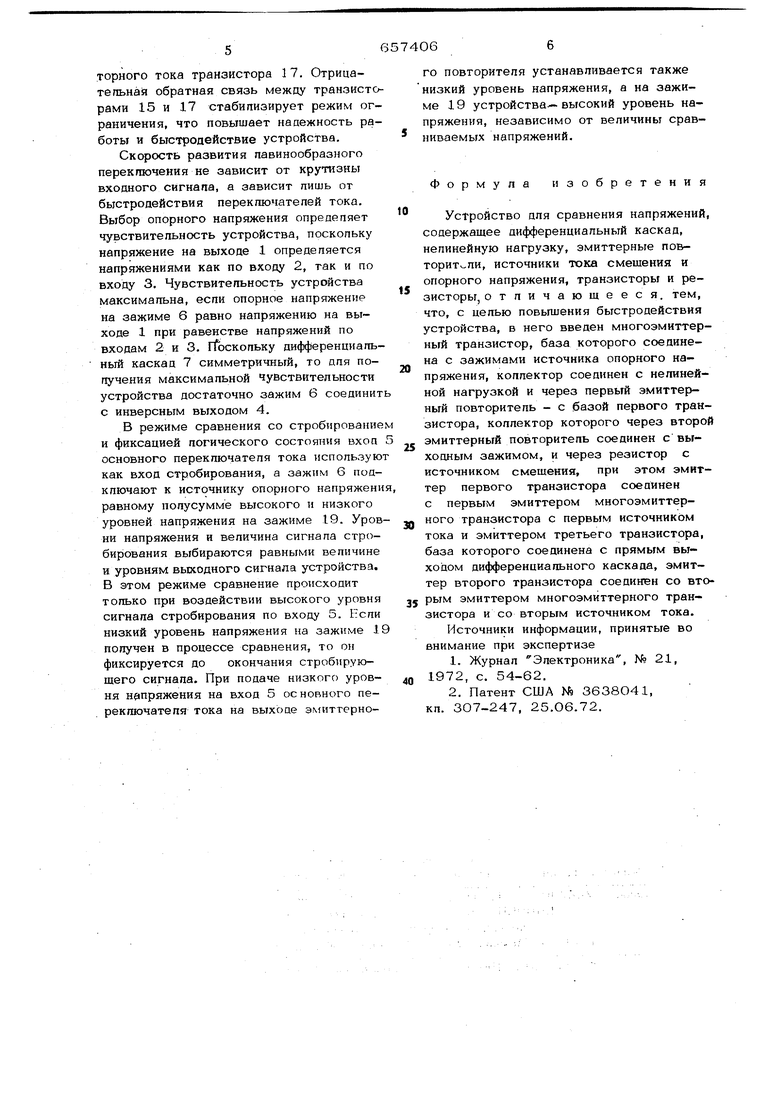

(54) УСТРОЙСТЕЮ ДЛЯ СРАВНЕНИЯ НАПРЯЖЕНИЙ соепинен с выходным зажимом и через -резистор - с источником смещения, при этом эмиттер первого транзистора соединен с первым эмиттером многоэмиттер ного транзистора, с первым источником тока и эмиттером третьего транзистора, база которого соединена с прямым выходом дифференциального каскада, эмиттер второго транзистора соединен с вторым эмиттером многоэмиттерного транзистора и с вторым источником тока. На чертеже представлена принципиаль ная электрическая схема предлагаемого устройства. Устройство вкгаочает в себя прямой выход 1 дифференциального каскада, прямой вход 2 дифференциального каскада и инверсный вход 3 дифференциального кас када, которые являются входами устройства, инверсный выход 4, дополнительный вход 5, зажим 6 источника опорного напряжения, дифференциальный каскад 7, соответственно третий, второй и первый транзисторы 8 - 10, второй и первый источники тока 11. и 12, многоэмиттерный транзистор 13, резистор 14 нелиней ной нагрузки, транзистор 15 нелинейной нагрузки, резистор 16 смещения транзистора 15, транзистор 17 эмиттерного повторителя цепи положительной обратной связи, выходной эмиттерньШ повторитель 18 и выходной зажим 19. Устройство обеспечивает возможность работы в следующих основных режимах: режим сравнения напр5шений без гистерезиса с чувствительностью, регулируемой как по величине, так и по знаку; режим сравнения со стробированием и фиксацией выбранного логического состояния. Для реализации режима сравнения без гистерезиса с регулируемой чувствительностью базу транзистора 9 подключают к выходу 1 дифференциального каскада, а зажим 6 подключают к источнику опорного напряжения, величина которого опре деляет чувствительность и.ее знак. Для получения максимальной- стабипьной чувствительности зажим 6 гаэпкпючаюТ к инверсному выхоцуг дифференциаль ного каскада... ; В режиме сравнения с регулируемой чувствительностью устройство: работает следукяцим образом .::. : к .- -, . Вхоц. 5 соединяют с выходом .lij-а аажим 6 соединяют с HCTO4HHKONf опорного напряжения, ;равного i полусумме высокого и низкого уровней напряжения на OG4 зажиме 1.0. Вхоцы 2 и 3 являются входами устройства. Пусть в исходном состоянии напряжение по входу 2 меньше по Величине, чем по входу 3, и одинаково с ним по знаку. Напряжение на прямом выходе 1 дифференциального каскада меньше опорного, транзисторы 8 и 9 заперты, а ток источников 1 1 и 12 переключен в нелинейную нагрузку транзистора 13. Транзистор Ю выключен, поскольку напряжение на эмиттере транзистора 17 меньше напряжения на базах транзисторов 8 и 9. Напряжение на зажиме 19 устройства соответствует низко1у1у уровню напряжения. Увеличение напряжения по входу 2 приводит к увеличению напряжения на выходе 1. Когда напряжение на нем станет равным опорному, то напряжение на эмиттере транзистора 17 также станет равно опорному, и транзистор 10 начинает открываться, что приводит к развитию лавинообразного процесса переключения тока источника 12 за счет попожительной обратной связи, реализуемой транзисторами-17 и 10, при этом транзистор 10 открыт, а транзисторы 13 и 8 заперты. На зажиме 19 устанавливается фиксированный низкий уровень напряжения. Дальнейшее увеличение напряжения по входу 2 не приводит к каким-либо изменениям на зажиме 19, ток источника 1 1 переключается в транзистор 9, на выходе эмиттерного повторителя появляется высокий уровень напряжения. Если напряжение на входе 2 уменьшается, то при равенстве напряжений на выходе 1 и опорного, ток источника 11 начинает переключаться транзистором 9 в нагрузку транзистора 13, напряжение на эмиттере транзистора 17 уменьшается и по достижении напряжения на выходе 1 происходит лавинообразный процесс переключения тока источника 12, в результате чего транзистор 10 закрьгеается, а транзисторы 18 и 13 включаются, на зажиме 19 напряжение достигает фиксированного высокого уровня. Транзистор . 5 автоматически ограничивает изменение напряжения на резисторе 14, исключая насьпцение транзистора 13. Максимальная величина ограничиваемого напряжения равна сумме напряжения; на .переходе эмиттерг-база транзистора 15; и падения напряжения на резисторе 16 при протекании коллекторного тока транзистора 17. Отрицатепьна 3 обратная связь между транзисторами 15 и 17 стабилизирует режим ограничения, что повышает надежность работы и быстродействие устройства.

Скорость развития павинообразного перекгпочения не зависит от крутизны входного сигнапа, а зависит пишь от быстродействия перекгаочатепей тока. Выбор опорного напряжения опредеаяет чувствительность устройства, поскольку напряжение на выходе 1 определяется напряжениями как по входу 2, так и по входу 3, Чувствительность устройства максимальна, если опорное напряжение на зажиме 6 равно напряжению на выходе 1 при равенстве напряжений по входам 2 и 3. ГГЬскольку дифференциальный каскад 7 симметричный, то для получения максимальной чувствительности устройства достаточно зажим 6 соединит с инверсным выходом 4.

В режиме сравнения со стробирование и фиксацией логического состояния вход основного переключателя тока использую как вход стробирования, а зажим 6 подключают к источнику опорного напряжени равному полусумме высокого и низкого уровней напряжения на зажиме 19. Уровни напряжения и величина сигнала стробирования выбираются равными величине и уровням выходного сигнала устройства. В этом режиме сравнение происходит только при воздействии высокого уровня сигнала стробирования по входу 5. Если низкий уровень напряжения на зажиме 19 получен в процессе сравнения, то он фиксируется до окончания стробируюшего сигнала. При подаче низкого уровня напряжения на вход 5 ос новного переключателя тока на выхоае эмиттерноГО повторителя устанавливается также низкий уровень напряжения, а на зажиме 19 устройства- высокий уровень напряжения, независимо от величины сравниваемых напряжений.

Формула изобретения

Устройство для сравнения напряжений, содержащее дифференциальный каскад, нелинейную нагрузку, змиттерные повторит ли, источники тока смешения и опорного напряжения, транзисторы и резисторы, отличающееся, тем, что, с целью повышения быстродействия устройства, в него введен многоэмиттерный транзистор, база которого соединена с зажимами источника опорного напряжения, коллектор соединен с нелинейной нагрузкой и через первый эмиттерный повторитель - с базой первого транзистора, коллектор которого через второй эмиттерный повторитель соединен с выходным зажимом, и через резистор с источником смешения, при этом эмиттер первого транзистора соединён с первым эмиттером многоэмиттерного транзистора с первым источником тока и эмиттером третьего транзистора, база которого соединена с прямым выходом дифференциального каскада, эмиттер второго транзистора соединен со вторым эмиттером многоэмиттерного транзистора и со вторым источником тока.

Источники информации, принятые во внимание при экспертизе

1.Журнал Электроника, № 21, 1972, с. 54-62.

2.Патент США № 3638О41, кл. 307-247, 25.Об.72.

бе.

e + U

«t-f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| Усилитель переменного тока с регулируемым коэффициентом усиления | 1989 |

|

SU1658375A1 |

| КАСКАД УСИЛИТЕЛЯ С РЕГУЛИРУЕМЫМ УСИЛЕНИЕМ, УСИЛИТЕЛЬ С РЕГУЛИРУЕМЫМ УСИЛЕНИЕМ, ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 1993 |

|

RU2140705C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2157048C2 |

| Устройство электронной защиты | 1980 |

|

SU974358A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU815902A1 |

| Комплементарный логический элемент и-или/и-или-не | 1978 |

|

SU718929A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

Авторы

Даты

1979-04-15—Публикация

1976-03-09—Подача