1

Изобретение относится к имиульсной нике.

Известен троичный логичесхи/ элемент, содержащий четырехэмиттерныт onopHbiii транзистор, два эмиттера которого соединены с эмиттерами транзисторов входного элиттсрного повторителя, а два других змитте и, -с эмиттерами транзнсторо змиттерного повторителя в цени обратной связи, Bbixo;i:io;; чмиттерный новторитель, база тр Н31 стора которого соединена с коллектором четырсхэл;;;:терного онорного транзистора, а коллекго) соединен с базой одного из транзисторов элтнттерного повторителя в цени обратной .

Известный логический элемент не обеспечивает достаточной стабильности, достаточного диапазона частот и имеет большое пот1:сб. ение мощности.

Цель изобретения - новьпленпе сгаби.,ности работы, расщиреиие частотного днг;нг:зона и уменьшеннс нотребляелюй монпост;:.

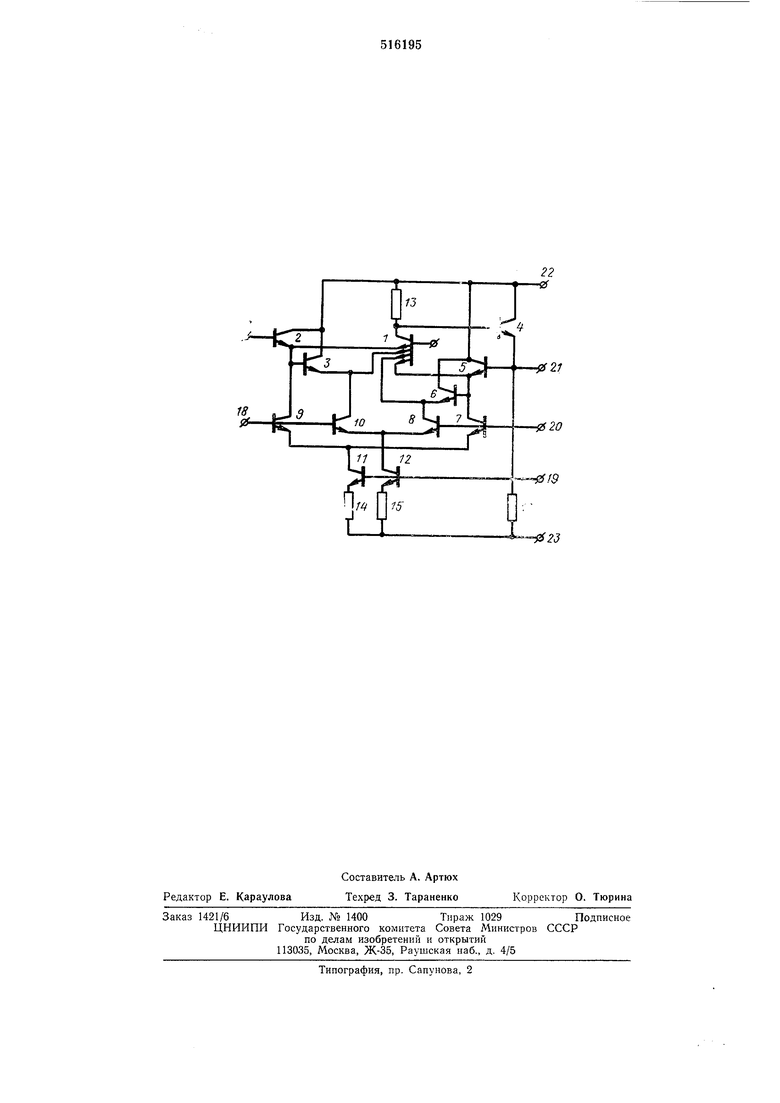

В предлагаемом троичном логическом з/ieменте это достигается введеннем в него лвух переключателей тока на двух транзисторах каждый, иричем коллектор одного из трр1::;;:сторов нервого переключателя тока соединен с эмиттером и базой транзисторов входного эмиттерного повторителя, коллектор вторОго транзистора нервого перек.иочатсля токп соединен с эмнттепом второго тпапзнетсп: п(У(того эмнттер1юго повторителя, а на соединен;Ь:е базы транзнсгороз нервого нереключате1я тока нодан унрав. сигнал, коллекroj) нерБого транз11сто)а второго перек.тючаго,i;i тока соединен с базой н эмнттером тран;;сго; ов эмгггтерного новторителя в цени об. спйзн. коллектор второго транзистора о ;;ере;слючателя тока соединен с эмитзторого гранзнстора эмнттерного преля в н,енн обратной связн, а на соеди: базы транз :сторов второго нереклюока нодано онорпос напряжение, нрнм эмиттеры соответствующих транзисторов 1)вого :i второго переключателей тока по|;но соединены н подключены к коллектоi:vi донолнительных транзнсторов, на соеднiiHbie базы которых нодано онорное напрячертеже нриведена принципиальная : 1ическая схема поедлагаелюго тропчногичес; ого з,1еме1гта.

гнческнй 3.ie ;e:rr содержнт четырехэмпт,ni о1:ор1Ы1 т;)анзнстор 1, входной эмнт п; повтокггель на каскадпо-включенных зиего)ал 2, 3, эмнттерный новторнтель в обратной евязн на каскадно-включепных эисторах 4, 5, выходной эмпттерпып поттель на трапзнсторе 6, переключатели

на ;-р;п1згетормх 7, 8 н 9, 10, дополнн1Ы тпгнз: етО:Н11 11. 12 i; леяистопы 13-

16. Индексами 17, 18 обозначены входы, на которые поданы соответственно троичный входной сигнал и управляющий сигнал. Индексами 19, 20 обозначены входы, на которые поданы опорные сигналы, индексом 21 обозначен выход элемента, а индексами 22,23 входы, на которые подано положительное напряжение от источника питания (не показан).

Принцип работы предлагаемого троичного логического элемента заключается в следующем.

На базу транзистора 2 подается троичный информационный сигнал с логическими уровнями О, 1, 2, квантованного по амплитуде с квантом, равным падению напряжения на переходе база-эмиттер транзистора. На базы транзисторов 9 и 10 подается управляющий двоичный сигнал с логическими уровнями О, 1, определяющий режим работы элемента: режим хранения и режим записи. В режиме хранения на входе 18 устанавливается уровень логического «О. При этом транзисторы 9 и 10 выключены, транзисторы 7 и 8 включены и замыкают обратную связь в элементе. В режи.ме записи на вход подается импульс записи. При этом транзисторы 9 и 10 включаются, транзисторы 7 и 8 выключаются, и обратная связь разрывается. На выходе устанавливается уровень сигнала, соответствующий уровню информационного сигнала. При условии подачи на вход 17 уровня логического «О транзисторы 2 и 3 выключены, и токи текут через опорный транзистор 1, обуславливая падение напряжения на резисторе 13, равное удвоенному падению напряжения на переходе база-эмиттер транзистора 1, т. е. на выходе устанавливается уровень логического «О. При условии подачи на информ; ционный вход уровня логической «1 транзистор 2 включен, транзистор 3 выключен, и ток, текущий через транзистор 10, обусловливает падение напряжения на резисторе 13, равное падению напряжения иа переходе база-эмиттер транзистора 1. При условии нодачи на вход 17 уровня логической «2 транзистор выключен, и на выходе устанавливается уровеиь логической «2. После окончания импульса записи на входе 18 устанавливается уровень логического «О, транзисторы 7, 8 включаются и замыкают обратную связь, фиксируя информацию, подаваемую в режиме записи. Дальнейшее возможное изменение сигнала на входе 17 не влияет иа хранящуюся информацию.

Формула изобретения

Троичный логический элемент, содержащий

четырехэмиттерный опорный транзистор, два эмиттера которого соединены с эмиттерами транзисторов входного эмиттерного повторителя, а два других эмиттера - с эмиттерами транзисторов эмиттерного повторителя в цепи

обратной связи, выходной эмиттерный повторитель, база транзистора которого соединена с коллектором четырехэмиттерного опорного транзистора, а коллектор соединен с базой одного из транзисторов эмиттерного повторителя в цепи обратной связи, отличающийся тем, что, с целью повыщения стабильности работы, расн1ирения частотного диапазона и уменьшения потребляемой мощности, в него введены два переключателя тока на двух

транзисторах каждый, причем коллектор одного из транзисторов первого переключателя тока соединен с эмиттером и базой транзисторов входного эмиттерного повторителя, коллектор второго транзистора первого переключателя тока соединен с эмиттером второго транзистора входного эмиттерного повторителя, а на соединенные базы транзисторов первого переключателя тока подан унравляющий сигнал, коллектор первого транзистора второго переключателя тока соединен с базой и эмиттером транзисторов эмиттерного повторителя в цеии обратной связи, коллектор второго транзистора второго переключателя тока соединен с эмиттером второго транзистора

эмиттерного повторителя в цепи обратной связи, а на соединенные базы транзисторов второго переключателя тока подано опорное напряжение, причем эмиттеры соответствующих транзисторов первого и второго иереключателей тока попарно соединены и подключены к коллекторам дополнительных транзисторов, на соединенные базы которых подано опорное напряжение.

SH21

020

-fS2d

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU430445A1 |

| Элемент троичной логики | 1980 |

|

SU892729A1 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

| Пороговое устройство | 1972 |

|

SU464069A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1969 |

|

SU256065A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Многопороговый логический элемент | 1972 |

|

SU481136A1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

Авторы

Даты

1976-05-30—Публикация

1974-04-01—Подача