времени разряда ковденсатора, коэффициет передачи по компенсационному входу гораздо больше коэффициента передачи по интегрирующему входу 3.

Однако в данном устройстве выходной ток интегрирующего усилителя ограничен и время сброса конечно, что приводит к оишбке, которая накапливается с каждым сбросом.

Цель изобретения - повышение точности интегрирования.

Поставленная цель достигается тем, что устрюйство для интегрирова1шя в СОК содержит два двухпозиционных ключа и второй интегрирующий конденсатор, одна из обкладок которого подключена к выходу операционного усилителя, вторые обкладки интегрирующего конденсаторов соединены с переключающим контактом соответствующего двухпозиционного ключа, первьш контакт каждого из которых соединен с суммирующим входом операционного усилителя, второй контакт подключен к второму выводу соответствующего токоограничивающего резистора, причем управляющие входы двухпозиционных ключей связаны с выходами триггера.

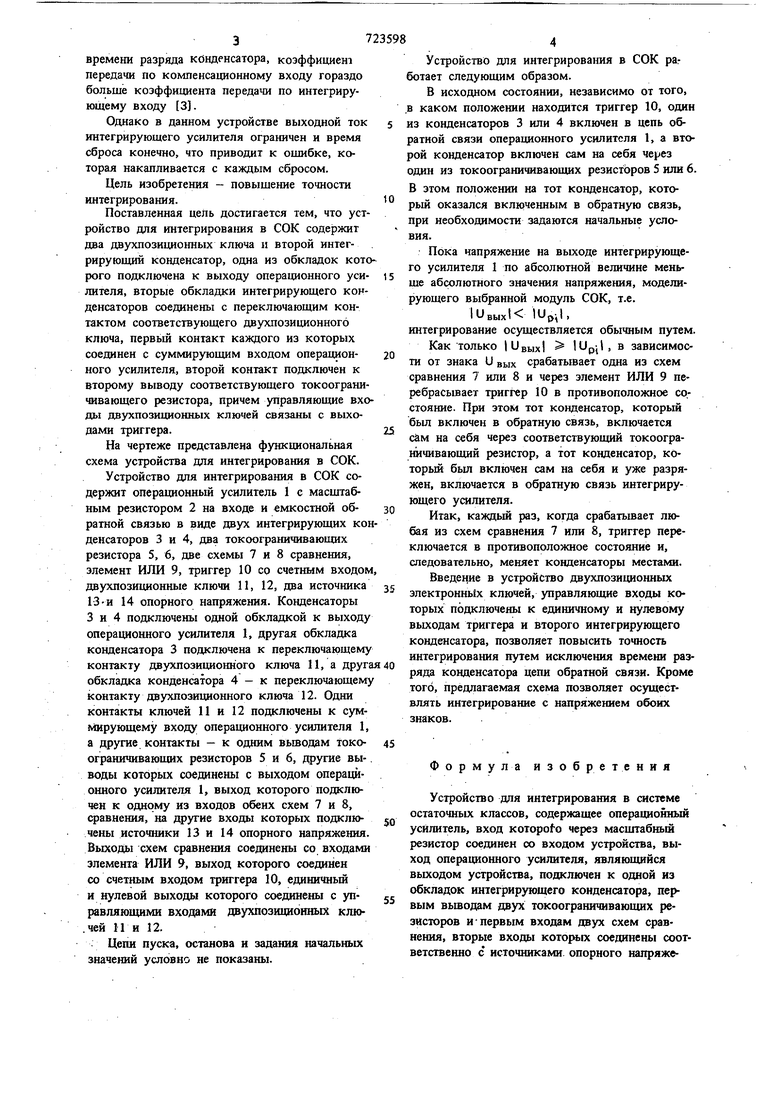

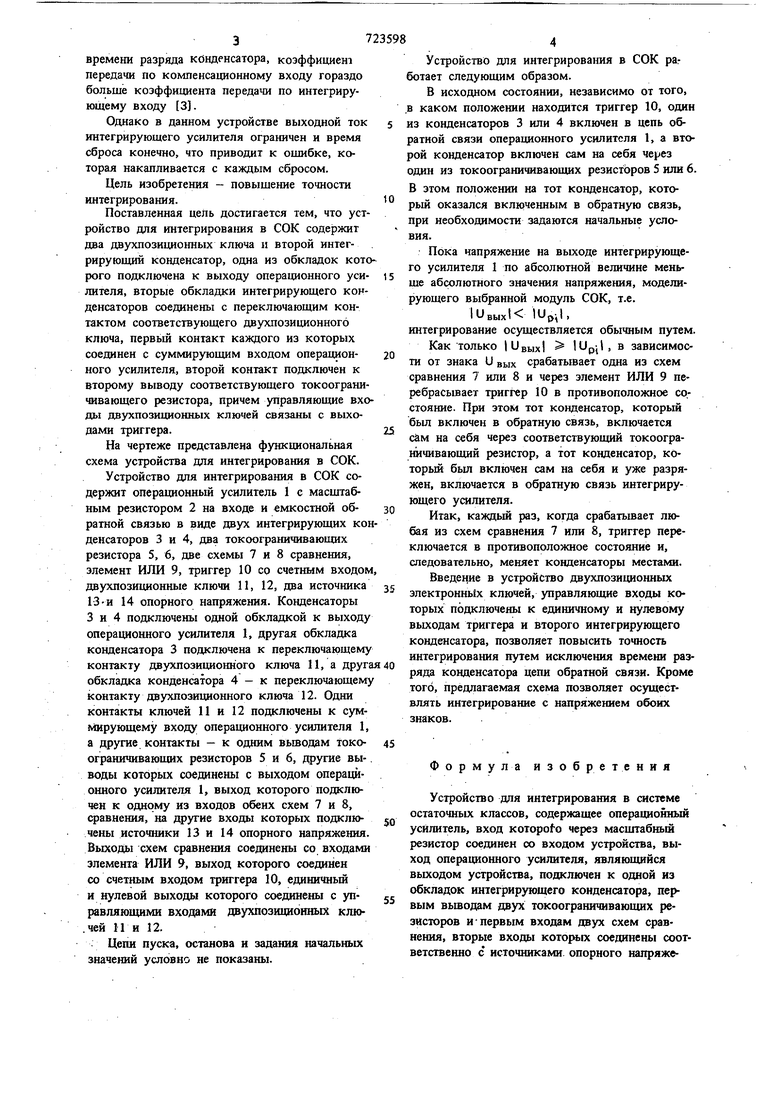

На чертеже представлена функциональная схема устройства для интегрирования в СОК.

Устройство для интегрирования в СОК содержит операционный усилитель 1 с масштабным резистором 2 на входе и емкостной обратной связью в виде двух интегрирующих конденсаторов 3 и 4, два токоограничивающих резистора 5, 6, две схемы 7 и 8 сравнения, злемент ИЛИ 9, триггер 10 со счетным входом двухпозиционные ключи 11, 12, два источника 13-и 14 опорного напряжения. Конденсаторы 3 и 4 подключены одной обкладкой к выходу операционного усилителя 1, другая обкладка конденсатора 3 подключена к переключающему контакту даухпозиционного ключа И, а друга обкладка конденсатора 4 - к переключающему контакту двухпозиционного ключа 12. Одни контакты ключей И и 12 подключены к суммирующему входу операционного усилителя 1, а другие контакты - к одним вьтодам токоограничивающих резисторов 5 и 6, другие выводы которых соединены с выходом операционного усилителя 1, выход которого подключен к одному из входов обеих схем 7 и 8, сравнения, на другие входы которых подключены источники 13 и 14 опорного напряжения. Выходы схем сравнения соединены со входами элемента ИЛИ 9, выход которого соединен со счетным входом триггера 10, единичный и нулевой выходы которого соединены с управляюишми входами двухпозициоиных .чей 11 и 12.

Цепи пуска, останова и задания начальных значений условно не показаны.

Устройство для интегрирования в СОК ра: ботает следующим образом.

В исходном состоянии, независимо от того, в каком положении находится триггер 10, один из конденсаторов 3 или 4 включен в цепь обратной связи операционного усилителя 1, а второй конденсатор включен сам на себя через один из токоограничивающих резисторов 5 или 6.

В зтом положении на тот конденсатор, который оказался включенным в обратную связь, при необходимости задаются начальные условия.

Пока напряжение на выходе интегрирующего усилителя 1 по абсолютной величине меньше абсолютного значения напряжения, моделирующего выбранной модуль СОК, т.е.

lUBbixK , интегрирование осуществляется обычным путем.

1U

Как только I и

в зависимосвых1

Pi

ти от знака U вых срабатывает одна из схем сравнения 7 или 8 и через элемент ИЛИ 9 перебрасывает триггер 10 в противоположное состояние. При зтом тот конденсатор, который был включен в обратную связь, включается сам на себя через соответствующий токоограшчивающий резистор, а тот конденсатор, который был включен сам на себя и уже разряжен, включается в обратную связь интегрирующего усилителя.

Итак, каждый раз, когда срабатывает любая из схем сравнения 7 или 8, триггер переключается в противоположное состояние и, следовательно, меняет конденсаторы местами.

Введение в устрюйство двухпозиционных электронньГх ключей, управляющие входы которых подключены к единичному и нулевому выходам триггера и второго интегрирующего конденсатора, позволяет повысить точность интегрирования путем исключения времени разряда конденсатора цепи обратной связи. Кроме того, предлагаемая схема позволяет осуществлять интегрирование с напряжением обоих знаков.

Формула изобретения

Устройство для интегрирования в системе остаточных классов, содержащее операционный усилитель, вход KOTopofo через масштабный резистор соединен со входом устройства, выход операционного усилителя, являющийся выходом устройства, подключен к одной из обкладок интегрирующего конденсатора, первым вьшодам двух токоограничивающих резисторов и-первым входам даух схем сравнения, вторые входы которых соединены соответственно с источниками опорного напряжения противоположной полярности, а выходы через элемент ИЛИ подключены к счетному входу триггера, отличающееся тем что, с целью повышения точности, оно содержит два двухпозиционных ключа и второй интегрирующий конденсатор, одна из обкладок которого подключена к выходу операционного усилителя, вторые обкладки интегрирующих конденсаторов соединены с переключающим контактом соответствующего двухпозиционного жлюча, первый контакт каждого из которых соединен с суммирующим входом операционного усилителя, второй контакт подключен

к второму вьшоду соответствующего токоограничивающего резистора, причем управляющие входы двухпозиционных ключей связаны с выходами триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 233299, кл. G Об; G 7/18, 1967.

2.Авторское свидетельство СССР № 437090, кл. G 06 G 7/18, 197г

3.Авторское свидетельство СССР N 249072, кл. G 06 G 7/18, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Квадратор | 1982 |

|

SU1084824A1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| Квадратично-множительный преобразователь | 1974 |

|

SU502383A1 |

| Способ определения нагрузочной способности сухих трансформаторов и устройство для его осуществления | 1985 |

|

SU1278732A1 |

| Интегрирующий преобразователь постоянного напряжения вов временной интервал | 1970 |

|

SU734875A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU769632A1 |

| Интегратор | 1975 |

|

SU542200A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1357856A1 |

| Интегратор | 1980 |

|

SU928369A1 |

.

Авторы

Даты

1980-03-25—Публикация

1978-03-01—Подача