ния через третий дополнительный масштабный резистор соединен со входом второго блока интегрирования, выход усилителя постоянного тока второго блока интегри- poBaiiHH через четвертый доподнитепьный масштабный резистор - со входом первого блока интегрирования; выходы первого и второго интегрирующих блоков объединены и соединены с первым входом сумматора и с одним неподвижным контактом дополнительно введенного переключателя, другой неподвижный контакт которого соединен со входом, запоминающего блока. Выход последнего связан со вторым входом сумматора а управляющий вход запоминающего блока подключен к выходу блока управления Подвижный контакт дополнительно введенного переключателя соединен с одной обкладкой дозирующего конденсатора другая обкладка которого соединена с шиной нулевого потенниала.

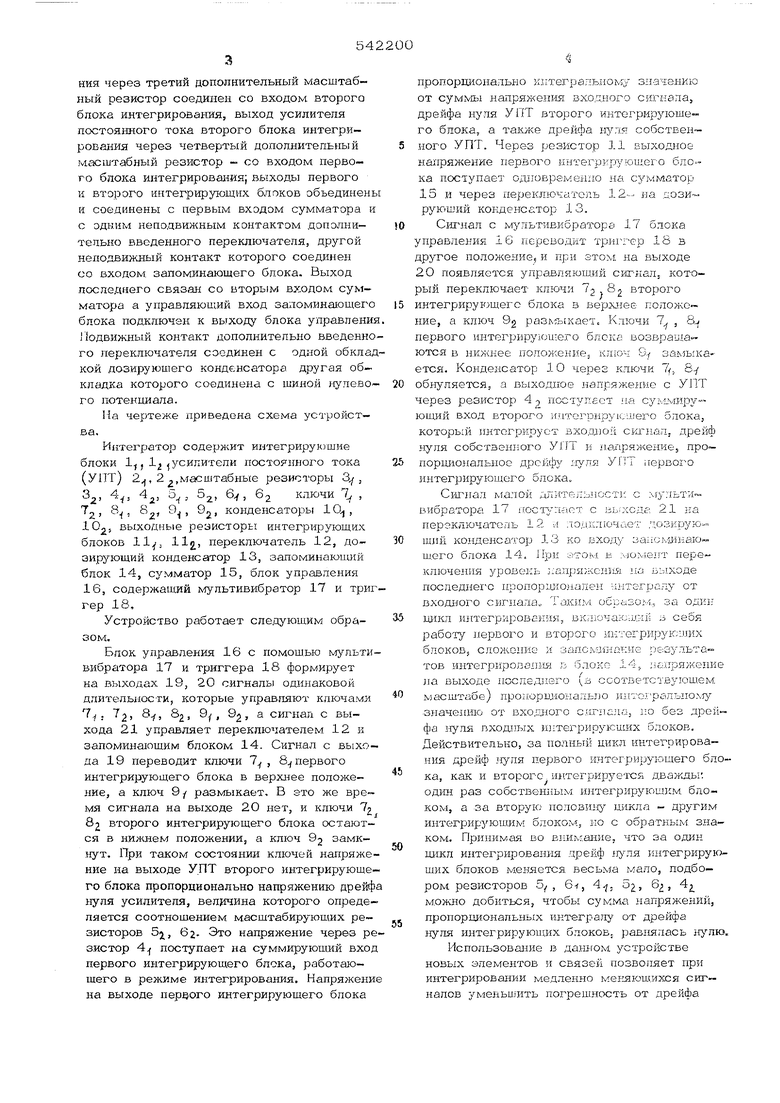

На чертеже приведена схема устройства.

Интегратор содержит интегрируюшие блоки 1 усилители постоянного тока (УПТ) 2, 2 2,масштабные резисторы 3, 3, 4, 4,,, 5, 5, 6, бз ключи 7 , Т, 8. 8, 9, Э, конденсаторы 10, выходные резисторы интегрирующих блоков переключатель 12, дозирующий конденсатор 13, запоминающий блок 14, сумматор 15, блок управления 16, содержащий мультивибратор 17 и триггер 18,

Устройство работает сле.дующим образом.

Блок управления 16 с помощью мультивибратора 17 и триггера 18 формирует на выходах 19, 2О сигналы одинаковой длительности, которые управляют ключами 7. 2i Q-i, 82, 9у, 9, а сигнал с выхода 21 управляет переключателем 12 и запоминающим блоком 14. Сигнал с выхода 19 переводит ключи 7, 8 первого интегрирующего блока в верхнее положение, а ключ 9/ размыкает, В это же время сигнала на выходе 2О нет, и ключи Tj 82 второго интегрирующего блока остаются в нижнем положении, а ключ 82 замкнут. При таком состоянии ключей напряжение на выходе УПТ второго интегрирующего блока пронорционально напряжению дрейфа нуля усилителя, величина которого определяется соотношением масщтабирующих резисторов 5j, 62- Это напряжение через резистор 4 поступает на суммирующий вход первого интегрирующего блока, работающего в режиме интегрирования. Напряжение на выходе первого интегрирующего блока

пропорционально интегральиому значению от cyMvibi напряжения входного CHPHanaj дрейфа нуля УЬТ второго интегрируюшего блока, а также дрейфа собствен5 иого УПТ. Через резистор J. 1 выходное напряжение первого интегокруюш.его блока поступает одповременпо на сумматор 15 и через переключатель 12- на дози-. рующий конденсатор 13. 0 Сигнал с мультивибратора 17 блока управления 16 переводит триггер 18 в другое положение, и при зтом. на выходе 20 появляется .ий сиг-каЯ; который переключает ключи 72 . 82 второго 5 интегрирующего блока в верхнее положс ние, а ключ Q разлсыкает. Ключи 7, , 8j первого интегрирующего бпока возвраидаются в нижнее положеию, ключ О/ закШ;ка-ется. Конденсатор 10 через ключи 7f, 8-/ 0 обнуляется, а выходное напряжение с УПТ через резистор 4р поступест иа суммирующий вход второго H.UTcrpiipyiciiiero блока, который интегрирует входной сигнал, дрейф нуля собстаенкого УНТ и лалряжение, про- 5 порциоыальное дрейфу нуля У1ТТ иервого интегрирующего блока.

Сигнал малой длитепьлост : с мультивибратора 17 nocTjAfic-r с 21 ка 1 9

0 щий конденсатор 13 ко входу запок-шкаюш.его блока 14. ilpii этом, в момент пере.ключения уровень ::а:аря;кс1иш иа выходе последнего пропорщ-юнаяек иитегрслу от входного сигнала Т;жн1-л образом, за один

5 Щ1КЛ иптегрировакия, ик почающнй а себя работу первого и второго И1-;тегрирую;.иих бпокоВ; сдожоние и запслшнакие результатов интегриройа11.:Ш ь блоке- 14,, ;1сипряжение па выходе поспедиего (Е, соответствующем

5 масштабе) пронорщ-гаыаяыю иито.траяьиом значению от входного c.iriicjiG, по без дрейфа нуля пход,т1ых ш-тегрируюших блоков. Действительно, за полный цикл интегрирования дрейф пуля первого интегрирующего блока, как и второго, интегрируегся дважльг.

один раз собственным интегрирующим, блоком, а за вторую половищ цикла - другим интегрирующим бяоком; но с обратным з,наком. Принимая во влимш-ше. что за один цикл интегрирования дрейф интегрирующих блоков меняется весьма мало, подбором резисторов 5f , 6-(, 4. 5, 6, 4 м.ожно добиться, чтобы сумма напряжений,

пропорциональных интегралу от дрейфа

нугш интегрирующих олоков. равнялась

Использование в да,ш-,ом устройстве новых элементов и связей позволяет при интегрировании медленно мекяюш.ихся сиг™ налов уменьшить погрешность от дрейфа

нуля усилителей постоянного тока входных блоков интегрирования, снизить требования к УПТ. Устройство может быть легко выполнено методами интегральной технологии.

Формула изобретения

Интегратор, содержащий интегрирую- щие блоки на усилителях постояьшого тока с конденсатором, в цепи обратной связи, ключи, блок управления, выходы которого соединены с управляющими входами ключей сумматор, выход которого является выходом интегратора, входы интегрируюших блоков через два масштабных резистора подключены ко входу интегратора, о т л и- чающийся тем, что, с целью повыщения точности интегрирования, в него

введены дополнительные масштабные ре- зисторы, переключатель, запоминаюший блок, дозирующий конденсатор, причем в каждом интегрирующем блоке первый ключ включен между входом усилителя

постоянного тока с одной обкладкой конденсатора, второй - между выходом усилителя постоянного тока и другой обкладкой конденсатора, вход усилителя постоянного тока через последовательно соединенные первый дополнительно введенный масштабный резистор и третий ключ соединен

с выходом усилителя постоянного тока и через второй дополнительный масштабный резистор - с суммирующим входом интегрирующего блока1выход усилителя постоянного тока первого интегрирующего блока через третий дополнительный масштабный резистор соединен со входом второго интегрирующего блока, выход усилителя постоянного тока второго интегрирующего блока через четвертый дополнительный масштабный резистор - со входом первого интегрирующего блока, выходы первого и второго интегрирующих блоков объединены и соединены с первым входом сумматора и с одним неподвижным контактом дополнительно введенного переключателя, другой неподвияшый конTaiiT которого соединен со входом запоминающего блока выход последнего связан со вторым входом сумматора, а управляющий вход запоминающего блока подключен к выходу блока управления, подвижный контакт дополнительно введе1шого переключа-теля соединен с одной обкладкой дозирующего конденсатора, другая обкладка которого соединена с шиной нулевого потенщшла.

Источники информации, пршштые во внимание при экспертизе:

1, Авторское свидетельство № 301713, &06 & 7/18, 28.11.69.

2 Смолов В. Б, Аналоговые вычислительные машины, изд. Высшая школа, Москва, 1972, стр. 179.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования постоянного тока | 1983 |

|

SU1166144A1 |

| Интегратор | 1989 |

|

SU1764063A1 |

| Устройство для интегрирования постоянного тока | 1978 |

|

SU1091183A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| Интегратор с запоминанием | 1984 |

|

SU1228122A1 |

| Интегратор | 1980 |

|

SU928369A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Устройство для интегрирования сигнала | 1988 |

|

SU1571623A1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Усилитель постоянного тока | 1981 |

|

SU1003300A1 |

Авторы

Даты

1977-01-05—Публикация

1975-07-07—Подача