(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Многопредельный усилитель заряда | 1982 |

|

SU1113754A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Интегрирующее устройство | 1983 |

|

SU1105903A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU888210A1 |

| Интегратор | 1979 |

|

SU834715A1 |

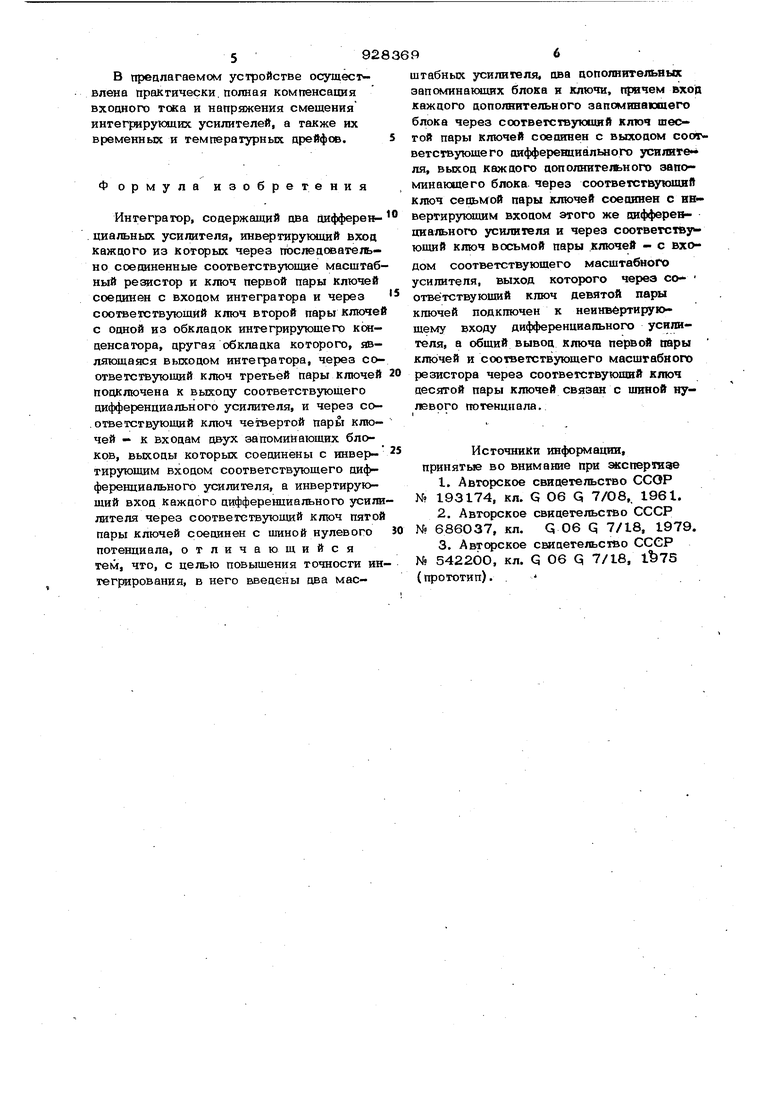

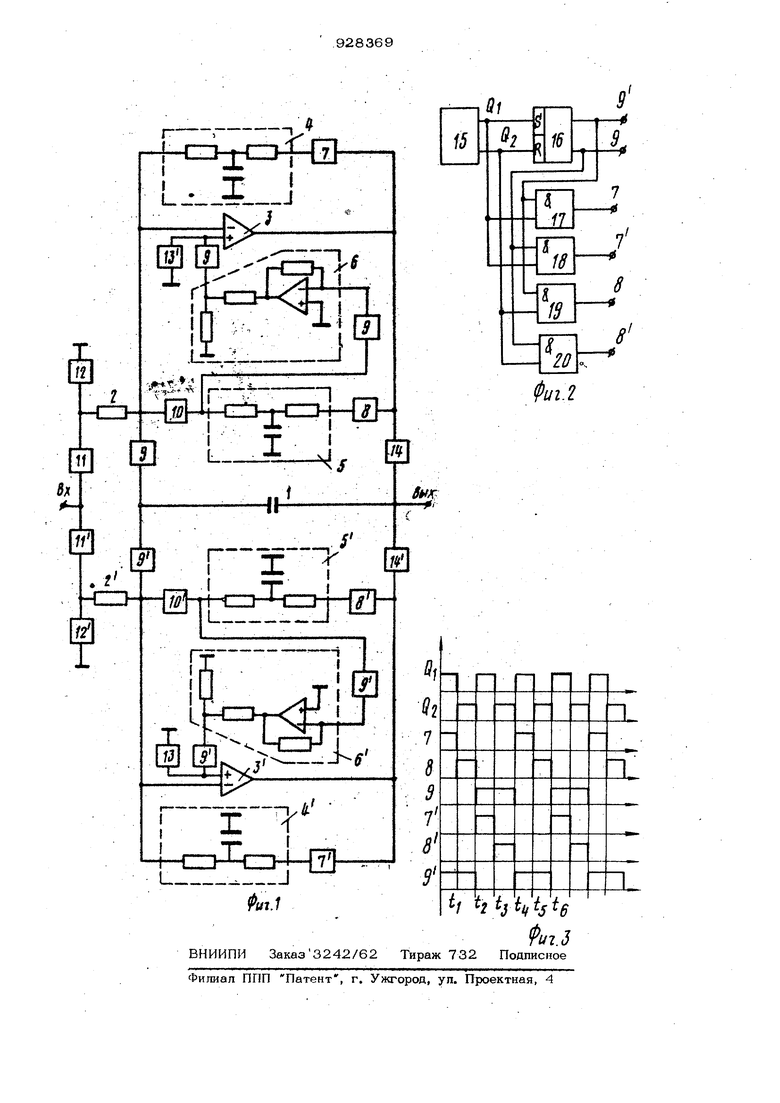

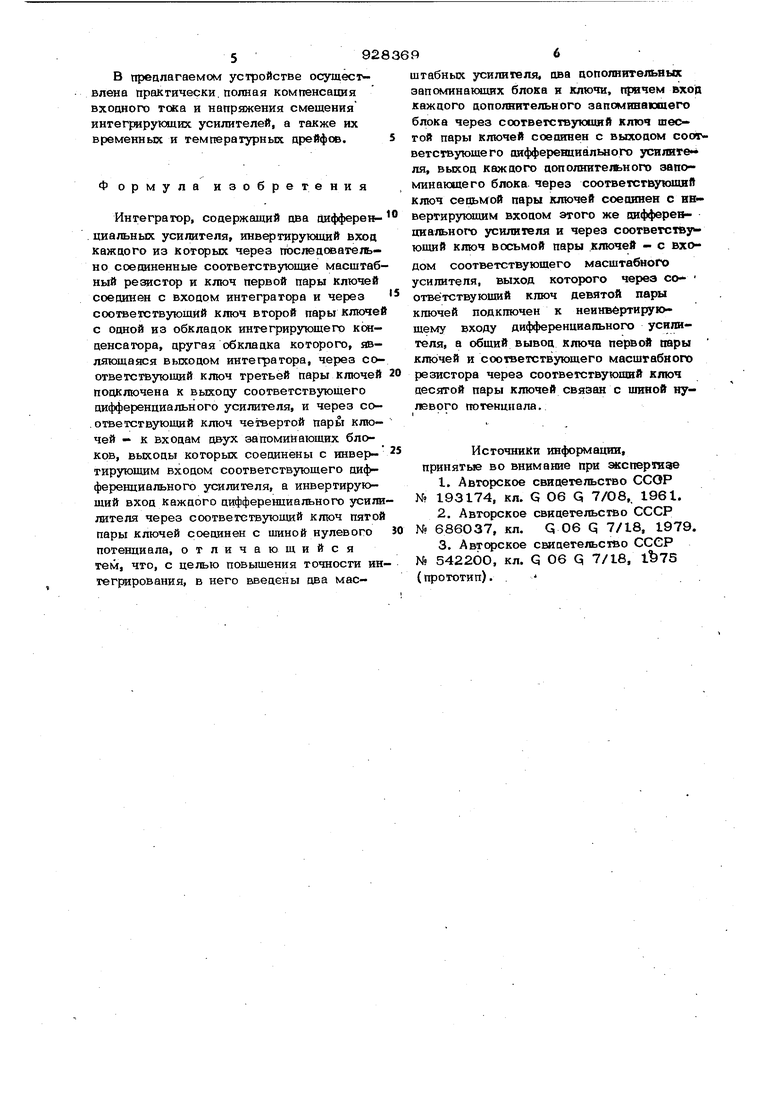

Изобретение огносится к аналоговой вьгчислигельной технике и может быть использовано при аналоговых вычислительных устройствах и системах автоматического управления. Известны интеграторы, соцержащие интегрирующие блоки, выполненные на усилителях постоянного тока с конденсатором в цепи обратной связи, ключи со схемами управления, масштабные резисторы, блок управления, выхоцы которого соединены с управляющими входами ключей 12.. Наиболее близким по технической сущ ности к предлагаемому является ингегратор, содержащий дифференциальные усилители с интегрирующими Конденсаторами в цепи обратной связи, запоминающие блоки, ключи, управляющие входы которых подключены к блоку управления ГЗ. Недостатками известньсс интеграторов являются неполная компенсация как начального входного тока (а также его температурного и временного дрейфа) интегрирующих уситтителей гак и начально- , го напряжения смещения и его температурного и временного дрейфа. Кроме того, дополните/шная погрешность появляется из-за неравенства величин ингегрж рующих конденсаторов, а также появления на обкладках интегрирующих конденсаторов напряжения, вызванного аффектом адсорбции после замыкания обкладок конденсаторов на качсаом такте работы устройства. Цель изобретения - повышение точности интегрирования. Поставленная цель достигается тем, что в интегратор, содержащий два ия ференциальных усилителя, инвертирукииий вход каждого из которых через последовательно соединенные соответствующие масштабный резистор и ключ первой пары ключей Соединен со входом интегратора и через соответствующий ключ второй пары ключей с одной из обкладок интегрирующего конденсатора, другая обкладка которотх), являющаяся выходом И1 тегроторп, через соогвегствуюший ключ Tpeibeft пары ключей подключена к выхоцу соогвегсгвующего дифференциального усилителя и через соответствующий ключ четвертой пары ключей - К выходам двух запоминающих блоков, выходы которых соединены с инвертирующим входом СОО-Рветствующего дифференциального усилитеяя,а инвертирующий вход каждого дифференциального усилителя через соответствующий ключ пятой пары ключей соединен с шиной нулевого потенциала, введены два масщтабных усилителя, два дополнительных запоминающих блока и ключи, причем вход каждого дополнительного запоминающего блска через соответс1 у ющий ключ шестой пары ключей соединен с выходом соответствующего дифференци альнрго усилителя, выход каждого дополнительного запоминающего блока через соответствующий ключ седьмой пары ключей соединен с инвертиругсшим входом этого же дифференциального усилителя и через соответствующий ключ восьмой пары Ключей - с входом соответствующего масштабного усилителя, выход которого через соответствующий ключ девятой пары Ключей подключен к неинвертирующему входу дифференциального усилителя, а общий вывод Ключа первой пары ключей и соответствующего масштабного резистора через соответствующий ключ десятой пары Ключей связан с шиной нулевого потенциала, На фиг. 1 приведена схема интегратоpajHa фиг. 2 - блок управления ключами; на фиг,. 3 - временная диаграмма замкнутого состояния ключей. Устройство содержит интегрирующий конденсатор 1 и два идентичных интегрирующих блока, каждый из которых вклю чает масштабный резибтор 2 (2 ), дифференциальный усилитель 3 (З), два запоминающих блока 4 (4 ) и 5 (5), два масштабных усилителя 6 (б ) с резисторным делителем напряжения на выходе и пары ключей 7 ( ), 8 (8), 9(9), Ю (1.0), И (11), 12 (12), 13 (13) и 14 (.14). Блок управления ключами (фиг. 2) со держит генератор 15 импульсов, триггер 16, элементы И 17-20. Интегратф работает следукицим образом. В течение времени О- t т замкнуты ключи 7 и 9 , 11 , 13 и 14, Интегрирующий конденсатор I подключен к дифференциальному усилителю Э а неинвертирующий вход дифференциального усилителя 3 интегрирующего блока замкнут на шину нулевого потенциала, а в цепи его обратной связи включен запоми- натоший блок 4, в котором конденсатор заряжается до напряжения, пропорционального входному току усилителя 3. Выбором резисторов в запоминающем блоке 4 стараются получить возможно большое напряжение на запоминающем кондя саторе блока, чтобы величиной нескомпенсированного в этот момент начального смешения усилителя 3 можно было пренебречь и считать, что величина запоминаемого напряжения, пропорциональна входному току усилителя. В течение времени -j- t(j ключ 7 разомкнут, замьйсаются к.лючи 8, 1О, 12, Инвертирующий вход усилителя 3 через входной масштабный резистор 2 подключается к шине нулевого потенциала, а в цепь обратной связи усилителя 3 включается второй запоминающий блок 5. Поскольку с помощью блока 4 Компенсирован входной ток усилителя 3 по инвертирующему входу напряжение на запоминающем конденсаторе блока 6 пропорционально напряжению смещения. Выбором резисторов в блоке 5 стараются получить возможно большое напряжение на запоминающем конденсаторе блока 5, чтобы по сравнению с его величиной можно было бы пренебречь начальным смещением масштабного усилителя 6, С помощью резисторного делителя напряжения на выходе усилителя 6 приводится в соответствие величина запоминаемого напряжения в блоке 5 напряжению смещения усилителя 3, которое в рабочий такт ( t) подается для компенсации напряжения смещения на инвертирующий вход усилителя 3 с обратным знаком. Желательно этот резисторный делитель напргокения выполнить на возможно низкоомных резисторах. Это снижает до минимума нескомпенсированную помеху от протекания по нему входного тока усилителя 3 по неинвертирующему входу. В течение t (j - 14 скомпенсир(Жанный усилитель 3 подкточается к интегрирующему конденсатору 1 и через входной масштабный резистор 2 - ко входу устройства, а усилитель (З) аналогично проходит два этапа компенсации. После чего циклы работы устройства повторяются. . Технико-экономический эффект от применения предлагаемого интегратора заключается в пшышении точности интегрирования. В tipeanaraevfOM устройстве осуществлена практически.полная компенсация вхоциого тока и напряжения смещения интегрирующих усилителей, а также их временных и температурных црейфов. Формула изобретения Интегратор, содержащий два дифферен циальных усилителя, инвертирукшшй вход каждого из которых через пЬс;юдовательно соединенные соответствующие масштабный резистор и ключ первой пары ключей соединен с входом интегратора и через соответствующий ключ второй пары ключей с одной из обкладок интегрирующего конденсатора, другая обкладка которого, являющаяся выходом интегратора, через соответствующий ключ третьей пары ключей подключена к выходу соответствующего дифференциального усилителя, и через со. ответствующий ключ четвертой пары ключей - к входам двух запоминающих блоков, выходы которых соединены с инвертирующим входом соответствующего дифференциального усилителя, а инвертирующий вход кажцого цифференциального уситш лителя через соответствующий ключ пятой пары ключей соединен с шиной нулевого потенциала, отличающийся тем, что, с целью повышения точности интегрирования, в него введены два масштабных усилителя, ива пополнительных запоминакшшх блока н ключи, причем вход каждого аополнительного запсж1инаюшего блока через соогветствутоишй ключ шестой пары ключей соеоянен с выходом соответствующего оифференциальиого усилите ля, выход каждого дополнительного запоминающего блока через соответствующий ключ седьмой пары ключей соединен с инвертирующим входом этого же дифференциального усилителя и через соответствую ющий ключ восьмой пары ключе - с входом соответствующего масштабного усилителя, выход которого через со- отвётствуюший ключ девятой пары кгаочей подкшочен к неинвёртирующему входу дифференциального усилителя, а общий вывод ключа первой пары ключей и соответствующего масштабного резистора через соответствующий ключ десятой пары ключей связан с шиной нулевого потенциала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство ССОР N 193174, кл. 3 Об Q 7/08,, 1961. 2.Авторское свидетельство СССР № 686О37, кл. Q 06 q 7/18, 1979. 3.Авторское свидетельство СССР № 542200, кл. Q 06 Q 7/18, (прототип).

Авторы

Даты

1982-05-15—Публикация

1980-06-23—Подача