Изобретение относится к области контрольно-измерительной техники и цифровой вычислительной техники и может быть применено при производственном или эксплуатационном диагностировании логических схем. Известны устройства для ксУнтроля функционирования логических схем, содержащие блок управления, блок анализа, блоки ввода и входные и выходные блоки 1 и 2 . Наиболее близким по технической сущности к данному изобретению является устройство для контроля логи еских схем, содержащее последовательйо соединенные генератор импульсов, делитель частоты и первый блок управления, а также блок ввода, выход которого соединен с первыми входами первогоИ второго регистров, блок сравнения, соединенный первыми входами с выходами второго регистра вторыми входами - со входами устройства, а выходом- - со вторым входом первого блока управления, и блок регистрации 3. Недостатком известных устройств являются существенные потери времени на регис1рацита неисправностей. Целью изобретения является повышение быстродействия и надежности устройства. Поставленная цель достигается тем, что в предлагаемое устройство .введены дешифратор, счетчик, блок буферной памяти и три канала, состоящие из последовательно соединенных триггера, ключа и. второго блока управления, выходы второго блока управления первого канала подключены к первому входу блока регистрации и к первому входу блока буферной памяти, вторые входы которого соединены с выходами счетчика и с первыми входами дешифратора, соединенного вторым входом и выходами с первым выходом первого блока управления и с третьими входами блока сравнения соответственно, первый выход блока управления второго канала подключен к третьему входу блока буферной памяти, второй выход - ко входу счетчика, а второй вход - к выходу блока сравнения, первые выходы второго блока управления третьего канала подсоединены ко вторым входам первого и второго регистров, а второй выход - ко входу блока ввода, первый

и второй выходы блока буферной памяти соединены соответственно со вторым входом блока регистрации и с третьим входом первого блока управления, причем в каждом канале входы триггеров подключены ко вторым выходам первого блока управления, вто рые входы ключей - к соответствующим выходам частоты, а один из выходов вторых блоков управления к четвертым входам первого блока управления.

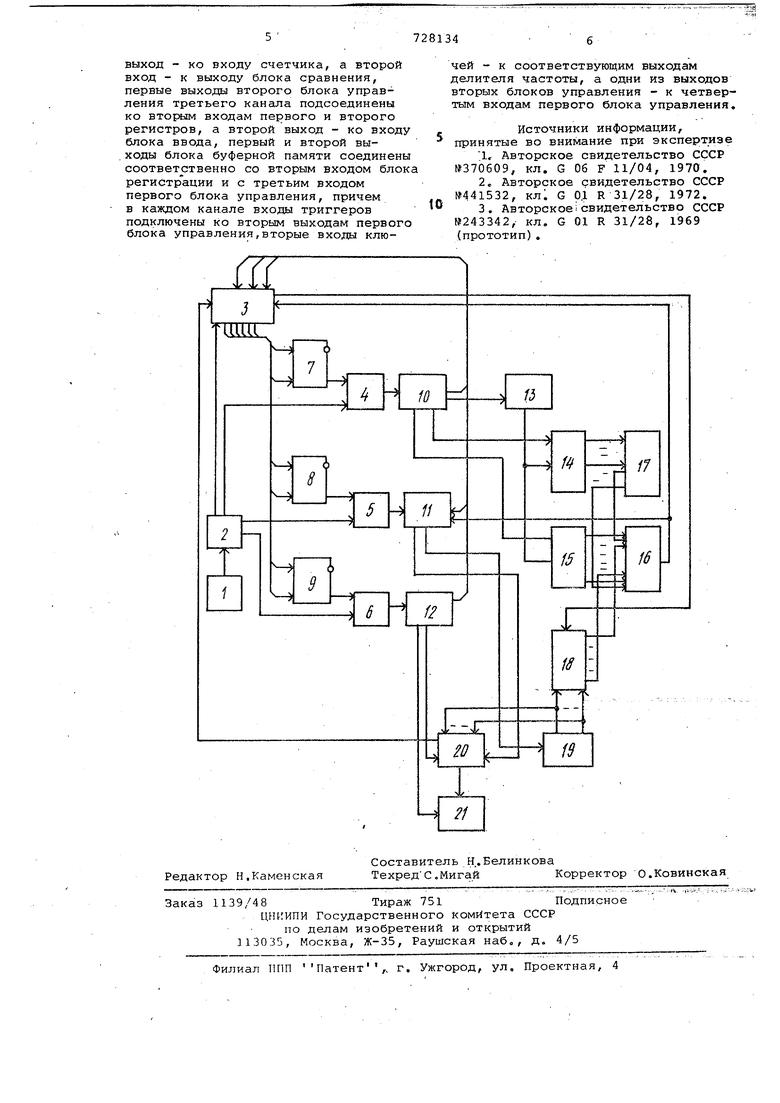

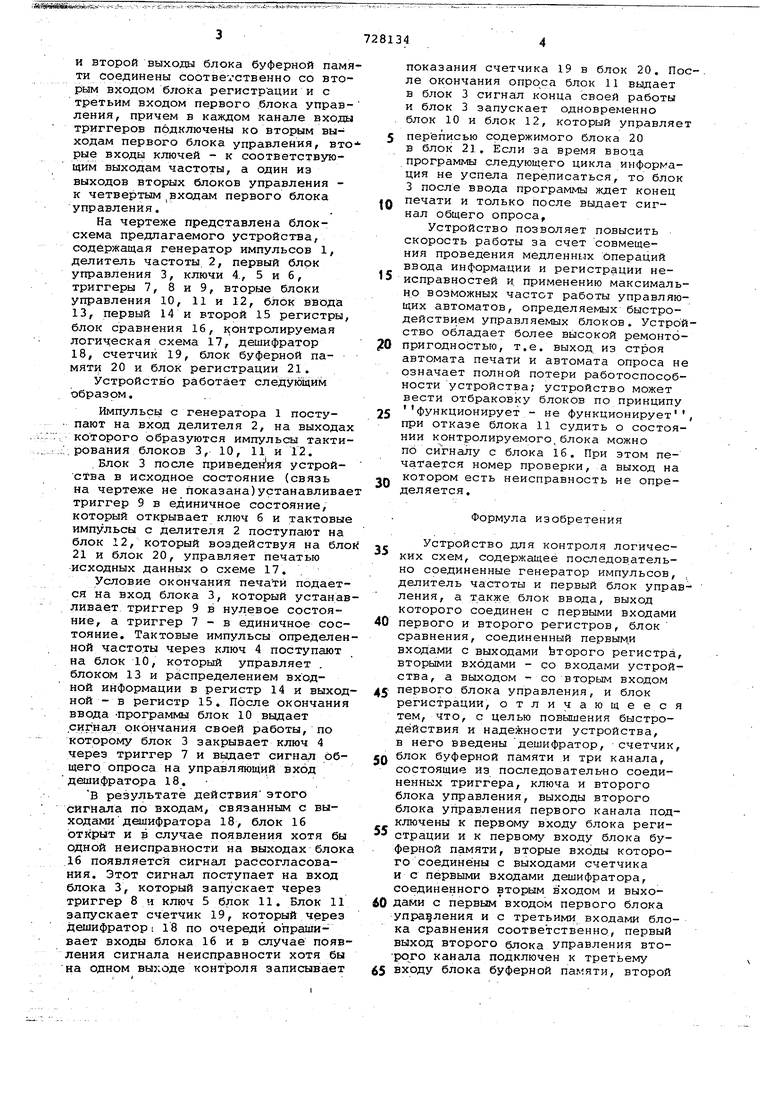

На чертеже представлена блоксхема предлагаемого устройства, содержащая генератор импульсов 1, делитель частоты 2, первый блок управления 3, ключи 4., 5 и б, триггеры 7, 8 и 9, вторые блоки управления 10, 11 и 12, блок ввода 13, первый 14 и второй 15 регистры, блок сравнения 16, к;онтралируемая логическая схема 17, дешифратор 18, счетчик 19, блок буферной памяти 20 и блок регистрации 21.

Устройство работает следующим образом.

Импульсы с генератора 1 поступают на вход делителя 2, на выходах которого образуются импульсы такти,рования блоков 3, 10, 11 и 12.

Блок 3 после приведения устройства в исходное состояние (связь на чертеже не показана)устанавливае триггер 9 в единичное состояние, который открывает ключ б и тактовые импульсы с делителя 2 поступают на блок 12, который воздействуя на бло 21 и блок 20, управляет печатью исходных данных о схеме 17. ,

Условие окончания печати подается на вход блока 3, который устанавливает триггер 9 в нулевое состояние, а триггер 7 - в единичное состояние. Тактовые импульсы определенной частоты через ключ 4 поступают на блок 10, который управляет . блоком 13 и распределением входной информации в регистр 14 и выходной - в регистр 15. После окончания ввода -программы блок 10 выдает сигнал окончания своей работы, по которому блок 3 закрывает ключ 4 через триггер 7 и выдает сигнал общего опроса на управляющий вход

дешифратора 18. .

В результате действия этого сигнала по входам, связанным с выходами дешифратора 18, блок 16 открыт и в случае появления хотя бы одной неисправности на выходах блок 16 появляется сигнал рассогласования. Этот сигнал поступает на вход блока 3, который запускает через триггер 8 и ключ 5 блок 11. Блок 11 запускает счетчик 19, который через дешифратор i 18 по очереди опрашивает входы блока 16 и в случае появления сигнала неисправности хотя бы

на одном выходе контроля записывает

показания счетчика 19 в блок 20. После окончания опроса блок 11 выдает в блок 3 сигнал конца своей работы и блок 3 запускает одновременно блок 10 и блок 12, который управляет переписью содержимого блока 20 в блок 21. Если за время ввода программы следующего цикла информация не успела переписаться, то блок 3 после ввода программы ждет конец

печати и только после выдает сигнал общего опроса.

Устройство позволяет повысить скорость работы за счет совмещения проведения медленных операций ввода информации и регистрации неисправностей и. применению максимально возможных частот работы управляющих автоматов, определяемых быстродействием управляемых блоков. Устройство обладает более высокой ремонтопригодностью, т.е. выход из строя автомата печати и автомата опроса не означает полной потери работоспособности устройства; устройство может вести отбраковку блоков по принципу

функционирует - не функционирует , при отказе блока 11 судить о состоянии контролируемого блока можно по сигналу с блока 16. При этом печатается номер проверки, а выход на

котором есть неисправность не определяется.

Формула изобретения

Устройство для контроля логических схем, содержащее последовательно соединенные генератор импульсов, делитель частоты и первый блок управления, а также блок ввода, выход которого соединен с первыми входами

0 первого и второго регистров, блок сравнения, соединенный первыми входами с выходами второго регистра, вторыми входами - со входами устройства, а выходом - со вторым входом

5- первого блока управления, и блок

регистрации, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, в него введены дешифратор, счетчик,

л блок буферной памяти и три канала, состоящие из последователь-но соединенных триггера, ключа и второго блока управления, выходы второго блока управления первого канала подключены к первому входу блока регистрации и к первому входу блока буферной памяти, вторые входы которого соединены с выходами счетчика и с первыми входами дешифратора, соединенного вторым входом и выхо 0 дами с первым входом первого блока управления и с третьими входами блока сравнения соответственно, первый выход второго блока управления второ го канала подключен к третьему

65 входу блока буферной памяти, второй

выход - ко входу счетчика, а второй вход - к выходу блока сравнения, первые выходы второго блока управения третьего канала подсоединены ко вторым входам первого и второго регистров, а второй выход - ко входу блока ввода, первый и второй выходы блока буферной памяти соединены соответственно со вторым входом блока регистрации и с третьим входом первого блока управления, причем в каждом канале входы триггеров подключены ко вторым выходам первого блока управления,вторые входы клю

чей - к соответствующим выходам делителя частоты, а одни из выходов вторых блоков управления - к четвертым входам первого блока управления.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР №370609, кл. G 06 F 11/04, 1970.

2,Авторское свидетельство СССР №441532, кл. G ОД R 31/28, 1972.

6

3.Авторское)свидетельство СССР №243342, кл, G 01 R 31/28, 1969 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1975 |

|

SU590757A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ СИЛОВЫХ УСТАНОВОК И ОПРЕДЕЛЕНИЯ ЭКСПЛУАТАЦИОННЫХ ПАРАМЕТРОВ ТРАНСПОРТНЫХ СРЕДСТВ | 2006 |

|

RU2308767C1 |

| Устройство для регистрации потоков подвижных объектов | 1984 |

|

SU1193704A1 |

| Устройство диагностирования скважинных штанговых насосов | 1988 |

|

SU1560799A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

Авторы

Даты

1980-04-15—Публикация

1976-08-26—Подача