Предлагаемое устройство относится к автоматическотлу управлению и может быть использовано в устройствах программного регулирования па раметров различных технологических процессов. Известно программное задающее устройство, содержащее блоки набора программы, каждый из которых состои из схемы задания скорости, схемы задания уровня и переключающей схем причем вход схемы задания скорости подключен к управляемому делителю частоты, выход схемы задания уровня подключен к реверсивному счетчику, один выход переключающей схемы соединен со схемами,задания скорости и уровня, другой - с переключающей схемой последующего блока набора программ, а входы переключающей схемы соединены, соответственно, с ходом схемы задания уровня и выходом переключающей схемы предьвдущего блока набора программы 1. Однако, применение управляемого делителя частоты существенно затру няет получение требуемой в современ ных условиях дискретности задания скорости изменения выходного сигнал Кроме того, устройство, построенное по такому принципу, содержит очень большое число схем переключения и блоков набора программ, равное числу участков задаваемой программы. Известно также прогргиимное задающее устройство, содержащее блок задания уровня и скорости, реверсивный счетчик со схемой совпадения, один вход которого соединен с выходом делителя частоты, другой - с выходом блока задания уровня, а выход подключен ко входу коммутатора, причем входблока задания уровня подсоединен к выходу коммутатора 2 . Это устройство содержит один блок набора программы, однако применение управляемого делителя частоты оно также не обеспечивает получение требуемой дискретности задания скорости изменения выходного сигнала, а. применение коммутатора приводит к снижению надежности устройства. Наиболее близким техническим решением к предлагаемому изобретению является программно-задающее устройство, содержащее блок постоянной пpoгpaмlvQ pyeмoй памяти, выход которого соединен с входом основного блока оперативной памяти, блок сравнения, первый вход которого соединен с первым выходом основного блока оперативной памяти, блок задания программы, выход которого соединен с входом блока постоянной программи руемой памяти и блок управления 3

Недостатком устройства является то, ЧТ.О--ОНО содержит управляемый генератор частоты и цифроаналоговый преобразователь, не обеспечивающие получения выходного сигнала с точностью, удовлетворяющей требованиям промышленности, а, следовательно, реализация программных задающих устройств, построенных по подобной структуре,является недостаточно рациональной.

Целью изобретения является повышение точности и надежности устройства.

Это достигается тем, что - в устройствовведены дополнительный (блок оперативной памяти и блок алгебраического суммирования, -причем второй выход основного блока оперативной памяти соединен с первым входом блока алгебраического суммирования, второй вход которого соединен с выходом дополнительного блока оперативной памяти, выход блока алгебраического суммирования соединен с входом дополнительного блока оперативной памяти и со вторым входом блока сравнения, выход которого соединен с входом блока управления.

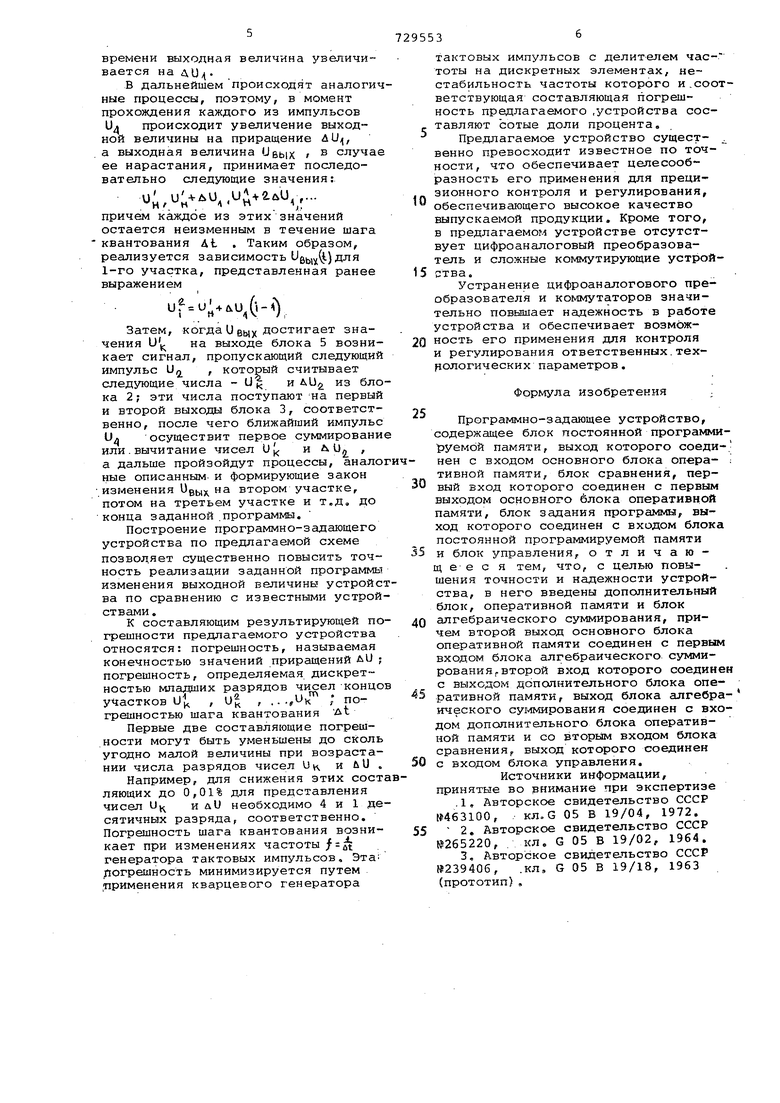

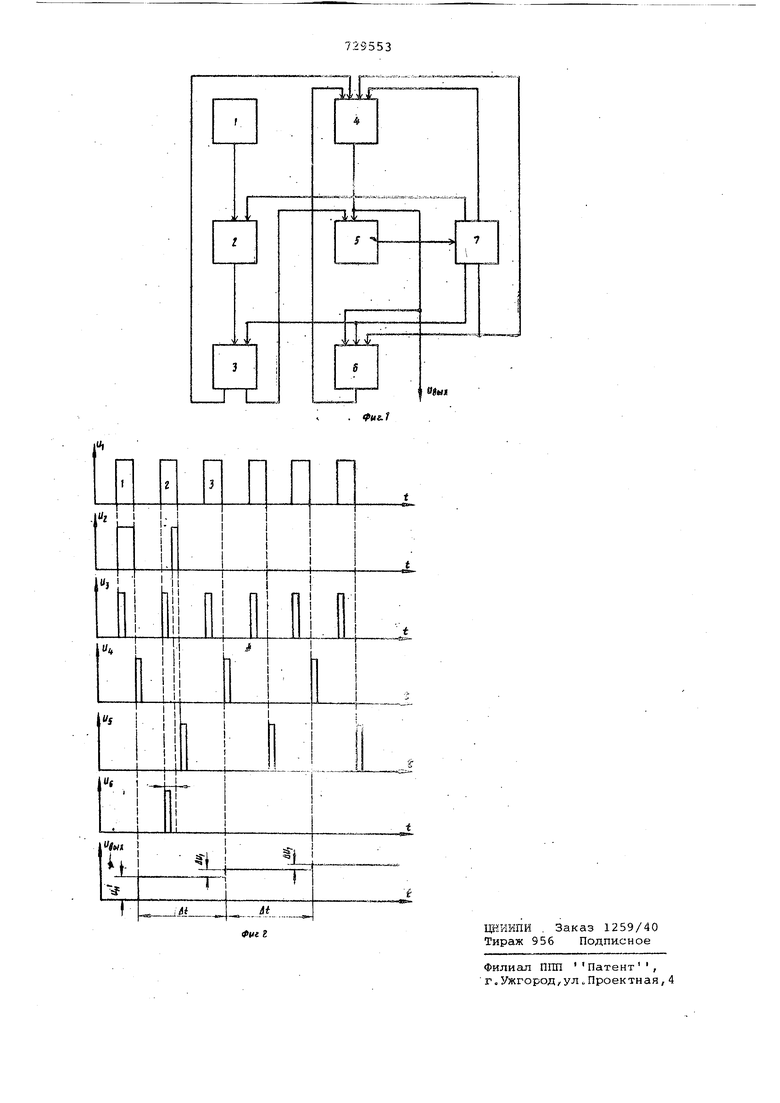

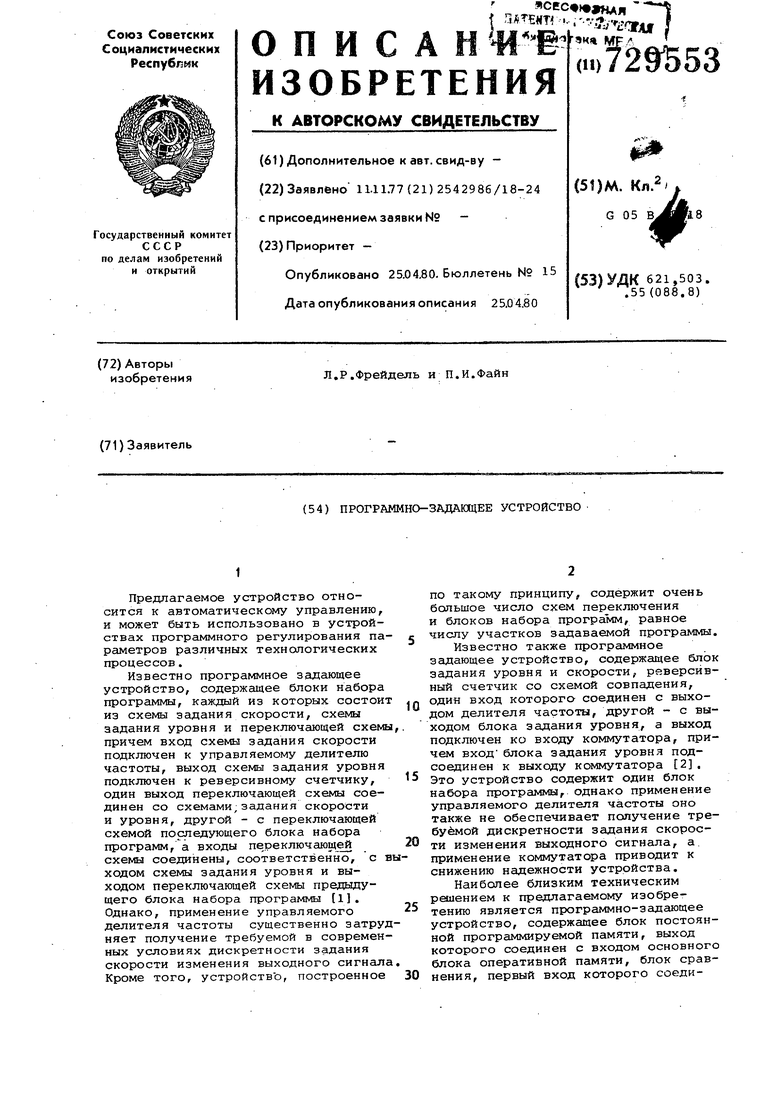

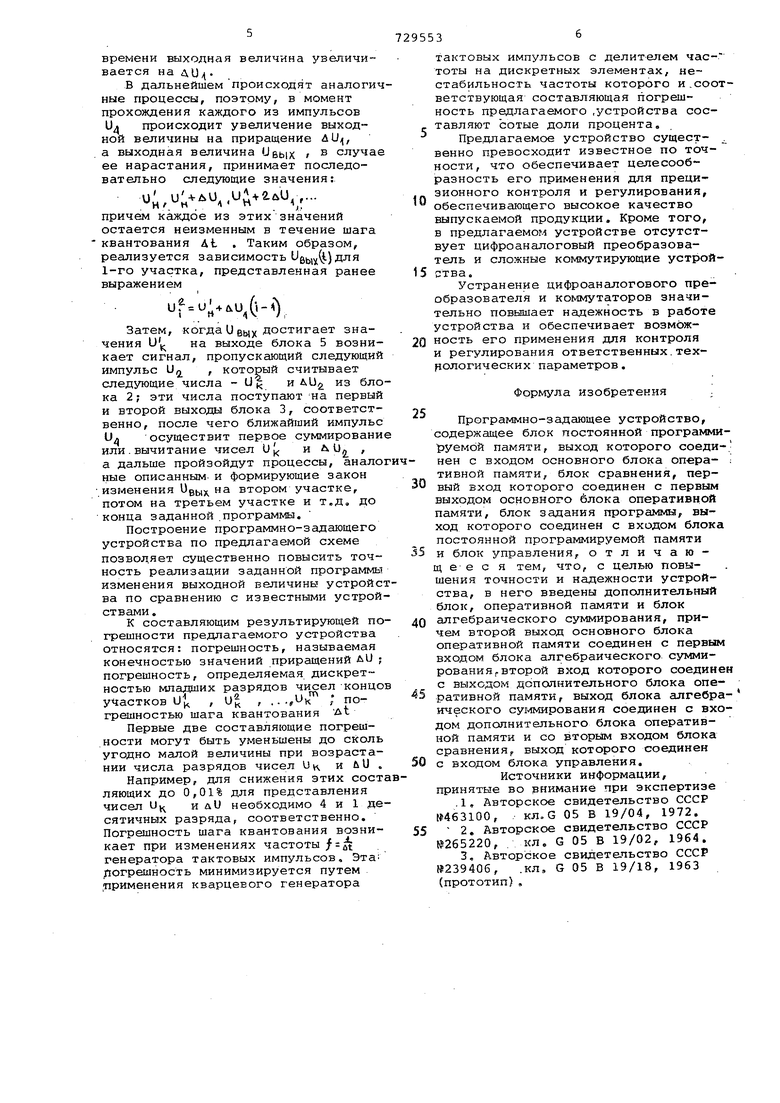

На фиг. 1 представлена функционалная схема программно-задающего устройства; на фиг. 2 диаграммы импульсов. Устройство содержит блок задания программы 1, блок постоянно программируемой памяти 2,основной блок оперативной памяти 3, блок алгебраического суммирования 4, блок сравнения 5, дополнительный блок оп ративной памяти 6 и блок управления

Устройство работает следующим образом.

После включения устройства в сет из тактовых импульсов U блока 7 фомируются импульсы Ug , поступающие на управляюгций вход блока 2.

Каждый импульс команду на считывание чисел, хранимых в блоке 2, а адреса этих чисел определтатся koличecтзpм. импульсов поступивших на управляющий вход блока 2 с, момента включения устройства Первый импульс U j считывает первое число, находящееся в блоке 2 - первого участка Ми и вводит его в блок оперативной памяти 3, Число jj{( при этом возникает на первсяй и втором выходах блока 3.

На задних фронтах импульсов U, формируются следующие поочередно импульсы Уд и Ug f поступающие с четвертого и второго выходов блока 7 на управляющие входы блоков 6, 4 и 6,3, соответственно.

Первый импульс U дает команду алгебраического суммирования числа ин на втором выходе блока 3 с числом на выходе блока б,

Так как в рассматриваемый момент времени запоминающие элементы (например, регистры) блока б не заполненЫр на выходе блока алгебраического сумгч ирования возникает число ин

Блок 7 содержит обычную триггерную Схему запрета, которая после поступления каждого импульса U на управл-яющий вход блока 2 запрещ ВТ прохождение -следующих импульсов ДО появления . импульса на выходе блока 5, Непосредственно после включения устройства схема запрета устанавливается в открытое состояние,

К моменту появления второго импульса и на третьем управляющем входе блока 4 возникает импульс U, который дает ксманду на передачу выходйого числа блока 4 на второй вход блока 5.

Вевязи с тем, что в расс матривамый момент времени на первый и второй входы блока 5 поступают одинаковые числа, а именно Оц , на выходе блока 5 появляется импульс Ug, который через Временную задержкуЧд возвращает триггерную схему запрета в блоке 3 в исходное состояние, разрешающее прохождение еще одного импульса и .

„В результате поступления второго импульса и2 на управляющий вход блока 2 происходит считывание следующих чисел и к и ди,( , которые поступают на первый и второй выходы блока 3,соответственно.

Далее,, в момент окончания второг импульса и 2 возникает первый импульс Ug f который обеспечивает пердачу выходного числа блока 4 в блок бе одновременным запретом считывания информации со второго выхода блока 3, В результате на выходе блока оперативной памяти б возникает число Uy ,

Далее, в момент появления третьего тактового импульса Уд возникает третий импульс УЗ и вновь .происходит сравнение кодов с выходом блока 4 и 3. Однако теперь на первом выходе блока 3 существует число UK - ордината конца первого участка, и, так как Uj н г совпадени кодов не происходит, импульс Ug не появляется и, следовательно, импульсы и. не проходят,

Затем, в результате появления второго импульса U происходит либо суммирование числа Уи с числом & и , либо вычитание этого же числа из UH в зависимости от значения знакового разряда (О или 1) числа ии . В этот момент времени выходная величина увеличивается на дУд В дальнейшем происходят аналоги ные процессы, поэтому, в момент прохождения каждого из импульсов происходит увеличение выходной величины на приращение ДУ, . а выходная величина / в случа ее нарастания, принимает последовательно следующие значения: ,.;,.H vпричем каждое из этих значений остается неизменным в течение шага квантования At . Таким образом, реализуется зависимость Ugbiyll) для 1-го участка, представленная ранее выражением Затем, когда и вух значения U на выходе блока 5 возни кает сигнал, пропускающий следующи импульс и2 , который считывает следующие числа - U и AU из бл ка 2; эти числа поступают на первы и второй выходы блока 3, соответст венно, после чего ближайший импуль и осуществит первое суммирован или . вычитание чисел Uj и л U , а дальше произойдут процессы, анал ные описанным и формирующие закон изменения на втором участке, потом на третьем участке и т.д. до конца заданной .программы. Построение программно-задающего устройства по предлагаемой схеме позволяет существенно повысить точность реализации заданной программы изменения выходной величины устройс ва по сравнению с известными устрой ствами. К составляющим результирующей по грешности предлагаемого устройства относятся: погрешность, называемая конечностью значений приращений ди погрешность, определяемая дискретностью младших разрядов чисел концо участков и ц .. .,UK ; ПОгрешностью шага квантования At Первые две составляющие погрешности могут быть уменьшены до сколь угодно малой величины при возрастании числа разрядов чисел UK и MJ Например, для снижения этих сост ляющих до 0,01% для представления чисел Uj и aU необходимо 4 и 1 де сятичных разряда, соответственно. Погрешность шага квантования возникает при изменениях частоты fгенератора тактовых импульсов. Эта: погрешность минимизируется путем применения кварцевого генератора тактовых импульсов с делителем частоты на дискретных элементах, нестабильность частоты которого и,соответствующая составляющая погрешность предлагаемого .устройства составляют сотые доли процента. Предлагаемое устройство существенно превосходит известное по точности, что обеспечивает целесообразность его применения для прецизионного контроля и регулирования, обеспечивающего высокое качество выпускаемой продукции. Кроме того, в предлагаемом устройстве отсутствует цифроаналоговый преобразователь и сложные коммутирующие устройства. Устранение цифроаналогового преобразователя и коммутаторов значительно повышает надежность в работе устройства и обеспечивает возможность его применения для контроля и регулирования ответственных.техрологических параметров. Формула изобретения ; Программно-задающее устройство, содержащее блок постоянной программируемой памяти, выход которого соедийен с входом основного блока опера- . тивной памяти, блок сравнения, первый вход которого соединен с первым выходом основного блока оперативной памяти, блок задания программы, выход которого соединен с входом блока постоянной программируемой памяти и блок управления, отличающ е- е с я тем, что, с целью повышения точности и надежности устройства, в него введены дополнительный блок, оперативной памяти и блок алгебраического суммирования, причем второй выход основного блока оперативной памяти соединен с первым входом блока алгебраического суммирования второй вход которого соединен с выходом дополнительного блока оперативной памяти, выход блока алгебраического су1.1мирования соединен с входом дополнительного блока оперативной памяти и со вторым входом блока сравнения, выход которого соединен с входом блока управления. Источники информации, принятые во внимание при экспертизе .1, Авторское свидетельство СССР №463100, кл.С 05 В 19/04, 1972, - 2. Авторское свидетельство СССР №265220, . кл, G 05 В 19/02, 1964, 3, Авторское свидетельство СССР №239406, .кл, G 05 В 19/18, 1963 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР,v....c;;i-^3'</^;. •-..;..;; ; ,'i;.'•;•::[•;'"Н^ ^у-;;--, •i;'|,_. ;-:i< ^. | 1971 |

|

SU302722A1 |

| Устройство для программного регулирования | 1979 |

|

SU930263A2 |

| Система управления вибростендом | 1985 |

|

SU1305649A1 |

| Цифровое устройство для автоматического управления движением шахтной подъемной машины | 1978 |

|

SU765173A1 |

| Устройство для задания программы | 1972 |

|

SU463100A1 |

| Устройство для измерения характеристик синусоидального сигнала | 1985 |

|

SU1307366A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Пневматическое программное устройство | 1978 |

|

SU830317A1 |

| Устройство для программного управления | 1978 |

|

SU824146A2 |

| Программное задающее устройство | 1976 |

|

SU693337A1 |

Авторы

Даты

1980-04-25—Публикация

1977-11-11—Подача