1. 130

Изобретение относится к цифровой электроизмерительной технике,а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов.

Цель изобретения - расширение функциональньи возможностей за счет измерения частоты и фазы синусоидального сигнала, повышение точности и быстродействия измерения, расширение частотного диапазона.

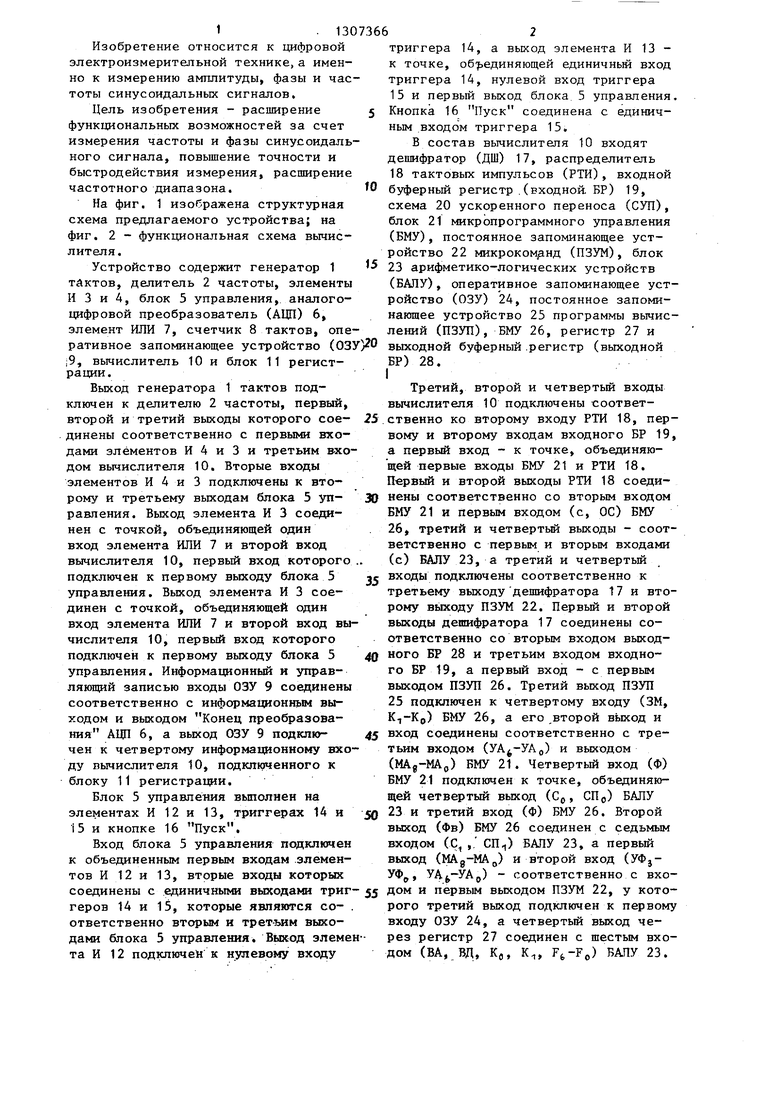

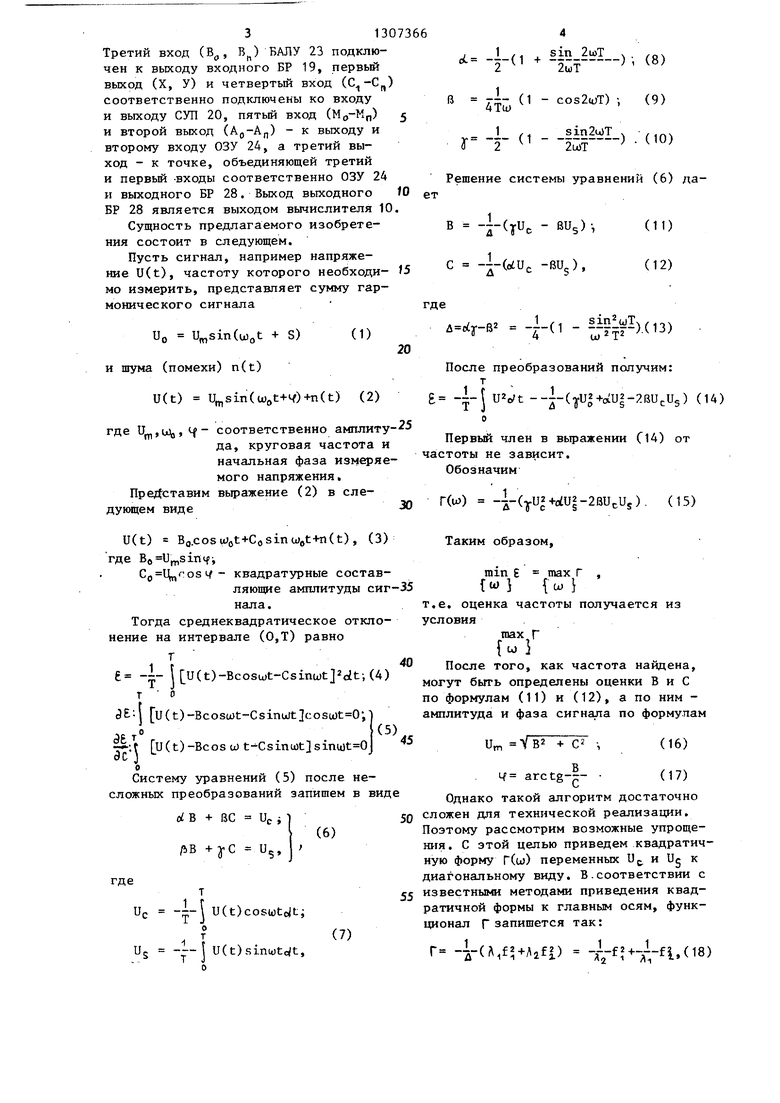

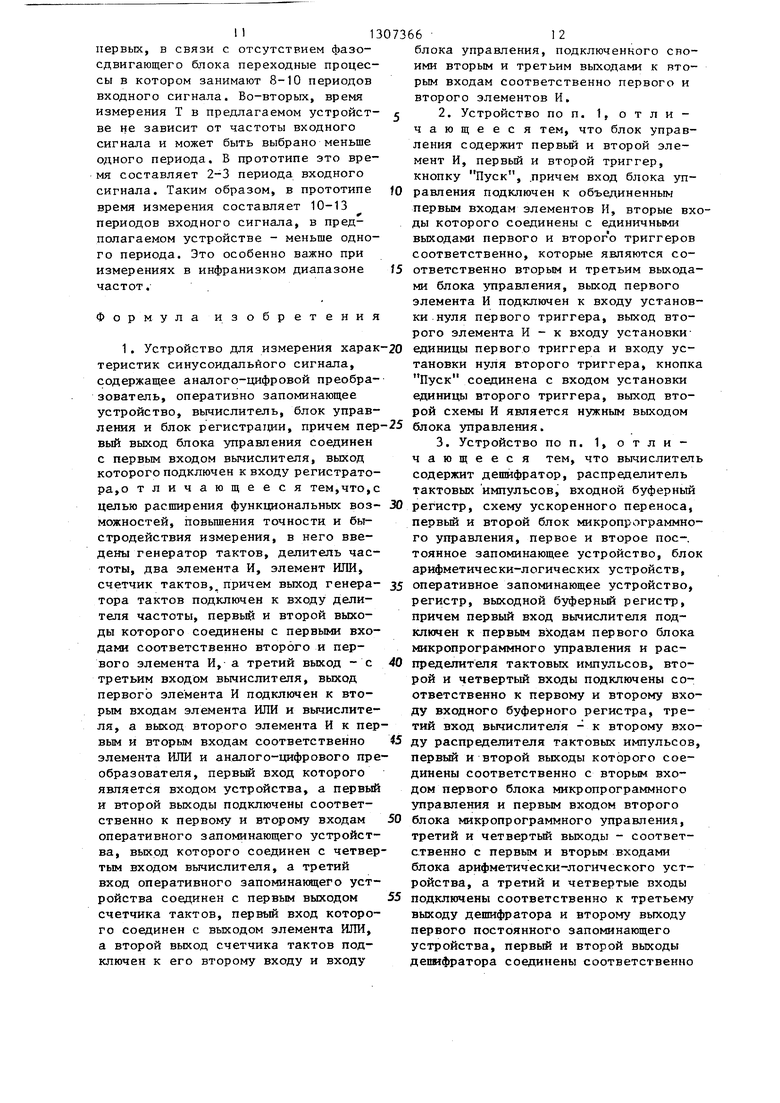

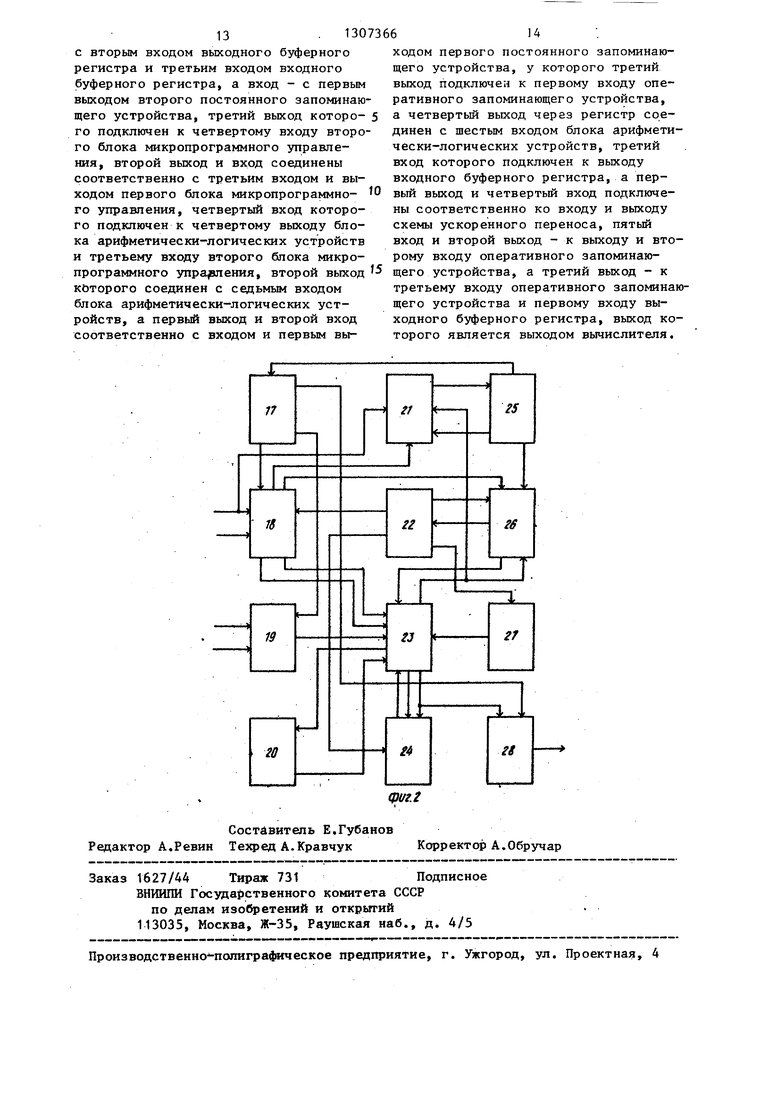

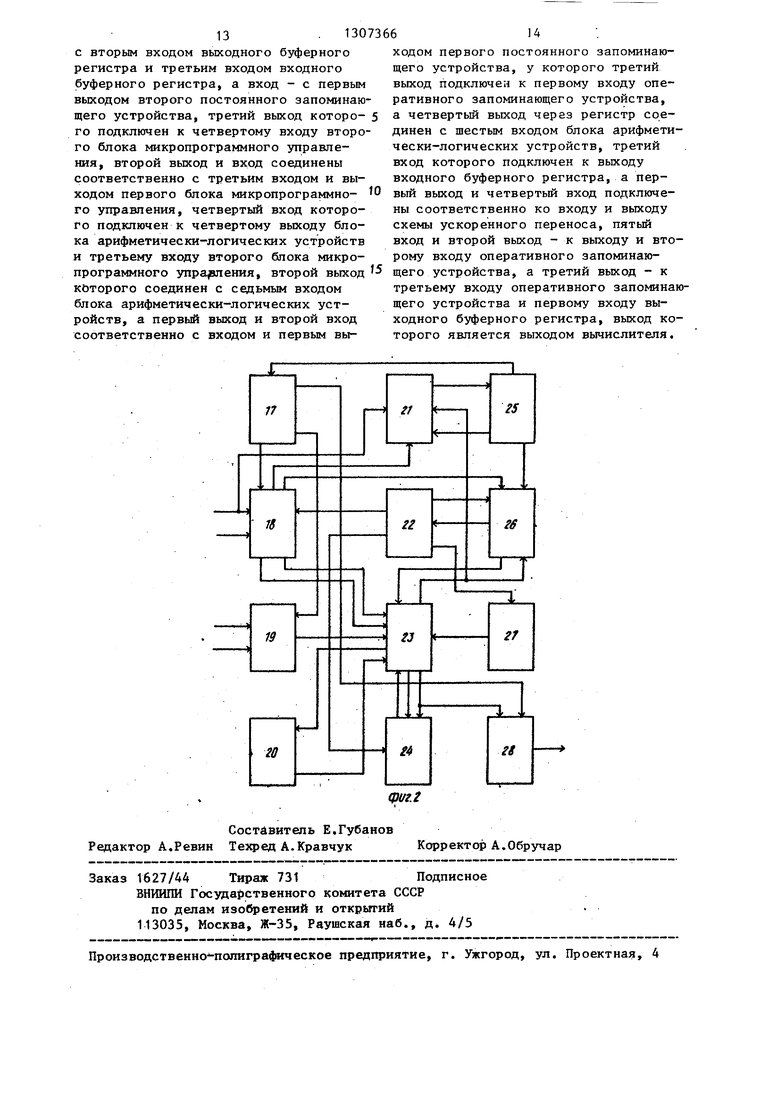

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема вычислителя.

Устройство содержит генератор 1

ТАКТОВ, делитель 2 частоты, элементы И 3 и 4, блок 5 управления, аналого- цифровой преобразователь (АЦП) 6, элемент ИЛИ 7, счетчик 8 тактов, oneВ состав вычислителя 10 входят дешифратор (ДШ) 17, распределитель 18 тактовых импульсов (РТИ), входной буферный регистр .(входной ВР) 19, схема 20 ускоренного переноса (СУП), блок 21 микропрограммного управления (БМУ), постоянное запоминающее устройство 22 микрокоманд (ПЗУМ), блок 5 23 арифметико-логических устройств (БАЛУ), оперативное запоминающее устройство (ОЗУ) 24, постоянное запоминающее устройство 25 программы вычислений (ПЗУП), БМУ 26, регистр 27 и

Третий, второй и четвертый входы вычислителя 10 подключены соответративное запоминающее устройство (ОЗУ) выходной буферный .регистр (выходной

;9, вычислитель 10 и блок 11 регист- БР) 28. рации.I

Выход генератора 1 тактов подключен к делителю 2 частоты, первый, второй и третий выходы которого сое- 25 ственно ко второму входу РТИ 18, пер- динены соответственно с первыми вхо- вому и второму входам входного БР 19, дами элементов И 4 и 3 и третьим вхо- а первый вход - к точке, объединяющей первые входы БМУ 21 и РТИ 18. Первый и второй выходы РТИ 18 соеди- 30 йены соответственно со вторым входом БМУ 21 и Первым входом (с, ОС) БМУ 26, третий и четвертьй выходы - соответственно с первым и вторым входами (с) Б;АЛУ 23, а третий и четвертый ас входы подключены соответственно к третьему выходу дешифратора 17 и второму выходу ПЗУМ 22. Первый и второй выходы депшфратора 17 соединены соответственно со вторым входом выход- 40 ного БР 28 и третьим входом входного Б 19, а первый вход - с первым выходом ПЗУП 26. Третий выход ПЗУП 25 подключен к четвертому входу (ЗМ, KT-KJ,) БМУ 26, а его второй вькод и 45 вход соединены соответственно с третьим входом () и выходом (MAg-MAp) БМУ 21. Четвертый вход (Ф) БМУ 21 подключен к точке, объединяющей четвертый выход (С, СП,,) БАЛУ 50 23 и третий вход (Ф) БМУ 26. Второй выход (Фв) БМУ 26 соединен с седьмым входом (С ,. СП) БАЛУ 23, а первый выход (MAg-MAp) и второй вход ( УФ, ) - соответственно с вхо- соединены с единичными выходами триг- 55 Дом первым выходом ПЗУМ 22, у кото- геров 14 и 15, которые являются со- . рого третий выход подключен к первому ответственно вторым и трет-ьим выхо- входу ОЗУ 24, а четвертый выход че- дами блока 5 управления. Выход элемен- рез регистр 27 соединен с шестым входом вычислителя 10. Вторые входы элементов И 4 и 3 подключены к второму и третьему выходам блока 5 управления. Выход элемента И 3 соединен с точкой, объединяющей один вход элемента ИЛИ 7 и второй вход вычислителя 10, первый вход которого подключен к первому выходу блока 5 управления. Выход элемента И 3 соединен с точкой, объединяющей один вход элемента ИЛИ 7 и второй вход вычислителя 10, первый вход которого подключен к первому выходу блока 5 управления. Информационный и управляющий записью входы ОЗУ 9 соединены соответственно с информационньм выходом и выходом Конец преобразования АЦП 6, а выход ОЗУ 9 подключен к четвертому информационному входу вычислителя 10, подключенного к блоку 11 регистрации.

Блок 5 управления вьшолнен на элементах И 12 и 13, триггерах 14 и 15 и кнопке 16 Пуск.

Вход блока 5 управления подключен к объединенным первым входам элементов И 12 и 13, вторые входы которых

дом (ВА, ВД, Kfl, К, Ffe-F) ВАПУ 23.

та И 12 подключен к нулевому входу

триггера 14, а выход элемента И 13 - к точке, об единяющей единичный вход триггера 14, нулевой вход триггера 15 и первый выход блока 5 управления. Кнопка 16 Пуск соединена с единичным входом триггера 15.

В состав вычислителя 10 входят дешифратор (ДШ) 17, распределитель 18 тактовых импульсов (РТИ), входной буферный регистр .(входной ВР) 19, схема 20 ускоренного переноса (СУП), блок 21 микропрограммного управления (БМУ), постоянное запоминающее устройство 22 микрокоманд (ПЗУМ), блок 23 арифметико-логических устройств (БАЛУ), оперативное запоминающее устройство (ОЗУ) 24, постоянное запоминающее устройство 25 программы вычислений (ПЗУП), БМУ 26, регистр 27 и

выходной буферный .регистр (выходной

Третий, второй и четвертый входы вычислителя 10 подключены соответственно ко второму входу РТИ 18, пер вому и второму входам входного БР 19 а первый вход - к точке, объединяющей первые входы БМУ 21 и РТИ 18. Первый и второй выходы РТИ 18 соеди- йены соответственно со вторым входом БМУ 21 и Первым входом (с, ОС) БМУ 26, третий и четвертьй выходы - соот ветственно с первым и вторым входами (с) Б;АЛУ 23, а третий и четвертый входы подключены соответственно к третьему выходу дешифратора 17 и вто рому выходу ПЗУМ 22. Первый и второй выходы депшфратора 17 соединены соответственно со вторым входом выход- ного БР 28 и третьим входом входного Б 19, а первый вход - с первым выходом ПЗУП 26. Третий выход ПЗУП 25 подключен к четвертому входу (ЗМ, KT-KJ,) БМУ 26, а его второй вькод и вход соединены соответственно с третьим входом () и выходом (MAg-MAp) БМУ 21. Четвертый вход (Ф) БМУ 21 подключен к точке, объединяющей четвертый выход (С, СП,,) БАЛУ 23 и третий вход (Ф) БМУ 26. Второй выход (Фв) БМУ 26 соединен с седьмым входом (С ,. СП) БАЛУ 23, а первый выход (MAg-MAp) и второй вход ( УФ, ) - соответственно с вхо Дом первым выходом ПЗУМ 22, у кото рого третий выход подключен к первом входу ОЗУ 24, а четвертый выход че- рез регистр 27 соединен с шестым вхо

ственно ко второму входу РТИ 18, пер- вому и второму входам входного БР 19 а первый вход - к точке, объединяющей первые входы БМУ 21 и РТИ 18. Первый и второй выходы РТИ 18 соеди- йены соответственно со вторым входом БМУ 21 и Первым входом (с, ОС) БМУ 26, третий и четвертьй выходы - соответственно с первым и вторым входами (с) Б;АЛУ 23, а третий и четвертый входы подключены соответственно к третьему выходу дешифратора 17 и второму выходу ПЗУМ 22. Первый и второй выходы депшфратора 17 соединены соответственно со вторым входом выход- ного БР 28 и третьим входом входного Б 19, а первый вход - с первым выходом ПЗУП 26. Третий выход ПЗУП 25 подключен к четвертому входу (ЗМ, KT-KJ,) БМУ 26, а его второй вькод и вход соединены соответственно с третьим входом () и выходом (MAg-MAp) БМУ 21. Четвертый вход (Ф) БМУ 21 подключен к точке, объединяющей четвертый выход (С, СП,,) БАЛУ 23 и третий вход (Ф) БМУ 26. Второй выход (Фв) БМУ 26 соединен с седьмым входом (С ,. СП) БАЛУ 23, а первый выход (MAg-MAp) и второй вход ( УФ, ) - соответственно с вхо- Дом первым выходом ПЗУМ 22, у кото- рого третий выход подключен к первому входу ОЗУ 24, а четвертый выход че- рез регистр 27 соединен с шестым входом (ВА, ВД, Kfl, К, Ffe-F) ВАПУ 23.

313073664

Третий вход (В, В1) БАЛУ 23 подклю- ,i. -i E Il-Zi

чен к выходу входного БР 19, первый 2 2ШТ

выход (X, У) и четвертый вход ()

соответственно подключены ко входу в -1- ( - cos2tuT) -, (9) и выходу СУП 20, пятый вход (Mt,-Mf,) 5

и второй выход (АО-А„) - к выходу и 1 ,-.

второму входу ОЗУ 24, а третий вы- У 2 2ШТ

ход - к точке, объединяющей третий

и первый -входы соответственно ОЗУ 24 Решение системы уравнений (6) даи выходного БР 28. Выход выходного 10 g

БР 28 является выходом вычислителя 10.

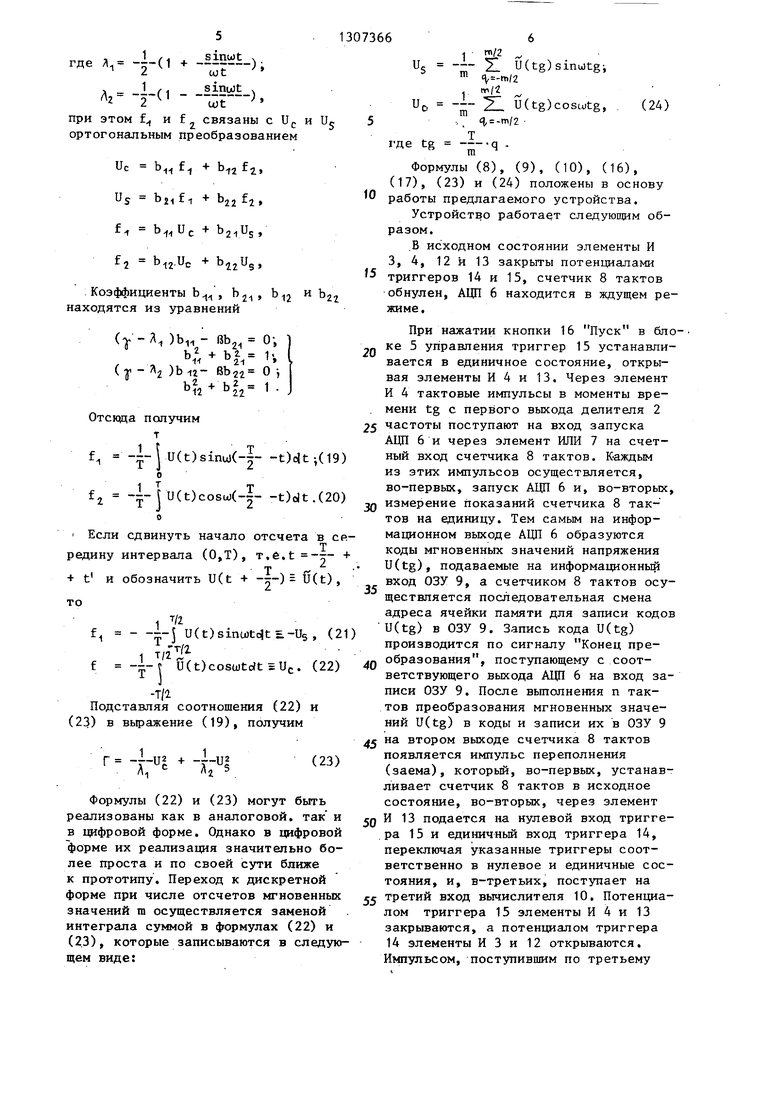

Сущность предлагаемого изобрете- в ---(ги. - BUe), (11) имя состоит в следующем.

Пусть сигнал, например напряже-1

ние U(t), частоту которого необходи- 5 д Ug), (12) МО измерить, представляет сумму гармонического сигнала -где

DO (u)ot + S) (1) (1 - ).( 13)

20

и шума (помехи) n(t)После преобразований получим:

т

U(t) (aj,t+4)+n(t) (2) -I-J uVt --(yU oiU|-.BU(.Us) (14)

,,0

где и ,u)L.,tf- соответственно амплиту-

да, круговая частота и Первый член в выражении Cl4) от

начальная фаза измеряв- частоты не зависит.

мого напряжения.Обозначим

Представим выражение (2) в следующем виде

30 r(w) -i-(yU2+oiU2-2SUeUs). (15)

30 r(w) -i-(yU2+oiU2-2SUeUs). (15)

U(t) BQ.cosuJot+Cosinwet+n(t), (3)Таким образом,

где Bo U sirHfi.

,,гоз1/- квадратурные состав-min max Г ,

ляющие амплитуды сиг-35{ { ш J

нала.т.е. оценка частоты получается из

Тогда среднеквадратическое откло-условия

нение на интервале (О,Т) равноmax Г

Т I

с 1 f Г1ТС.-Л г, 13 1 // После того, как частота найдена,

6 --- ru(t)-Bcosu)t-Csinu)t 2cit; (4)., ,, ,,

Т J - могут быть определены оценки В и С

по формулам (11) и (12), а по ним U(t)-Bcosu)t-CsinuJt cosu), jамплитуда и фаза сигнала по формулам

u(t)-Bcosu)t-Csinu)t siniot OJ U В2 ч- С -, (16)

В

Систему уравнений (5) после не- arctg-r- (17)

сложных преобразований запишем в виде .. алгоритм достаточно

50сложен для технической реализации.

(6)Поэтому рассмотрим возможные упрощения . С зтой целью приведем квадратичную форму Г(ы) переменных 1), и Ug к

гдедиагональному виду. В.соответствии с

т 55известными методами приведения квадUp --- U(t)cosiot(Jt;ратичной формы к главным осям, функ0ционал Г запишется так:

Us -J-- U(t),г -V(A,) T-f n--fi.(18)

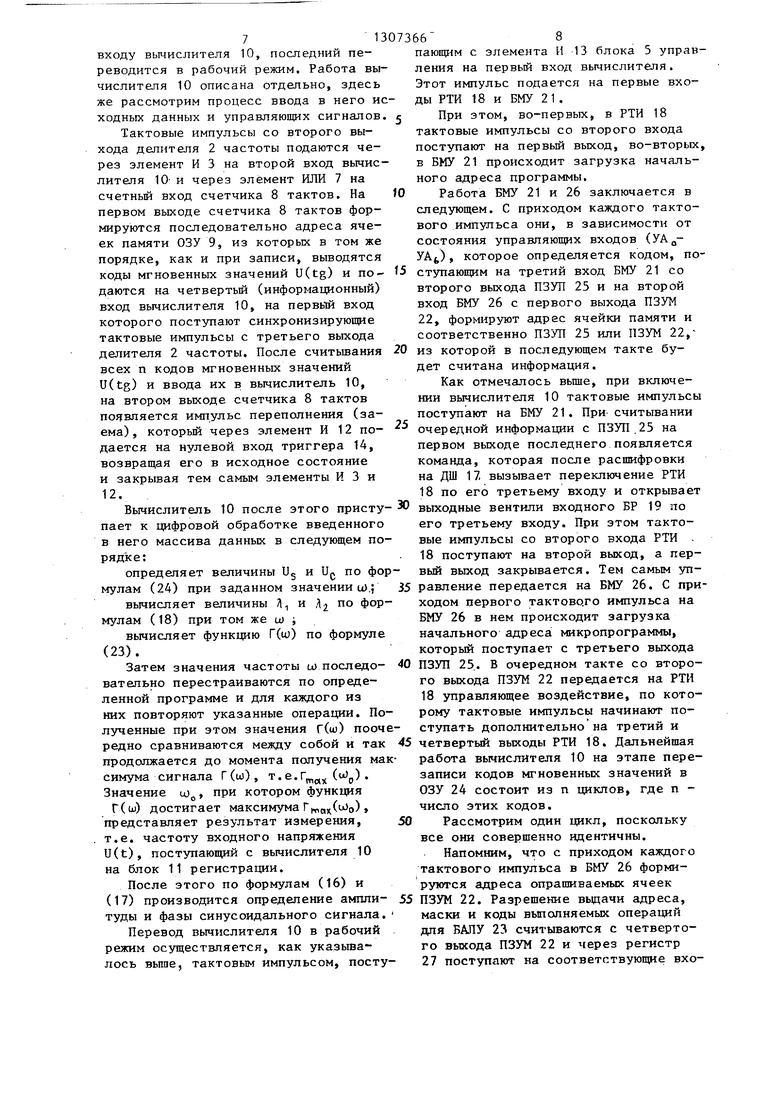

при этом f и f J, связаны с U и U ортогональным преобразованием

Uc b,, f -t- ,

Uy - Ъц f 1 + bjj fj ,

b,,U

с + b2,Us,

f,

b,2.Uc

-Ь ,

Коэффициенты b

-1-t

находятся из уравнений

2-t

Отснзда получим

т

f, U(t)sinuj(-|- -t)c{t-,(19)

-ru(t)cosuj( о

Если сдвинуть начало редину интервала (О,Т),

+ t и обозначить U(t +

то

т/2

- --5 U(t)sinwtolt -U5, (21)

- m

т,{1«

1

U(t)cosu)toft Uc. (22)

-Т/1

Подставляя соотношения (22) и (23) в выражение (19), получим

(23)

Формулы (22) и (23) могут быть реализованы как в аналоговой, так и в цифровой форме. Однако в цифровой форме их реализация значительно более проста и по своей сути ближе к прототипу. Переход к дискретной форме при числе отсчетов мгновенных значений m осуществляется заменой интеграла суммой в формулах (22) и (23), которые записываются в следующем виде:

Формулы (8), (9), (10), (16), (17), (23) и (24) положены в основу

работы предлагаемого устройства.

Устройство работает следующим образом.

.В исходном состоянии элементы И 3, 4, 12 и 13 закрыты потенциалами триггеров 14 и 15, счетчик 8 тактов обнулен, АЦП 6 находится в ждущем режиме.

При нажатии кнопки 16 Пуск в бло- ке 5 управления триггер 15 устанавливается в единичное состояние, открывая элементы И 4 и 13. Через элемент И 4 тактовые импульсы в моменты вре- мени tg с первого выхода делителя 2

частоты поступают на вход запуска АЦП 6 и через элемент ИЛИ 7 на счетный вход счетчика 8 тактов. Каждым из этих импульсов осуществляется, во-первых, запуск АЦП 6 и, во-вторых,

измерение показаний счетчика 8 так- тов на единицу. Тем самым на информационном выходе АЦП 6 образуются коды мгновенных значений напряжения U(tg), подаваемые на информационный вход ОЗУ 9, а счетчиком 8 тактов осуществляется последовательная смена адреса ячейки памяти для записи кодов U(tg) в ОЗУ 9. Запись кода U(tg) производится по сигналу Конец преобразования, поступающему с соответствующего выхода АЦП 6 на вход записи ОЗУ 9. После вьтолнения п тактов преобразования мгновенных значений U(tg) в коды и записи их в ОЗУ 9

на втором выходе счетчика 8 тактов появляется импульс переполнения (заема), который, во-первых, устанавливает счетчик 8 тактов в исходное состояние, во-вторых, через элемент И 13 подается на нулевой вход триггера 15 и единичный вход триггера 14, переключая указанные триггеры соответственно в нулевое и единичные состояния, и, в-третьих, поступает на

третий вход вычислителя 10. Потенциалом триггера 15 элементы И 4 и 13 закрываются, а потенциалом триггера 14 элементы И 3 и 12 открываются. Импульсом, поступившим по третьему

входу вычислителя 10, последний переводится в рабочий режим. Работа вычислителя 10 описана отдельно, здесь же рассмотрим процесс ввода в него исходных данных и управляющих сигналов.

Тактовые импульсы со второго выхода делителя 2 частоты подаются через элемент И 3 на второй вход вычислителя 10- и через элемент ИЛИ 7 на счетньй вход счетчика 8 тактов. На первом выходе счетчика 8 тактов формируются последовательно адреса ячеек памяти ОЗУ 9, из которых в том же порядке, как и при записи, выводятся

10

пающим с элемента И 13 блока 5 управления на первый вход вычислителя. Этот импульс подается на первые входы РТИ 18 и БМУ 21.

При этом, во-первых, в РТИ 18 тактовые импульсы со второго входа поступают на первый выход, во-вторых, в БМУ 21 происходит загрузка начального адреса программы.

Работа БМУ 21 и 26 заключается в следующем. С приходом каждого тактового импульса они, в зависимости от состояния управляющих входов ( УА), которое определяется кодом, по- коды мгновенных значений U(tg) и по- 15 ступающим на третий вход БМУ 21 со даются на четвертьй (информационный) второго выхода ПЗУП 25 и на второй

вход БМУ 26 с первого выхода ПЗУМ 22, формируют адрес ячейки памяти и соответственно ПЗУП 25 или ПЗУМ 22, 20 из которой в последующем такте будет считана информация.

Как отмечалось выше, при включении вычислителя 10 тактовые импульсы поступают на БМУ 21. При считывании ема), который через элемент И 12 по- очередной информации с ПЗУП.25 на дается на нулевой вход триггера 14, первом выходе последнего появляется возвращая его в исходное состояние команда, которая после расщифровки

на ДШ 17, вызывает переключение РТИ 18 по его третьему входу и открывает Вычислитель 10 после этого присту- выходные вентили входного БР 19 по пает к цифровой обработке введенного его третьему входу. При этом такто- в него массива данных в следующем по- вые импульсы со второго входа РТИ . рядке:.18 поступают на второй выход, а перопредепяет величины Ug и Ujv по фор- вый выход закрывается. Тем самым уп- мулам (24) при заданном значении и).; 35 равление передается на БМУ 26. С при- вычисляет величины Д и Д по фор- ходом первого тактово.го импульса на мулам (18) при том же ш iБМУ 26 в нем происходит загрузка

начального адреса микропрограммы, который поступает с третьего выхода Затем значения частоты и) послед о- 40 ПЗУП 25.. В очередном такте со второ- ватепьно перестраиваются по опреде го выхода ПЗУМ 22 передается на РТИ ленной программе и для каждого из 18 управляющее воздействие, по кото- них повторяют указанные операций. По- рому тактовые импульсы начинают полученные при этом значения г(ш) пооче- ступать дополнительно на третий и редко сравниваются между собой и так 45 четвертый выходы РТИ 18. Дальнейшая продолжается до момента получения мак- работа вычислителя 10 на этапе перевход вычислителя 10, на первый вход которого поступают синхронизирующие тактовые импульсы с третьего выхода делителя 2 частоты. После считьшания всех п кодов мгновенных значений U(tg) и ввода их в вычислитель 10, на втором вькоде счетчика 8 тактов появляется импульс переполнения (заи закрывая тем самым элементы И 3 и 12.

вычисляет функцию Г(и)) по формуле (23).

симума сигнала Г(из), т. е.г () . Значение LO, при котором функция

r(u)) достигает максимума Г,) представляет результат измерения, т.е. частоту входного напряжения U(t), поступающий с вычислителя 10 на блок 11 регистрации.

После этого по формулам (16) и

(17) производится определение ампли- 55 ПЗУМ 22. Разрешение вьщачи адреса, туды и фазы синусоидального сигнала. маски и коды выполняемых операций

дпя БАЛУ 23 считываются с четвертого выхода ПЗУМ 22 и через регистр 27 поступают на соответствующие вхоПеревод вычислителя 10 в рабочий режим осуществляется, как указывалось вьппе, тактовым импульсом, посту-

10

15

записи кодов мгновенных значений в ОЗУ 24 состоит из п циклов, где п - число этих кодов.

50 Рассмотрим один цикл, поскольку все они совершенно идентичны.

Напомним, что с приходом каждого тактового импульса в БМУ 26 формируются адреса опрашиваемых ячеек

ды БАЛУ 23. Использование регистра 27 позволяет сократить длительность одного такта с 246 не до 126 не.

В начале цикла в БАЛУ 23 происходит формирование и запись в соответствующий регистр адреса ячейки , ОЗУ 24, в которую будет записан ис- комьй код. В первом цикле код ячейки памяти нулевой, а в последующих - на единицу больше предыдущего. Его формирование достигается путем подачи на БАЛУ 23 команд соответственно для первого цикла - CSR, а для последующего - ILR. Запись в регистр адреса происходит по команде LMI. Признак Фв, поступающий на седьмой вход БАЛУ 23 со второго выхода БМУ 26 для команд CSR и ILR равен единице, а для LMI - нулю. В свою очередь, признак Фв формируется БМУ 26 в зависимости от состояния управляющих входов УФ,- УФ5, которые связаны по второму входу с первым выходом ПЗУМ 22.

Далее БАЛУ 23 по своему третьему входу принимает информацию от входного БР 19. Это происходит при подаче команды LDI через регистр 27 с четвертого выхода ПЗУМ 22 с равным единице признаком Фв. В следукнцем такте

гистра, содержащего код п, вычитается значение адреса ячейки памяти ОЗУ 24, увеличенное на единицу, а регистр, содержащий результат, анализи

5 руется на нуль. Это происходит при подаче команд ILR, CIA, SDR, ILR, ALR и TZR, причем признак Фв для второй команды ILR и ALR равен нулю, а в остальных случаях - единице.

10 Если содержимое анализируемого регистра равно нулю, что соответствует окончанию программного модуля, то на четвертом выходе БАЛУ 23 появляет ся нуль, а в противном случае - еди 5 ница. БМУ 26, который до этого выполнял переходы ICC и ICR, по призна ку Ф (т.е. по результату анализа) на третьем входе, осуществляет условный переход ICF, а затем, вьшолнив пере20 ходы ICC и ICR, переходит на завершение программного модуля либо возвращается на тот участок микропрогра мы, откуда начинается цикл перезаписи информации. При вьшолнении услов 5 ного перехода на БАЛУ 23 подается ко манда DCA, которая с признаком Фв, равным единице, является пустой операцией.

При завершении программного модул

на четвертом выходе ПЗУМ 22 появляет- 30 на втором выходе ПЗУ1 1 22 появляется

ся разрешение на выцачу адреса и данных соответственно на второй и третий выходы БАЛУ 23, а на третьем выходе ПЗУМ 22 - разрешение на запись поступившей информации в ОЗУ 24. 35

По завершению записи очередного значения кода мгновенного значения в ОЗУ 24 БАЛУ 23 совместного с БМУ 26 осуществляют условный переход. Суть

команда, по которой РТИ 18 вьщачу тактовых импульсов по второму, четвертому и пятому выходам прекращает. В -то же время первьй выход РТИ 18 от крывается. Тем самым управление передается на БМУ 21. С этого момента вычислитель 10 приступает к расчету искомых величин.

Предлагаемое устройство уменьшает

его сводится к следующему: если коли- 40 погрешность измерения (по сравнению

чество совершенных циклов равно количеству мгновенных значений исследуемого сигнала, то осуществляется завершение этого программного модуля, в противном случае цикл повторяется. 45 Происходит это так. Перед началом выполнения циклов перезаписи в БАЛУ 23 производится генерация числа п - количества мгновен ных значений исследуемого сигнала. Так, например, для 50 п 32 последовательно вьтолняются команды CSR и ILR и пять раз ALR. При этом признак Фв равен для команд CSR и ILR единице, а для команды

ALR - нулю. Генерация п 32 происхо- 55 которых в инфранизкочастотном диападит путем комбинации описанных команд. Код числа п записывается в любой из девяти регистров БАЛУ 23. При выполнении условного перехода из регистра, содержащего код п, вычитается значение адреса ячейки памяти ОЗУ 24, увеличенное на единицу, а регистр, содержащий результат, анализируется на нуль. Это происходит при подаче команд ILR, CIA, SDR, ILR, ALR и TZR, причем признак Фв для второй команды ILR и ALR равен нулю, а в остальных случаях - единице.

Если содержимое анализируемого регистра равно нулю, что соответствует окончанию программного модуля, то на четвертом выходе БАЛУ 23 появляется нуль, а в противном случае - единица. БМУ 26, который до этого выполнял переходы ICC и ICR, по признаку Ф (т.е. по результату анализа) на третьем входе, осуществляет условный переход ICF, а затем, вьшолнив переходы ICC и ICR, переходит на завершение программного модуля либо возвращается на тот участок микропрограммы, откуда начинается цикл перезаписи информации. При вьшолнении условного перехода на БАЛУ 23 подается команда DCA, которая с признаком Фв, равным единице, является пустой операцией.

При завершении программного модуля

команда, по которой РТИ 18 вьщачу тактовых импульсов по второму, четвертому и пятому выходам прекращает. В -то же время первьй выход РТИ 18 открывается. Тем самым управление передается на БМУ 21. С этого момента вычислитель 10 приступает к расчету искомых величин.

Предлагаемое устройство уменьшает

с известным) от единиц до десятков процентов, даже при небольших фазовых погрешностях фазового сдвига и заданий значения синуса и косинуса, а также при малых нелинейных искажениях, весьма характерных для практики

Техническое преимущество предлагаемого устройства (по сравнению с известным) состоит в неограниченном распирении частотного диапазона измерений в сторону низких и инфранизких частот за счет исключения операции фазового сдвига, а следовательно, и фазовращателя, техническая реализация

зоне очень и очень сложна.

Предлагаемое устройство (по сравнению с известн15 м) имеет более высокое быстродействие по двум причинам. Вопервых, в связи с. отсутствием фазо- сдвигающего блока переходные процессы в котором занимают 8-10 периодов входного сигнала. Во-вторых, время измерения Т в предлагаемом устройстве не зависит от частоты входного сигнала и может быть выбрано меньше одного периода. Б прототипе это время составляет 2-3 периода входного сигнала. Таким образом, в прототипе время измерения составляет 10-13 периодов входного сигнала, в предполагаемом устройстве - меньше одного периода. Это особенно важно при измерениях в инфранизком диапазоне частот.

Формула изобретения

1. Устройство для измерения характеристик синусоидального сигнала, содержащее аналого-цифровой преобразователь, оперативно запоминающее устройство, вычислитель, блок управления и блок регистрагщи, причем первый выход блока управления соединен с первым входом вычислителя, выход которого подключен к входу регистратора,о тличающееся тем,что,с целью расширения функциональных возможностей, повьш1ения точности и быстродействия измерения, в него введены генератор тактов, делитель частоты, два элемента И, элемент ИЛИ, счетчик тактов,, причем выход генератора тактов подключен к входу делителя частоты, первый и второй выходы которого соединены с первыми входами соответственно второго и первого элемента И, а третий выход - с третьим входом вычислителя, выход первого элемента И подключен к вторым входам элемента Ш1И и вычислителя, а выход второго элемента И к первым и вторым входам соответственно элемента ИЛИ и аналого-цифрового преобразователя, первый вход которого является входом устройства, а первый и второй выходы подключены соответственно к первому и второму входам оперативного запоминающего устройства, выход которого соединен с четвертым входом вычислителя, а третий вход оперативного запоминающего устройства соединен с первым выходом счетчика тактов, первьш вход которого соединен с выходом элемента ИЛИ, а второй выход счетчика тактов подключен к его второму входу и входу

блока управления, подключенного своими вторым и третьим выходами к вторым входам соответственно первого и второго элементов И,

52. Устройство по п. 1, отличающееся тем, что блок управления содержит первьй и второй элемент И, первый и второй триггер, кнопку Пуск, причем вход блока уп- O равления подключен к объединенным

первым входам элементов И, вторые входы которого соединены с единичными выходами первого и второг о триггеров соответственно, которые являются со- 5 ответственно вторым и третьим выходами блока ттравления, выход первого элемента И подключен к входу установки нуля первого триггера, выход второго элемента И - к входу установки

0 единицы первого триггера и входу установки нуля второго триггера, кнопка Пуск соединена с входом установки единицы второго триггера, выход второй схемы И является нужным выходом

5 блока управления.

3. Устройство по п. 1, отличающееся тем, что вычислитель содержит дешифратор, распределитель тактовых импульсов, входной буферный

0 регистр, схему ускоренного переноса, первый и второй блок микропрограммного управления, первое и второе пос-, тоянное запоминающее устройство, блок арифметически-логических устройств,

5 оперативное запоминающее устройство, регистр, выходной буферньй регистр, причем первый вход вычислителя подключен к первым входам первого блока микропрогра;ммного управления и рас0 пределителя тактовых импульсов, второй и четвертый входы подключены соответственно к первому и второму входу входного буферного регистра, третий вход вычислителя - к второму вхо5 ду распределителя тактовых импульсов, первый и второй выходы которого соединены соответственно с вторым входом первого блока микропрограммного управления и первым входом второго

0 блока микропрограммного управления, третий и четвертый выходы - соответственно с первым и вторым входами блока арифметически-логического устройства, а третий и четвертые входы

5 подключены соответственно к третьему выходу дешифратора и второму выходу первого постоянного запоминающего устройства, первый и второй выходы депнфратора соединены соответственно

13. 1307366

с BTopbw входом выходного буферного регистра и третьим входом входного буферного регистра, а вход - с первым выходом второго постоянного запоминающего устройства, третий выход которо- 5 го подключен к четвертому входу второго блока микропрограммного управления, второй выход и вход соединены соответственно с третьим входом и выходом первого постоянного запоминающего устройства, у которого третий выход подключен к первому входу оперативного запоминающего устройства, а четвертый выход через регистр соединен с шестым входом блока арифметически-логических устройств, третий вход которого подключен к выходу входного буферного регистра, а перходом первого блока микропрограммно- вый выход и четвертый вход подключе- го управления, четвертый вход которого подключен к четвертому выходу блока арифметически-логических устройств и третьему входу второго блока микропрограммного , второй выход щего устройства, а третий выход - к кйторого соединен с седьмым входомтретьему входу оперативного запоминаюблока арифметически-логических уст-щего устройства и первому входу выройств, а первый выход и второй входходного буферного регистра, выход косоответственно с входом и первым вы- торого является выходом вычислителя.

ны соответственно ко входу и выходу схемы ускоренного переноса, пятый вход и второй выход - к выходу и второму входу оперативного запоминаю14

ходом первого постоянного запоминающего устройства, у которого третий выход подключен к первому входу оперативного запоминающего устройства, а четвертый выход через регистр соединен с шестым входом блока арифметически-логических устройств, третий вход которого подключен к выходу входного буферного регистра, а пер вый выход и четвертый вход подключе- щего устройства, а третий выход - к третьему входу оперативного запоминаюны соответственно ко входу и выходу схемы ускоренного переноса, пятый вход и второй выход - к выходу и второму входу оперативного запоминаюOWZ/

Составитель Е.Губанов Редактор А.Ревин Техред А.КравчукКорректор А.Обручар

Заказ 1627/4АТираж 731Подписное

ВНИИПИ Госуда15ственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно- полигра отческое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| ИМПУЛЬСНО-ФАЗОВАЯ РАДИОВЫСОТОМЕРНАЯ СИСТЕМА | 2013 |

|

RU2551448C1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

Изобретение относится к цифровой электроизмерительной технике, а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов. Цель изобретения - расширение функциональных возможностей, повышение точности и быстродействия устройства. Устройство содержит блок 5 управления, аналого-цифровой преобразователь 6, элемент ИЛИ 7, оперативное запоминающее устройство 9, вычислитель 10, блок 11 регистрации. В устройство введены генератор 1 тактов, делитель 2 частоты, элемент И 3 и 4, а блок 5 управления выполнен на элементах И 12 и 13 и триггерах 14 и 15. Это позволяет уменьпить погрешность измерения по сравнению с известным от единиц до десятков процентов. Искпю- чение фазовращателя позволяет расширить частотный диапазон измерений в сторону низких и инфранизких частот. Отсутствие фазосдвигающего блока, переход, процессы в котором занимают 8-10 периодов входного сигнала, а так-а же независимость времени измерения, которое может быть выбрано меньше одного периода, от частоты входного сигнала, повышает быстродействие устройства. 2 з.п. ф-лы, 2 ил. & (Л utt оо о со О5 О5

| Патент США № 4523289, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| « | |||

Авторы

Даты

1987-04-30—Публикация

1985-12-30—Подача