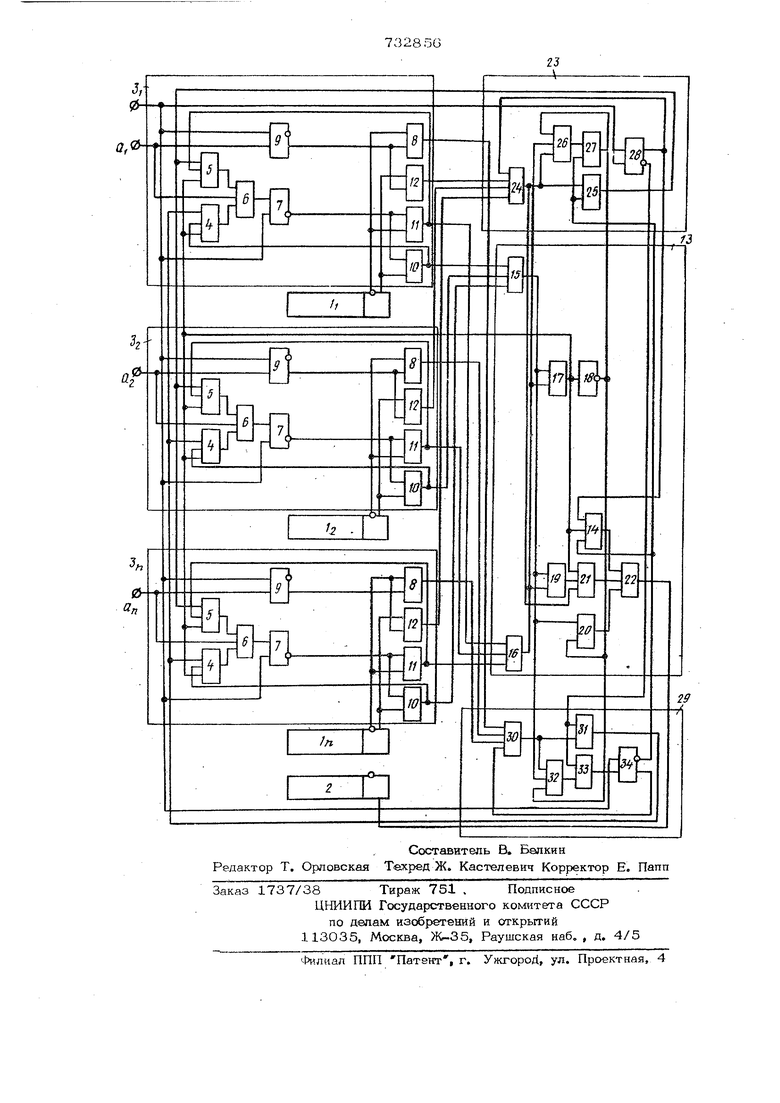

Изобр.ет9ние относится к области автоматики и вычислительной техники и м жет быть использовано в системах дискретного управления и ЭВМ при сравнени и анализе двоичных чисел. Известно устройство для выбора из множества чисел числа, ближайшего к заданному |lj , которое, кроме регистров чисел, содержит регистр для записи заданного числа, два регистра приема чис8П| схему определения положения заданного числа относительно двух других, записанных на данном этапе сравнения в регистрах приема, две схемы совпадения и линии задержки. Результат достигается путем вьшолнения цикла выбора из двух очередньк чисел, числа,ближайшего к заданному. К недостаткам этого устройства отн сятся невысокое быстродействие и значительное количество оборудования. Наиболее близким техническим решением к предложенному является устройство, содержащее п кольцевьк сдвигаю- ших регистров, регистр результата, п узлов ком1.1утациИ| узел анализа, -первый и второй узлы переключения, причем прямой и инверсный вькод } последнего разряда -го кольцевого сдвигающего регистра подключены к первому и второму входам i -го узла коммутации, третий вход каждого из которьк подключены к информационным входам устройства, чет верфые входы узлов коммутации подключены к шине управления, первый выход первого узла переключения соединен с пятыми входами всех узлов коммутации, второй выход первого узла переключения подключен к первому входу узла анализа, третий выход первого узла переключения соединен с первым входом второго узла переключения, первый вьрсод которого подключен к шестому входу каждого узла коммутации, второй выход второго узла переключения соединен со вторым нходом узла анализа и с первым аходом первого узла переключения 37 Описанное устройство имеет ные функциональные возможности. Резул татом сравнения является выбор только одного из экстремальных чисел, пря гхгом выбрать число, ближайшее к заданному, с помощью устройства невозможно. За всключеннем экстремальных чисел, сстал ные числа массива уничтожаются, что в целом ряде практических случаев неке- лательно или недопустимо. Зачастую доотуп к регистрам массива невозможен и результат сравнения требуется выводить в отдельный регистр, что в данном уст ройстве не предусмотрено. Цель изобретения - расширение функциональньсс возможностей путем обесдечения сжатия информации, Поставленная цель достигается тегл , что в предложенном устройстве первый выход каждого узла ком гутадии подключен к соответствующему входу пер . вой группы входов «второго узла переклю чения, второй выход каждого уала комму тации соединен,с соотв-етствуюлшм вхо дом первой группы входов первого узла перекшочекиЯз третий выход каждого узла коммутадии подключен к cooTB-eTCTBy ющему входу nepBoti. группы входов уз. ла анализа, четвертый выход каждого у-э ла коммутадии соединен с .соответствую шим входом второй группы входов узла анализа. Второй вход первого узла пера лючения подключен к шине управления, а его четвертый выход соединен с тршь им входом, узла анализа, первый выход которого подключен к третьему входу первого узла переключения и ко BTOpoiviy входу второго узла переключения. Третий вход второго узла переключения со-Э динен -с шиной управленияэ второй выход узла анализа подключен ко входу |}егасТ ра результата, третий выход узла . аиа лиза соединен с четвертым входом второго узла переключения, четвертый выход уала анализа подключен к Ч8твер тому входу первого узда пареключанияз пятый выход узла анализа соединен с седьмьпу входом каждого узл-в KOMviyтадии. Каждый из узлов, комисутэлнй состоит из- элементов И, ИЛИ, триггеров причем первые входы первого и второго эл ментов И подключены к первому входу узла, первые входы третьего и чет5зер того элементов И подключены ко второму аходу узла. Первый вход первого триггера соединен с перв1-,1М входом вто рого триггера и подключен к чeтвepтo 4y 64 входу узла, второй в,ход первого триггера соединен с первым входом элемента ИЛИ и подключен к третьему входу узла. Выход первого соединен со вторыми аходами первого и третьего элементов И„ Первый вход пятого элемента И подключен к пятому входу узла, второй аход пятого элемента И соединен с выходом второго элемента И, третий аход пятого элемента И подключен к перво- Sviy входу шестого элемента И и соединен с седьмым . входом узла, Е торой вход шестого-элемента И подключен к вьгходу четвертого элемента И, третий вход шестого элемента И соединен с шестым вхо- ,дом узла„ Выходы пятого и шестого эле- меитов И подключены ко второму и треть- входам элемента ИЛИ соответственно Выход элемента ИТМ соединен со вторым входом второго триггера, выход которого подключен ко вторкм входам второго и четвертого элементов И. Выходы первого , второго третьего и четвертого элементов К соединены с первым, третьим вторым и четвертым выходами узла соответственно. Узел анализа состоит из элементов И, ИЛИ, НЕ, причем входы первого элемента ИЛИ подключены к первой группе входов узла, а его выход к первым входам первого и второго элементов Ник .четвертогуд,- вькоду узла. Входы второго шгемента ИЛИ соединены со второй группой входов узла, а его вьрсод - со вто- рьйЛй ккойзми. первсго и второго элемек-тов Hj с первым входом третьего элемента И и с третьим выходом уала, BbJход второго элемен га И подключен к первым входам четвертого и пятого элементов И, к пятому выходу узла и через элемент НЕ - ко второш входу третьего элемента И и к первому выходу узла, Вторые входы четвертого и пятого элементов И соединены с пэрвым и третьим входами узла соотвгпгственно, третий вхаа .четвертого элемент И подключен ко вто- , рому входу узла, третий выход первого элемента И соединен с третьим- входом пятого элемента И, Выход которого подключен к первому аходу элемента ИЛИ, второй и третий входы которого соединены с выходами третьего и четвертого элементов И соотве гственно,-выход эле- MeiiTa ИЛИ подключен ко второму выходу узла. Первый узел переключения содержит элементы И, ИЛИ, триггер, причем входы элемента ИЛИ соединенЕл со входами ;..уп- пы входов уола, а его выход - с гюрвы.ми аходамй первого и второго элементов И и четвертым выходом узла. Второй и третий аходы первого элемента И подключены к третьему и четвертому входам узла, а его выход - к первому входу третьего эламеет-а И, второй вход которого соединен со вторым входом второго эпе мента И ,и с первым входом узла. Выход третьего элемента И подключен к первому аходу триггера, второй аход которого 10 соединен со вторым аходом узла, а прямой вькод - со аходом. элемента ИЛИ и до вторым выходом узла. Инверсный вы ход триггера и выход второго элемент .И подключен к третьему и первому выходам узла соответственно. Второй узел переключения содержит элементы И, ИЛИ, триггер, причем входы элемента ИЛИ соединены со аходамй группы входов узла, а его выход - с первым входом первого и второго элег ментов И. Второй и третий аходы перво го элемента И подключены ко второму и четвертому входам узла, а его выход к nepBONfy входу третьего элемента И, второй вход которого соединен со вторым входом второго элемента. И и с пер вым входом узла. Вьрсод третьего элемента И подключен к первому аходу три гера, второй вход которого соединен с первым аходом узла, а прямой выход - со входом элемента ИЛИ, инверсный вьь ход триггера и выход второго элемента И подключен ко второму и первому выходам узла соответственно. Структурная схема устройства представлена на чертеже. Устройство содержит кольцевые сдвигающие регистры 1д - Ifiрегистр р&зультата 2; узлы коммутации 3yj - 3 г каждый из которых состоит из элементов И 4, 5, элемента ИЛИ S, триггера 7, элемента И 8, триггера 9, элементов И 10, 11, 12;.узел анализа 13, состоящий из элемента И 14, элементов ИЛИ 15, 16, элемента И 17, элемеш-а НЕ 18, элементов И 19, 2О, 2 Ij элемент ИЛИ 22; первый узел переключения 23, состоящий из элемента ИЛИ 24 элементов И 25, 26, 27, триггера 28;второй узел переключения 29, состоящий из элемента ИЛИ 30, элементов И 31, 32, 33, триггера 34. Устройство работает следующим образом. В исходном состоянии в кольцевьк сдвигающих регистрах саны числа, имеются сигналы на инверс-

ных выходах триггеров 7 и 34, регистр результата 2 в состоянии О.

Пусть подан сигнал на информационные входы, что соответствует вьйору числа, записанного в регистре 1, в качестве заданного. При этом появится сигнал на прямом выходе -триггера 9, на аходе элемента ИЛИ 6, а следовательно, на нходе триггера 7. Триггер 7 уст новится в состояние 1 и отключит тем самым от участия а -последующей усл-ройства элементы И 10 и 11, Множество остальных чисел (ncKine исключения заданного числа) будем называть массивом. Сигнал с прямого выхода триггера 9 подготавливает схемы И 12 и 8 Возможны три случая представления информации. 1, Пусть в старшем разряде заданного числа записана 1, старигае разряды чисел массива равны между собой и их триггеры установлены в О. В этом случае на первом такте сравнения имеется сигнал на обоах аходах элемента И 12 регистра заданного числа. Следовательно, имеется сигнал на его выходе, выходе элемента И ЛИ24 и первых входах элементов И 25, 26 узла переключения 23 и третьемаходе элемента И 21 Имеется также сигнал на инверсном выходе триггеров 28 и 34, что приводит к появлению сигнала на вторых входах элементов И 25, 27 узла 23 и элеменн TOB И 31, 33 узла 29, Наличие сигнала на выходах триггеров 7 узлов коммутации, кольцевых сдвигающи-х регистров 1д, - If и на инверсных, выходах их анализируемых разрядов приводит к появлению сигнала только на вьгходе злеменгга ИЛИ 16, а следовательно, на втором аходе элемента И 17, втором входе элемента И 26 узла 23 и второмвходе элемента И 19. Отсутствие сигнала на втором входе элемента И 17 приводит к появлению сигнала на выходе элемента НЕ 18, и соответственно, на третьем : аходе эле- меета И 26 и втором аходе элемента И 2О, Наличие сигнала на всех аходах элемента И 26 узла 23 приводит к лению сигнала и на первом входе элемента И 27, следовательно, на его выходе. Триггер 28устанавливается в и появг ляющийся сигнал на его прямом вькоде поступает на аход элемента ИЛИ 24 узла 23. Таким образом, до окончания цикла сравнения имеются сигналы на прямом выходе триггера28 и на выходе элемента ИЛИ 24 узла 23 и на инверсном вььходе триггера 34 узла 29. Появляется сигнал на выходе элемента И 25 узла 23 следовательно на первых входах элемента И 5, Однако отсутствуют сигналы на его остальных аходах, поэтому никаких переключений в узле коммутации не прои-; зойдет. Следовательно, в анапизируемрм разряде регистра результата 2 останется О,

В дальнейшем работа устройства сводится к поиску среди остальных чисел наиВопьшего, которое и будет ближайшим к заданному. Эта процедура состоит в следующем. На всех последую1Щ1.х тактах 15 при равенстве анализируемьгх разрядов повторится рассмотренная ситуация, т.е, изменений в схеме не произойдет, а в соответствующий разряд регистра резуль тата запишется число, содержащееся в этом разряде сравниваемых чисел, так как при равенстве анализируемого разряда нулю запишется (ситуация pac смотрена), а при равенстве, единице появится сигнал на первом входе триггера 28, следовательно, на выходе элемента ИЛИ 22 появится сигнал и 1 запишется в регистр результата 2. При неравенстве значений анапизируемых разрядов массива появляются сигналы на входах элемететов ИЛИ 15 и 16, следовательно,, на обоих аходах элемента И 17 и на выходе элемента НЕ 18 и на третьих в.ходах элемеш-ов И 4 и 5 всех узлов коммутации. Сигнал появляется на вторых входах элементов И 5 тех регистров, в анализируемых разрядах которых записан О. В этом случае сигнал с выхода элемента И 5 через эл мент ИЛИ 6 перебрасьшает триггер 7 с ответствующих узлов коммутации, в результате чего соответствующие регистры исключаются из дальнейшей процедуры сравнения. Наличие сигнала на всах входах элементов И 19 и 14 приводит к появлению сигнала на выходе элемента ИЛИ 2 Следствием этого является запись 1 в анализируемый разряд регистра резуль тата. 2. Пусть в старшем разряде заданного числа записан О, а старшие разряды -чисел массивов равны между собой и в них записана 1. В этом случае на первом такте сравнения имеется сигнал на обои.х входах элемента И 8 регистра заданного числа. Следовательно, появляется сигнал на выходе элемен

та И 30 узла 29. Дальнейшее прохождение сигналов аналогично описанному для узла 23. В результате до окотвния цикла работй устройства будет сиг нал на прямом выхода триггера 34 узла 29 и инверсном выходе триггера 28 узла 23, а также на выходе элемента И 31 узла 29,

В дальнейшем работа устройства сво-. дится к поиску среди массива чисел наименьшего, которое и будет ближайшим к заданному. Эта процедура аналогична описанной при поиске наибольшего числа с той разницей} что подготовленными яв-ляются первый и третий входы элемен.та И 4, второй в.ход которого подоготов- ляется при равенстве 1 анализируемого разряда массива. При этом исршючаются из процедуры сравнения регистры, в анализируемых разрядах которых записана 1. В соответствующем разряде регистра результата сохранится: О. 3. Старшие разряды чисел не равны между собой. В этом случае имеются сигналы на нходах элементов ИЛИ 15 и 16, следовательно, на И.Х выходах и обоих нходах элемента И 17. Сигнал с вькода элемента И 17 подается на третьи Б.ХОДЫ всех элементов И 4 и 5, Если при этом в ана-лизируемом разряде заданного числа записана 1, то имеется сигнал на вьгходе элемента ИЛИ 24 узла 23, следовательно, на первом в.ходе элемента И 25, на втором входе которого имеется сигнап с инверсного выхода триггера 34 узла 29. Сигнал с выхода элемента И 25 узла 23 подается на первые входы элемента И 5. Сигналы на вторьк входах элемента И 5 появятся только в тех узлах коммутации j в анализируемых разрядах регистров которых записан О, Аналогично описанному исчезает сигнал на инверсном выходе триггера 7, и число исключается из дальней- шего рассмотрения. Аналогично описанному появится сигнал на выходе элемента ИЛИ 22, и в рассматриваемый разряд регистра результата запишется 1. Если в анализируемом разряде заданного числа записан О, то появляется сигвал на вькоде элемента И 31 узла 29, следовательно, на первых в.ходах элементов И 4. При этом из-дальнейшего срав- нё11йя исключаются регистры, в анализи руемом разряде которых записана . Сигнал на выходе элемента ИЛИ 22 отстгствует(ситуация .рассмотрена ранее) и в соответствующем разряде регистра результата 2 останется О. Таким образом, при несовпадении зна чений анализируемых разрядов чисел из дальнейшего рассмотрения исключаются те из них, анализируемый разряд которы не совпадает с соответстсвующим разрядом заданного числа. Если на очередном такте возникает с туация, когда анализируемый разряд за данного числа равен ICO), а анализи руемый разряд чисел массива-соответственно О ), то устройство продол жа-ет поиск аналогично пп. 1 и 2 описания работы устройства. Таким образом, после окончания цикл работы устройства в регистре 2 записан результат выбора - число, бли цайшее к заданному. Состояние 01 триггеров 7 и 9 индицирует заданное число, а Состояние ОО этих же триггеров - число, ближайшее к заданному. Изобретение позволяет расширить функ циональные возможности устройства, поскольку дает возможность при достаточно вьюоком быстродействии находить в масс ве число, ближайшее к заданному, сохранять информацию, индицировать заданное число и число, ближайшее к нему, а также выводить на отдельный регистр результат выбора. Формула изобретения 1. Устройство для выбора числа, ближайшего к заданному, содержащее И кол j цевьк сдвигающих регистров, регистр разультата, а узлов коммутации, узел анализа, первый и второй узлы переключения, причем прямой и инверсный выходы последнего разряда I -го кольцевого сдвигающего регистра подключены к первому и втор ому входам 1 -го ( i l,2...T узла коммутации, третий вход каждого из которык подключен к информационным ахо дамс устройства четвертые аходы узлов коммутации подключены к шине упраалени первый вьгх.Ьд первого узла переключения -соединен с пятыми входами всех узлов коммутации, второй вькод первого узла переключения подключен к первому аходу узла анализа, третий выход первог узла переключения соединен с первым входом второго узла переключения, первый вькод которого подключен к шестому входу каждого узла коммутации, второй ВЬРСОД второго узла переключения соединен со вторым в.ходом узла анализа и с 7 5610 первым RxoAOM первого узла переключения, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения сжатия информации, в нем первый выход каждо го узла коммутации подключен .к соогветствующаму 6.ходу перво1 группы входов второго узла переключения, второй выход каждого узла комк1утации соединен с соответствующим входом первой группы входов первого у.зпа переключения, третий ВЫ.ХОД каждого узла коммутации подключен к соответствующему кходу первой группы входов узла анализа, четввртый выход каждого узла коммутации соединен с соответствующим в.ходом втсь рой группы входов узла анализй, второй вход первого узла переключения подключен к шине управления, а его четвертый выход соединен с третьим входом узла анализа, первый выход которот о подклю чен к третьему входу первого узла переключения и ко второму аходу переключения, третий вход которого соединен с щиной управления, второй выход узла анализа подключен ко оду регистра результата, третий вьгход узла анализа соединен с четвертым входом второго узла переключения, четвертый выход узла анализа подключен к четвертому входу первого узла переключения, пятый выход узла анализа соединен с седьмым входом каждого узла коммутации. . 2, Устройство по п. 1, о т л и ч аю щ е е с я тем, что в нем каждый из узлов коммутации состоит из элементов И, ИЛИ, триггеров, причем первые входы первого и второго элементов И подключены к первому В.ХОДУ узла, первые входы третьего и четвертого элементов И подключены ко второму входу узла, первый аход первого триггера соединен .с первым входом второго триггера и подключен к четвертому аходу узла, второй аход первого триггера соединен с первым входом элемента ИЛИ и подключен к третьему входу узла, выход первого триггера соединен со вторыми входами первого и третьего элементов И, первый аход пятого элемента И подключен к пятому; входу узла, второй вход пятого элемента И соединен с выходом второго элемента И, третий аход пятого элемента И подключен к nepBoKiy аходу шестого элемента И и соединен С; седьмым .входом узла, второй аход шестого элемента И подключен к выходу четвертого элемента И, третий вход шестого элемента И соединен с шеотым аходом узла, выходы пятого и шестого эпементов И подключены ко второму и третьему аходам элемента ИЛИ соответственно, выход элемента ИЛИ соединен со вторым входом второго триггера, выход которого подключен ко вторым входам второго и четвертого элементов И, выходы первого, BToporoi третьего и четвертого элементов И соединены с первым третьим, вторым и четвертым выходам узла соответственно. 3, Устройство по п. 1, о т л и ч а ющ 8 е с я там, что в нем узел анализа состоит .из элементов И, ИЛИ, НЕ, причем входы первого элемента ИЛИ подключены к первой группе входов узла, а его выход - к первым аходам первого и второго элементов И и к четвертому выходу узла, входы второго элемента ИЛИ соединены со второй группой аходов узла, а его выход - Со вторыми входами перво го и второго элементов И, с первым входом третьего элемента И и с третьим вы ходом узла, выход второго элемента И подключен к первым аходам, четве)ртого и пятого элементов И, к пятому выходу узла и через элемент НЕ - ко второму входу третьего элемента И и к первому выходу узла, вторые входы четвертого и пятого элементов И соединены с первым и третьим-входами узла соответственно, третий вход четвертого элемента И подключен ко второму аходу .;узла, тре тий выход первого элемента И соединен с третьим входом пятого элемента И, выход которого подключен к первому вхо ду элемента ИЛИ, второй и третий входы которого соединены с выходами третьего и четвертого элементов И соответственно выход элемента ИЛИ подключен ко второму выходу узла. . 4, Устройство по п. 1, о т л и ч аю щ е ее я тем, что в нем первый узе переключения содержит элементы И, ИЛИ триггер, причем входы элемента ИДИ соединены со входами группы входов уз7612 1ла, а его выход - с первыми входа1 1и первого и второго элементов И и четвертым выходом узла, второй и третий входы первого элемента И подключены к третьему и четвертому аходам узла, а его вьпсод - к первому аходу третьего элемента И, второй вход которого соединен со вторым аходом второго элемента И и с первым аходом узла, выход третьего элемента И подключен к первому входу триггера, второй вход которого соединен со вторым входом узла, а прямой выход - со аходом элемента ИЛИ и со вторым выходом узла, инверсный выход триггера и вьгх:од второго элемен.та И подключены к третьему и первому выходам узлй соответственно. 5. Устройство по п. 1, о т л и ч аю щ е е с я тем, что. в нем второй узел переключения содержит элементы И, ИЛИ, триггер, причем входы элемента ИЛИ соединены со входами группы входов узла, а его выход - с первь1М входом первого, и второго элементов И, второй и третий входы первого элемента И подключены ко второму и: четвертому аходам узла, а его выход - к первому входу третьего элемента И, второй вход .кото рого соединен со вторым входом второго элемента И, и с первым в.ходом узла, выход третьего элемента И подключен К первому входу триггера, второй в.ход которого соединен с первым В.ХОДОМ узла, а прямой выход - со аходом элемента ИЛИ, инверсный вьрсод триггера и выход второго элемента И подключен ко второму и первому выходам узласоответственно.. Источники информации, принятые во внимание Нри экспертизе 1.Авторское свкаетельствр СССР № 356643, кл. G, 06 F 7/02, 23.10,72. 2.Авторское свидетельство СССР № 19316О, кл. Q Об F 7/02 02.03.67 (прсгготип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения числа,ближАйшЕгО K зАдАННОМу | 1979 |

|

SU809166A1 |

| Устройство для сравнения двоичных чисел | 1978 |

|

SU748408A1 |

| Устройство для сравнения чисел | 1976 |

|

SU682893A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960799A1 |

| Устройство для умножения п-разрядных чисел | 1978 |

|

SU734683A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для сравнения чисел | 1977 |

|

SU726527A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1363183A1 |

| Устройство для определения экстремальных чисел | 1989 |

|

SU1661754A1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-20—Подача