Изобретение относится к запоминающим устройствам.

Известно многофункциональное запоминающее устройство, содержащее накопитель на тороидальных сердечниках с прямоугольной петлей гистерезиса, к разрядным шинам чтения Которого подключены усилители чтения; разрядные формирователи записи и считывания, выхода которых чены JK соответствующим щинам записи и считывания накопителя; регистр адреса, выходы которого подсоединены к первым входам соответствующих адресных вентилей, выходы которых через адресные формирователи записи и считывания подключены к адресным щинам записи и считывания соответственно; регистр слова, разрядные вентили и схемы ИЛИ.

Предлагаемое устройство отличается от известного тем,что оно содержит дополнителыиле схемы ИЛИ, выходы двух из ко торых через соответствукяцие адресные вентилн соединены со входами адресных формирователей записи и считывания по координате X. а выходы двух через адрес-.

ные вентили подключены ко входам афеоных формирователей записи и считывания по координате у ; ко входам схем ИЛИ подключены соответствующие управляющие

5 щины. Это позволяет расщирить функпиональные возможности устройства.

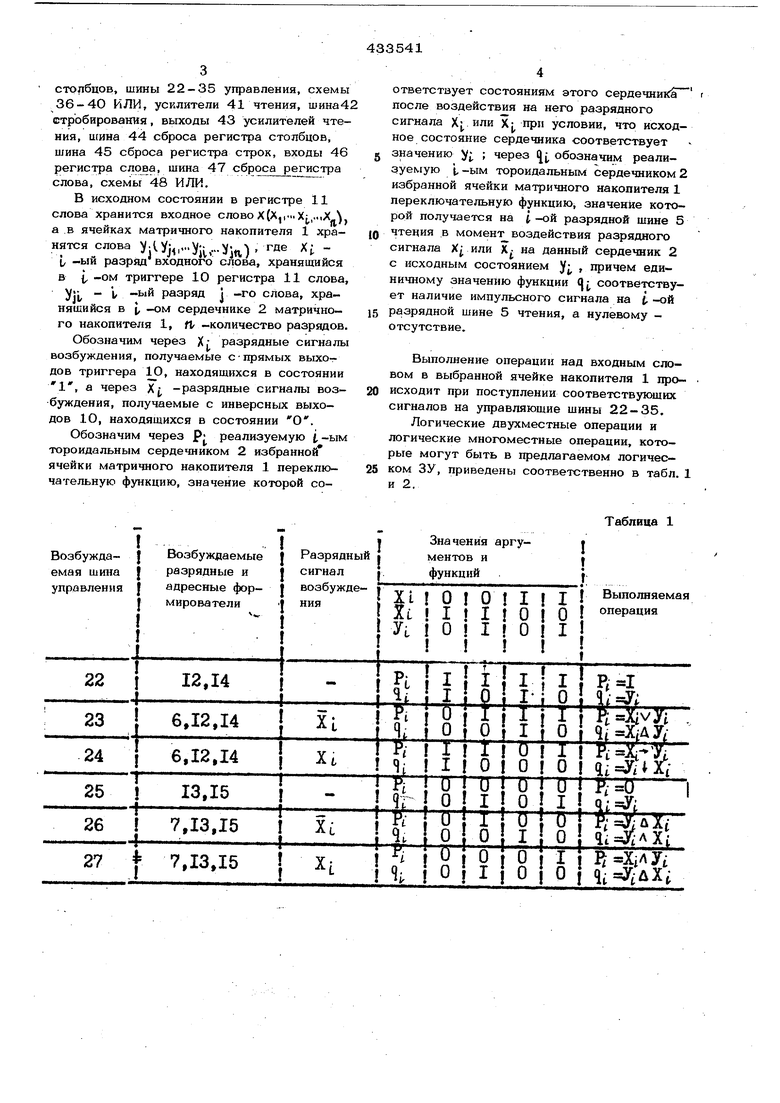

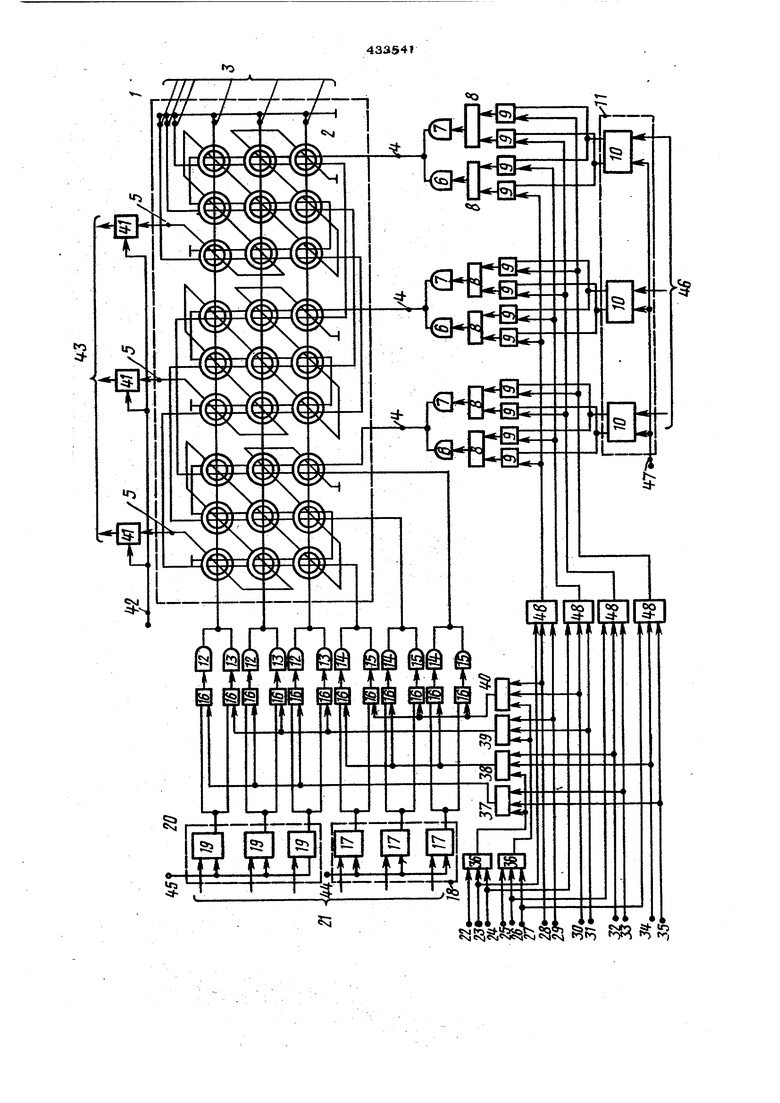

На чертеже изображена блок-схема предлагаемого многофункционального запоминающего устройства.

0 Устройство содержит матричный накопитель 1 на тороидальных сердечниках 2 с ПП-Г, пронизанных адресными шинак и 3 записи и считывания, разрядными щинами 4 записи и считывания, разрядными щинами 5

5 чтения. В устройство входят разрядные формирователи 6 считывания, разрядные форК ирователи 7 записи, схемы 8 ИЛИ, разрядные вентили 9, триггеры 1О регистра ii слова, адресные формирователи 12;

0 записи адресные формирователи 13 считывания по строкам, адресные формирователи 14 записи по столбцам, адресные формиро; ватели 15 считывания по столбцам, адрес :ные вентили 16, триггеры 17 реги- ,

5 стра 18 строк, триггеры 19 регистра 2О столбцов, входы 21 регистров строк и

столбцов, шины 22-35 управления, схемы 36-40 ИЛИ, усилители 41 чтения, шина4 етробирования, выходы 43 усилителей чтения, шина 44 сброса регистра столбцов, шина 45 сброса регистра строк, входы 46 регистра слова, шина 47 сброса регистра слова, схемы 48 ИЛИ,

В исходном состоянии в регистре 11 слова хранится входное слово X(X,,-Xj,..iX-, а ,в ячейках матричного накопителя 1 хранятся слова y;tyJH,.V;t,-5(jn,) I -ый разряд входного слова, хранящийся

в 1 -ом триггере 10 регистра 11 слова, У- - I, -ый разряд i -го слова, храняшийся в 1 -ом сердечнике 2 матричного накопителя 1, П -количество разрадов. Обозначим через Хг разрядные сигналы возбуждения, получаемые с-прямых выходов триггера 10, находяшихся в состоянии , а через X; -разрядные сигналы возбуждения, получаемые с инверсных выходов 10, находящихся в состоянии О.

Обозначим через Р реализуемую i -ым тороидальным сердечником 2 избранной ячейки матричного накопителя 1 переключательную функцию, значение которой соответствует состояниям этого сердечник после воздействия на него разрядного сигнала Х, или X: при условии, что исходное состояние сердечника соответствует

значению у ; через j, обозначим реализye ryю t -ым тороидальным сердечником 2 избранной ячейки матричного накопителя 1 переключательную функцию, значение которой получается на i -ой разрядной шине 5

чтения в момент воздействия разрядного сигнала Х или Х на данный сердечник 2 с исходным состоянием у , причем единичному значению функции (Jj соответствует наличие импульсного сигнала на t -ой

разрядной шине 5 чтения, а нулевому отсутствие.

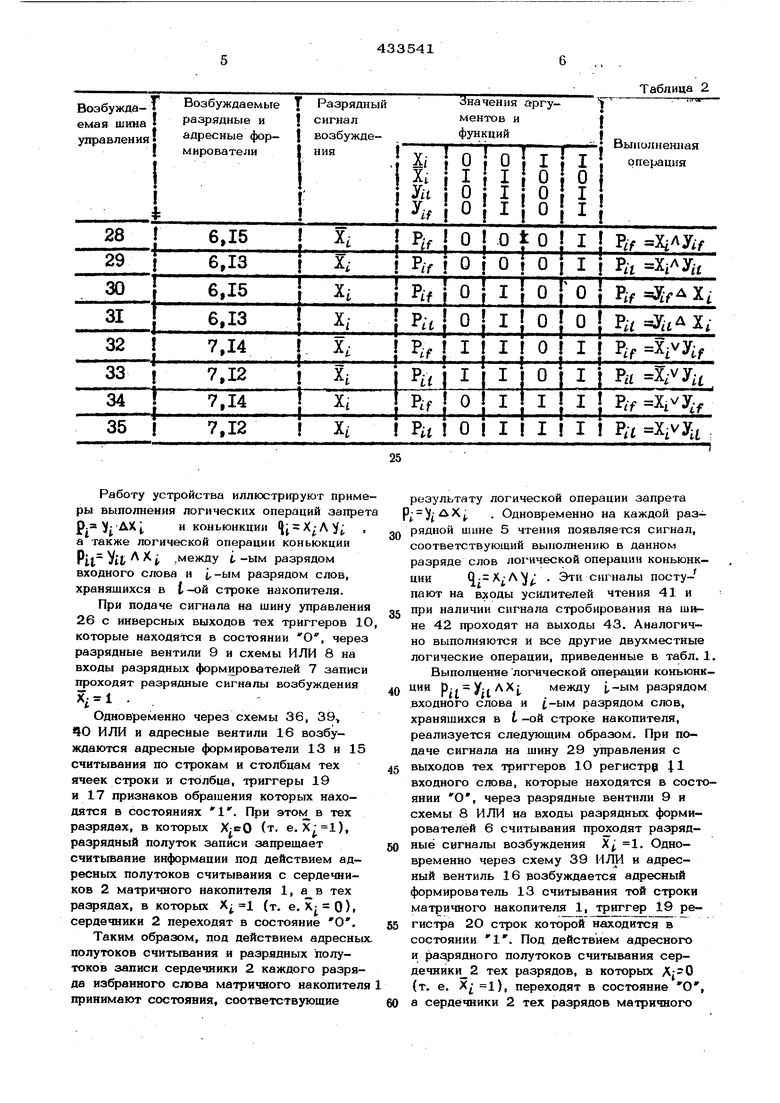

Выполнение операции над входным словом в выбранной ячейке накопителя 1 происходит при поступлении соответствующих сигналов на управляющие шины 22-35. Логические двухместные операции и логические многоместные операции, которые могут быть в предлагаемом логичес- ком ЗУ, приведены соответственно в табл. 1 и 2.

Таблица 1

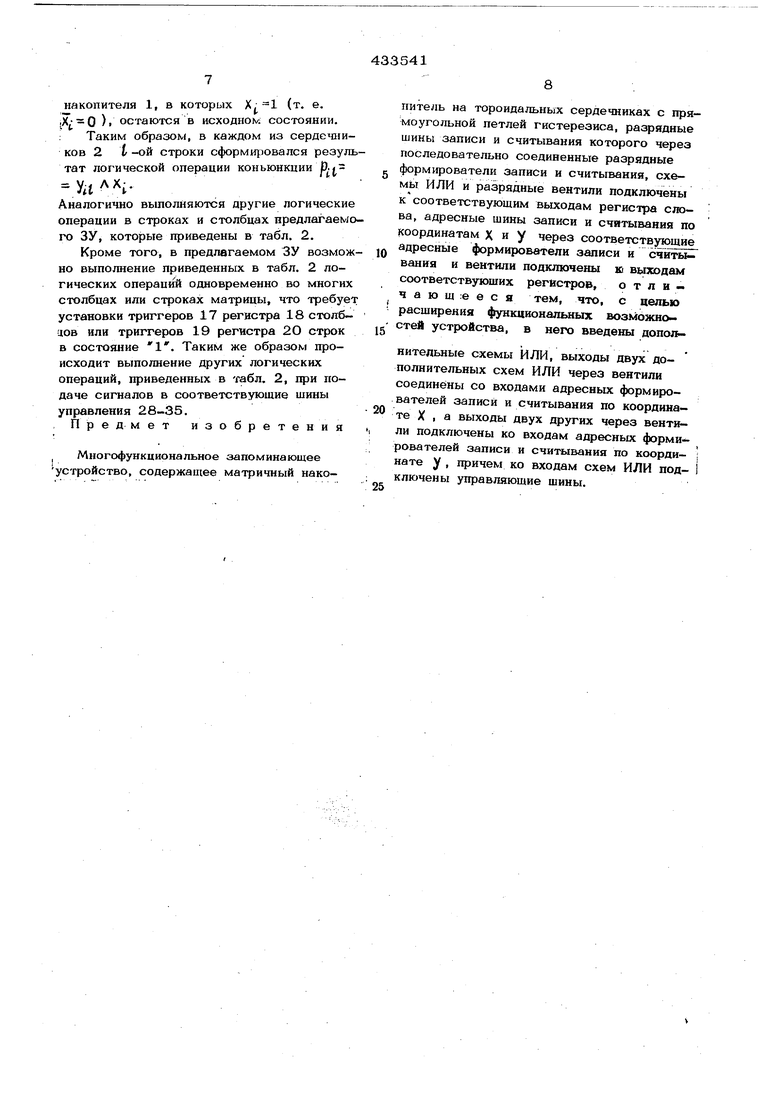

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЛОГИЧЕСКОЕ ЗАПОЛНИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432598A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

Работу устройства иллюстрируют примеры выполнения логических операций запрет p. ,и коньюикции 1

а также логической операции коньюкции .между i.-ым разрядом входного слова и 1,-ым разрядом слов, хранящихся в t-ой строке накопителя.

При подаче сигнала на шину управления 26 с инверсных выходов тех триггеров 1О которые находятся в состоянии О , через разрядные вентили 9 и схемы ИЛИ 8 на входы разрядных формирователей 7 записи проходят разрядные сигналы возбуждения . .

Одновременно через схемы 36, 39, 40 ИЛИ и адресные вентили 16 возбуждаются адресные формирователи 13 и 15 считывания по строкам и столбцам тех ячеек строки и столбца, триггеры 19 и 17 признаков обращения которых находятся в состояниях 1. При 3TON в тех разрядах, в которых Х;еО (т. е. ), разрядный полуток записи запрещает считьтание информации под действием адресных полутоков считывания с сердечников 2 матричного накопителя 1, а в тех разрядах, в которых Xj 1 (т. е. Х О), сердечники 2 переходят в состояние О.

Таким образом, под действием адресных полутоков считывания и разрядных полутоков записи сердечники 2 каждого разряда избранного слова матричного накопителя принимают состояния, соответствующие

результату логической операции запрета . Одновременно на каждой разрядной шине 5 чтения появляется сигнал, соответствующий выполнению в данном разряде слов логической операции коньюнкции1-- i Эти сигналы поступают на входы усилителей чтения 41 и

при наличии сигнала стробирования на шине 42 проходят на выходы 43. Аналогично выполняются и все другие двухместные логические операции, приведенные в табл. 1. Выполнение ло1М1ческой операции коньюнкции р-1 У-|ЛХ между 1,-ым разрядом входного слова и t-ым разрядом слов, хранящихся в L -ой строке накопителя, реализуется следующим образом. При подаче сигнала на щину 29 управления с

выходов тех триггеров Ю регистре 11

входного слова, которые находятся в состоянии О, через разрядные вентили 9 и схемы 8 ИЛИ на входы разрядных формирователей 6 считывания про содят разрядные сигналы возбуждения Х 1. Одновременно через схему 39 ИЛИ и адресный вентиль 16 возбуждается адресный формирователь 13 считывания той строки матричного накопителя 1, триггер 19 ре-

гистра 2О строк которой находится в состоянии . Под действием адресного и разрядного полутоков считывания сердечники 2 тех разрядов, в которых Aj-O (т. е. Х 1), переходят в состояние О,

а сердечники 2 тех разрядов матричного накопителя 1, в которых X; -1 (т. е. - ...Р ,Х/ 0 /I остаются в исходное, состоянии. : Таким образом, в каждом из сердсшиков 2 I -ой строки сформи1)овался резул тат логической операции коньюнкции р. j Уд Аналогично выполняются другие логические операции в строках и столбцах нредлагаем го ЗУ, которые приведены в табл. 2. Кроме того, в предлагаемом ЗУ возмож но выполнение приведенных в табл. 2 логических операций одновременно во многих столбцах или строках матрицы, что требуе установки триггеров 17 регистра 18 столбцов или триггеров 19 регистра 2 О строк в состояние 1. Таким же образом происходит выполнение других логических операций, приведенных в табл. 2, при подаче сигналов в соответствующие шины управления 28-35. Предмет изобретения I Многофункциональное запоминающее устройство, содержащее матричный накопитель на тороидальных сердечниках с прямоугольной петлей гистерезиса, разря дные шины записи и считывания которого через последовательно соединенные разрядные формирователи записи и считывания, схемы ИЛИ и разрядные вентили подключены к соответствующим выходам регистра слова, адресные шины записи и считывания по координатам X и у через соответствующие адресные формирователи записи и считывания и вентили подключены к выходам соответствующих регйстроэ, о т л и ч а ю щ :е е с я тем, что, с целью расщирения функциональных возможно стей устройства, в него введены дополнительные схемы ИЛИ, выходы двух дополнительных схем ИЛИ через вентили соединены со входами адресных формирователей записи и считывания по координате X , а выходы двух других через вентили подключены ко входам адресных формирователей записи и считывания по коорди- ; нате у , причем ко входам схем ИЛИ под- I ключены управляющие шины.

Авторы

Даты

1974-06-25—Публикация

1972-07-18—Подача