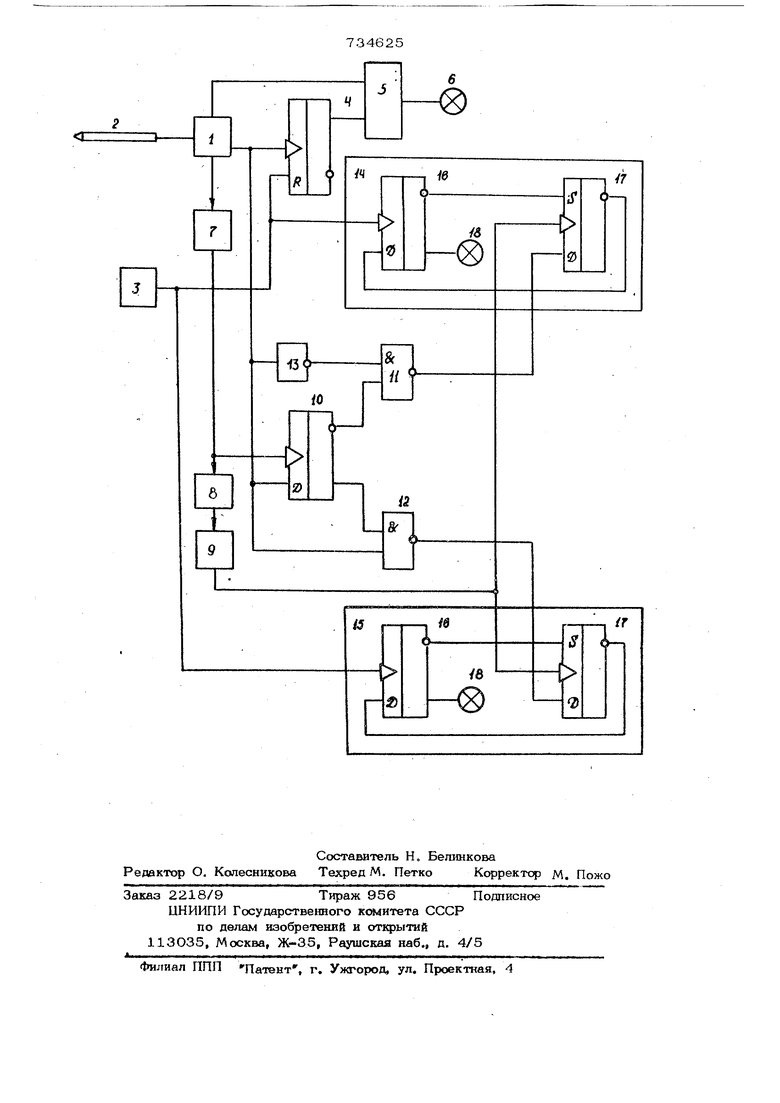

налов содержит третий и четвертый триггеры .второй индикатор, вход которого подключен к первому выходу третьего триггера, второй выход которого соединен с первым входом четвертого триггера выход которого подключен к первому входу третье го триггера, второй вход первого трит гера соединен с третьим входом формирователя сигналов, первый и второй входы четвертого триггера соединены соответстрвенно с первым и вторым входами формирователя сигналов. На чертеже изображенч функциональная схема предлагаемого устройства для проверки логических блоков. Схема устройства содержит входной блок 1, чувствительный элемент 2, генератор импульсов 3, первый триггер 4, элемент 5 отрицания равнозначности, первый индикатор 6, фильтр 7, интегратор 8, пороговый блок 9, второй триггер 10, первый и второй элементы И-НЕ 11 и 12 инвертор 13, первый и второй- формирователи 14 и 15 сигналов, каждый из которых состоит из третьего и четвертого триггеров 16, 17, индикатора 18. Устройство работает следующим обрэзом. При отсутствии импульсов на входе уст ройства, триггер 4 находится в нулевом состоянии, при котором низкий потенциал с его выхода поступает на вход элемента 5, При этом входной сигнал, поступающий с чувствительного элемента 2 через блок 1 на второй вход элемента 5, определяет состояние индикатора 6, свечение которого индицирует высокий логический уровень на входе, отсутствие свечения низкий. При наличии импульсов на чувствительт ном элементе 2 устройства, свечение индикатора 6 будет прерывистым с частотой повторения л/ 1 Гц. Это достигается за счет того, что периодически (Т -х 1 с) с генератора 3 на вход сброса триггера 4 поступают импульсы (,2 с), разрешающие его срабатывание по тактовому входу. Пошжительный фронт входного импульса, поступающего на тактовый вход трш гера, перебрасывает последний в еднни ное состояние (последующие импульсы no тверждают это состояние). При этом вы сЬкийлогический уровень с выхода триггера 4 поступает на элемент 5. Это приводит к тому, что индикация становится обратной: при высоком логическом уровне на входе индикаторный элемент-не CBSTHT я, а при низксм - светится. По окончаии времени ZT на вход триггера 4 подает я низкий потенциал, возвращающий в нулевое состояние. Исследуемый сигнал с выхода входного стройства 1 поступает также на фильтр 7. а выходе последний сигнал возникает тольо в том случае, если входное напряжение аходится в указанной зоне. Интегратор 8 с пороговым блоком 9 лужат для блокировки импульсов короче допустимой величины. В исходном состоянии триггеры 16,17 формирователей 14 и 15 в нуле и единице. Импульсы с генератора 3 периодически подтверждают эти состо5шия триггеров. Если длительность импульсов с выхо да фильтра 7 не превышает допустимой величины, то на выходе порогового блока 9 будет постоянно присутствовать низкий нулевой потенциал и триггеры 17 своего состояния не меняют. Если же длительность импульса на вь ходе фильтра 7 превьгсит допустимую величину, на выходе порогового блока 9 возникает сигнал, который поступает на тактовые входы, триггеров 17. Если в момент поступления этого сигнала на Д-входе одного из триггеров будет присутствовать низкий уровень (последний появляет ся на выходе схемы И-НЕ 11, если в сирнале присутствует звон О, и.на выходе схемы И-НЕ 12, если звон 1),то соответствующий триггер 17 также установится в нуль и тем самым подготовит к срабатыванию соответствующий триггер 16 по Д-входу. Это приводит к тому, что первый пришедший импульс на тактовый вход триггера 16 с генератфаимпульсов 3 установит его в единичное состояние, при котором засветится соответст вующий индикаторный элемент 18. Данное состояние продлится один период генератора 3, после чего следующий его импульс возвратит триггеры 16 а исходное нулевое состояние и соответствующий индикатс э погаснет. Воз1фат в исходное состоя триггеров 16 обеспечивается тем,что при срабатывании низкий потенциал с их инверсных выходов поступает на 5 -вход триггеров 17 и устанавливает их в единицу, тем самым подготавливая к уста-новке в нуль триггеры 16 по Д-входу. Триггер 1О вместе с инвертером 13 н с элементами 11 и 12 служит для бло|Юфовки выдачи сигнала звона, в случае Нормального сигнала. Нормальным сигналом считается следующая последовательность изменения уровней: нуль (0,4 В Нерабочий уровень (0,4 В; 2,4 В) единица (2,4 В) - нерабочий уровень - нуль и т.д. нуля будет восприниматьс следующая последовательность изменений уровней: нуль - нерабочий уровень -нульи как звон единицы , единица - нерабочий уровень - ешшица. Таким образом, при наличии в исследуемам сигнале звона, будет периодически вспыхивать тот из Ш1дикаторных элементов 18 (или оба сразу), который соответ ствует шределенному характеру звона, т.е. звону О или звону . Формула изобрете.ния 1. Устройство для проверки логических блоков, содержащее первый триггер, первы вход которого соединен с выходом генер Tqpa импульсов, выход через элемент от риианкя равнозначности - со входом перво го индикатора, второй -вход элемента отрицания равнозначности через согласующий блок соединен с выходом чувствительного элемента, второй выход согласующего бло ка подключен ко входу фильтра, а третий выход - ко второму нходу первого триггера, отличающееся тем, что, с целью увеличения полноты контроля, устройство содержит HHBepTqp, первый и второй элементы И-НЕ, интегратор, пороговый блок, первый и второй формировате ли сигналов и второй триггер, первый вхо JKOToporo подключен к выходу фильтра и через последовательно соединенные интег ратор и пороговый блок - к первым входам первого и второго формирователей сигналов, вторые входы которых подключены соответственно через первый и второй элементы И-НЕ к первому и второму выходам второго триггера, втqpoй нход первого элемента И-НЕ через инвертор соединен с вторым входом первого триггера, вторым входом второго триггера и вторым входом второго элемента И-НЕ, а третьи входы первого и второго формирователей сигналов с выходом генератора импульсов. 2.Устройство по п. 1, от л и ч а ющ е е с я тем, что формирователь сирналов содержит третий и четвертый триггеры и второй индикатор, вход которого подключен к первому выходу третьего триггера, второй выход которого соединен с первым входом четвертого триггера, выход KOTqporo подключен к первому входу третьего триггера, второй вход первого триггера соединен с третьим входом формирователя сигналов, первый и второй EVXOды четвертого триггера соединены соотверственно с первым и вторым входами формирователя сигналов. Источники информации, принятые во внимание при экспертизе 1. Патент Японии 4 4-3 07О4, кл. 54 (7), 1975. 2. Патент США № 375О015, кл. 340-146, 1976. 3.Журнал Приборы и системы управления, 1974, № 12, с. 38-29 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1989 |

|

SU1755377A1 |

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1987 |

|

SU1559415A1 |

| Устройство для автоматической настройки дугогасящего плунжерного реактора | 1986 |

|

SU1390704A1 |

| Устройство для моделирования каналов передачи дискретной информации | 1982 |

|

SU1049915A1 |

| Устройство для контроля фазировки электрических машин | 1988 |

|

SU1597796A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Логический пробник | 1984 |

|

SU1205085A1 |

| Устройство для измерения скорости телеграфирования | 1983 |

|

SU1167751A1 |

Авторы

Даты

1980-05-15—Публикация

1978-01-03—Подача