(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ КАНАЛОВ СВЯЗИ С ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с фискретными датчиками | 1975 |

|

SU611202A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2037964C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| Устройство для ввода информации | 1983 |

|

SU1128244A1 |

| Устройство для сопряжения вычислительной машины с импульсными датчиками | 1977 |

|

SU734651A1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Устройство для ввода информации от контактных датчиков | 1981 |

|

SU972498A1 |

| Устройство для сопряжения вычислительной машины с дискретными датчиками | 1978 |

|

SU694858A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU615472A1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

1

Изобретение относится к области технических средств сбора первичной информации в автоматизированных системах управления технологическими процессами, используемых в различных отраслях промышленности, где имеется большое число подлежаш,их контролю объектов и требуется обеспечить автоматический сбор и обработку информации.

Известны устройства для сопряжения каналов связи с электронной вычислительной машиной, содержашие п групп блоков хранения информации, группу элементов ИЛИ и генератор импульсов 1 и 2.

В известном устройстве спорадически возникаюшие сигналы о срабатывании датчиков поступают по каналам связи на соответствующие входы устройства и на первой стадии (стадии записи) каждое из них запоминается соответствуюш,им блоком хранения информации. На второй стадии (стадии выдачи сообшений) по команде генератора импульсов происходит передача сообшений на выход устройства в магистральный канал связи. В устройстве невозможна передача в магистральный канал связи одповременно нескольких сообшений, а следовательно, в этом канале отсутствуют искажения за счет наложения сообшений при передаче.

Недостатком известного устройства является то, что при передаче сообшений по его выходному магистральному каналу связи, особенно на большие расстояния и многоразрядных кодов сообшений, возможно возникновение другого рода искажений - перекрестных наводок по разрядным линиям. За счет емкостных и индуктивных связей между разрядными линиями канала из линий, по которым передаются единицы в разрядных кодах, наводятся помехи в линии, по которым сигналы не передаются - 15 параллельный двоичный код сообшения содержит в этих разрядах нули. Эта помеха наносит аддитивный характер и амплитуда напряжения помехи Un пропорциональна амплитуде полезного сигнала Ue и числу единиц в коде сообшения п. Поэтому при большем числе единиц в коде передаваемого сообшения амплитуда помехи становится соизмеримой с амплитудой полезного сигнала и на выходе канала связи не удается

разделить разряды, по которым передавались единицы, а по которым нули параллельного двоичного кода сообщения.

Целью изобретения является повышение надежности работы устройства.

Для достижения поставленной цели в устройство, содержащее группу элементов ИЛИ, п групп блоков памяти, генератор тактовых импульсов, причем выходы элементов ИЛИ группы соединены с первым входом соответствующих блоков памяти первой группы, входы элементов ИЛИ группы и вторые входы блоков памяти первой группы являются входами устройства, первые и вторые выходы блоков хранения предыдущей группы соединены, соответственно с первыми и вторыми входами блоков памяти последующей группы, третий вход предыдущего блока памяти каждой группь подключен к третьему выходу последующего блока памяти каждой группы, кроме последнего, а третий вход последнего блока памяти предыдущей группы, кроме последнего блока памяти последней группы соединен с третьим выходом первого блока памяти последующей группы, а третий вход последнего блока памяти последней группы подключен к выходу генератора тактовых импульсов, введен блока управления передачей, содержащий группы триггеров приема группу триггеров выдачи, первую и вторую и третью группу элементов И, группу одновибраторов, группу элементов задержки, элемент ИЛИ, элемент И, первый, второй и третий элементы задержки, одновибратор, причем первые входы триггеров приема и входы элемента ИЛИ подключены соответственно к четвертым выходам блоков памяти п групп, первые входы каждого триггера приема соединены с первым выходом одновибратора, первый выход каждого триггера приема подключен к первому входу соответствующего элемента И первой группы, второй выход каждого триггера приема соединен с первым входом соответствующего элемента И второй группы, выход предыдущего элемента И первой группы соединен со вторым входом последующего элемента И первой группы, вторые входы элементов И второй группы, кроме первого, подключены ко входам соответствующих элементов, задержки триггеров, кроме последнего, и выходом соответствующих элементов И первой группы, выходы элементов И второй группы соединены со входом соответствующих элементов задержки группы и первым входом соответствующих триггеров выдачи, вторые входы первых элементов И первой и второй группы соединены с первым входом первого элемента задержки и подключены к выходу второго элемента задержки, вход которого соединен с выходом элемента ИЛИ, выходы последнего элемента И первой группы и последнего элемента задержки группы подключены

ко входу третьего элемента задержки, выход которого подключен ко входу одновибратора, второй выход которого соединен со входом генератора тактовых импульсов, третий выход одновибратрра соединен с первым входом элемента И, второй вход которого подключен к выходу первого элемента задержки, выход элемента И подключен ко второму входу первого элемента задержки и первым входам элементов И третьей группы, вторые входь которых соединены с выходами соответствующих триггеров выдачи, а выходы элементов И третьей группы соединены со вторыми входами соответствующих триггеров выдачи и входом одновибраторов группы, выходы которых являются вы, ходами устройства.

Блок управления передачей преобразует передаваемый параллельный код сообщения в последовательно-параллельный код. В устройстве для минимизации времени передачи, число разрядов в передаваемых последовательно частичных кодах сообщения не остается постоянным. Устройство обеспечивает передачу каждый раз стольких разрядов кодов, число единиц в которых максимально приближается или равно допустимому для передачи числу единиц.

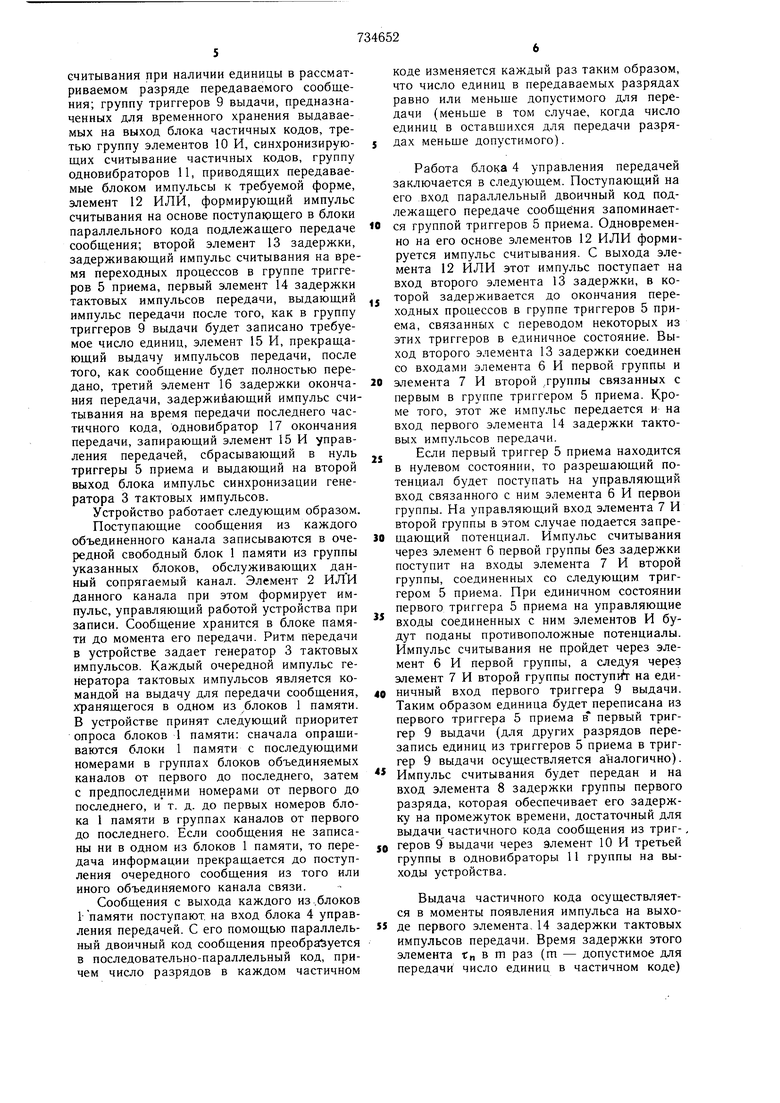

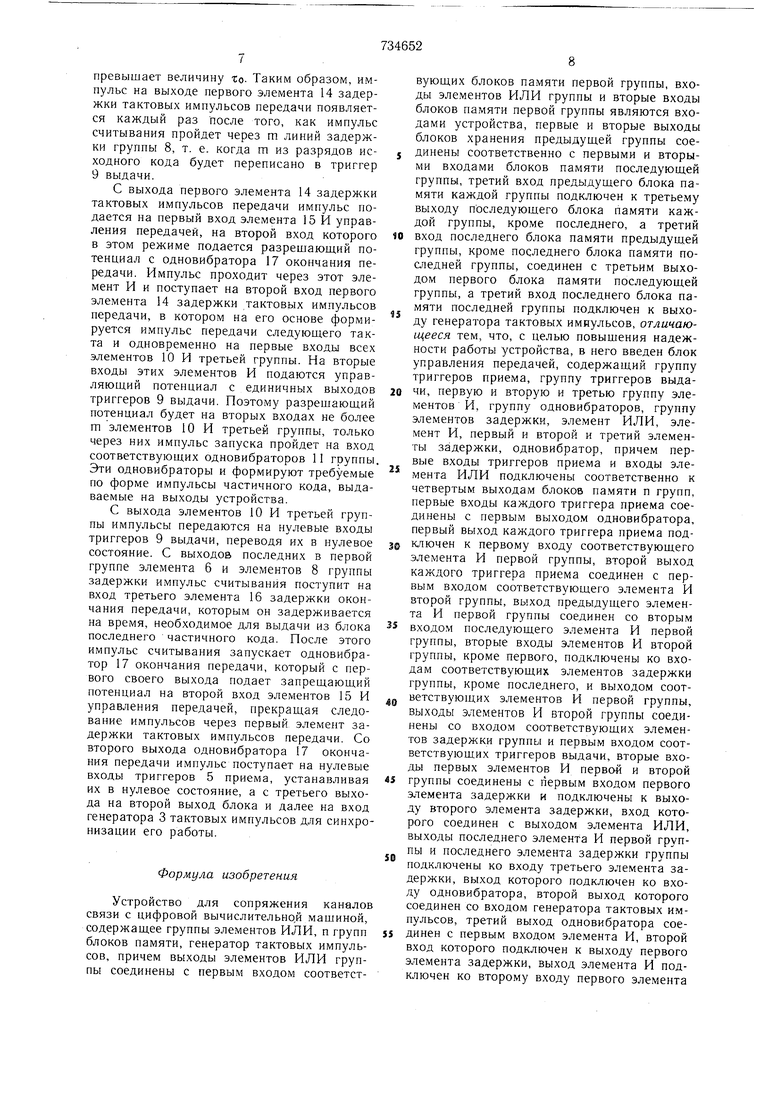

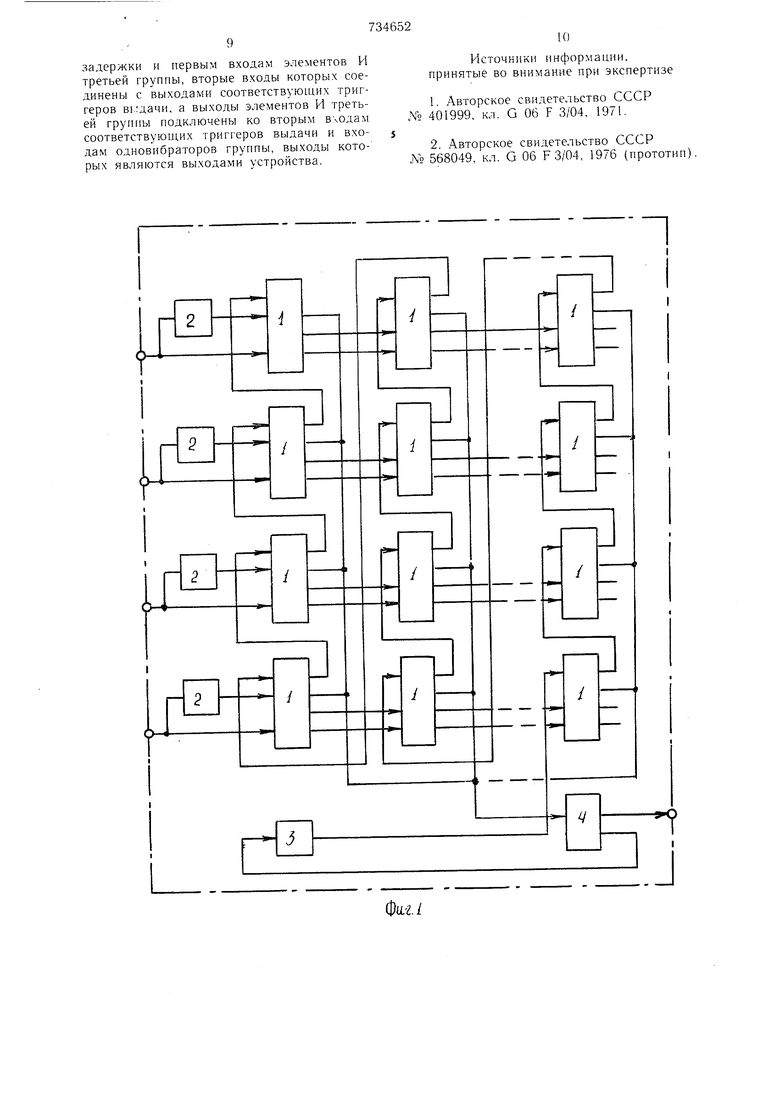

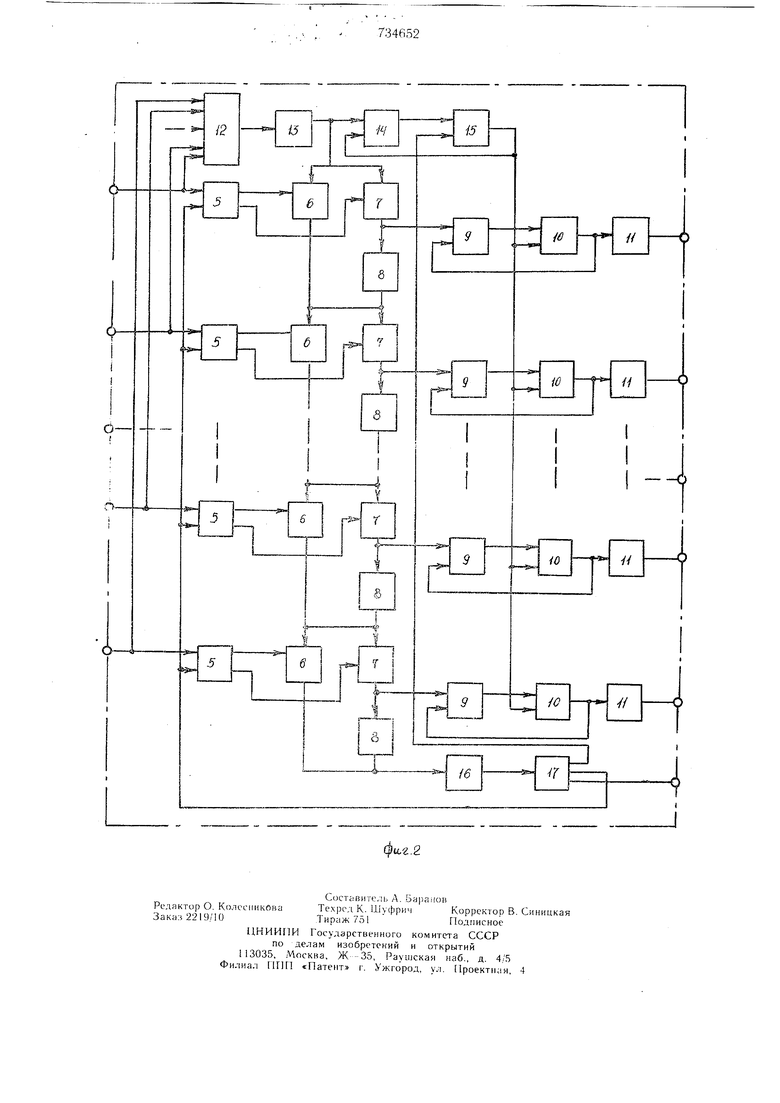

На фиг. I представлена структурная схема устройства; на фиг. 2 - структурная схема блока управления передачей.

Устройство для сопряжения каналов свя- зи с электронной вычислительной мащиной (фиг. 1) содержит п групп блоков 1 памяти, предназначенных для временного хранения поступающей с объединяемых каналов связи информации; группу элементов 2 ИЛИ, формирующих одиночный импульс при каждом поступлении информации из объединяемого канала, генератор 3 тактовых импульсов, задающий ритм выдачи информации на выход устройства, блок 4 управления передачей преобразующий параллельный двоичный код подлежащих передаче сообщений в последовательно-параллельный код, число разрядов в частичных кодах которого определяется тем условием, что количество единиц в них максимально приближается или равно допустимому для передачи. Этот блок синхронизирует работу генератора 3 тактовых импульсов.

Схема блока управления передачей содержит группу триггеров 5 приема (по числу разрядов в параллельном коде передаваемых сообщений) которыми запоминаются разряды подлежащих передаче сообщений, первую группу элементов б И, через которые проходит импульс считывания в нулевых разрядах передаваемого кода, вторую

группу элементов 7 И, пропускающих импульс считывания в разрядах, в которых передаваемое сообщение содержит единицы, группу элементов 8 задержки, обеспечивающих требуемую задержку импульса

считывания при наличии единицы в рассматриваемом разряде передаваемого сообщения; группу триггеров 9 выдачи, предназначенных для временного хранения выдаваемых на выход блока частичных кодов, третью группу элементов 10 И, синхронизирующих считывание частичных кодов, группу одновибраторов 11, приводящих передаваемые блоком импульсы к требуемой форме, элемент 12 ИЛИ, формирующий импульс считывания на основе поступающего в блоки параллельного кода подлежащего передаче сообщения; второй элемент 13 задержки, задерживающий импульс считывания на время переходных процессов в группе триггеров 5 приема, первый элемент 14 задержки тактовых импульсов передачи, выдающий импульс передачи после того, как в группу триггеров 9 выдачи будет записано требуемое число единиц, элемент 15 И, прекращающий выдачу импульсов передачи, после того, как сообщение будет полностью передано, третий элемент 16 задержки окончания передачи, задерживающий импульс считывания на время передачи последнего частичного кода, одновибратор 17 окончания передачи, запирающий элемент 15 И управления передачей, сбрасывающий в нуль триггеры 5 приема и выдающий на второй выход блока импульс синхронизации генератора 3 тактовых импульсов.

Устройство работает следующим образом.

Поступающие сообщения из каждого объединенного канала записываются в очередной свободный блок 1 памяти из группы указанных блоков, обслуживающих данный сопрягаемый канал. Элемент 2 ИЛИ данного канала при этом формирует импульс, управляющий работой устройства при записи. Сообщение хранится в блоке памяти до момента его передачи. Ритм передачи в устройстве задает генератор 3 тактовых импульсов. Каждый очередной импульс генератора тактовых импульсов является командой на выдачу для передачи сообщения, хранящегося в одном из блоков 1 памяти. В устройстве принят следующий приоритет опроса блоков 1 памяти: сначала опращиваются блоки 1 памяти с последующими номерами в группах блоков объединяемых каналов от первого до последнего, затем с предпоследними номерами от первого до последнего, и т. д. до первых номеров блока 1 памяти в группах каналов от первого до последнего. Если сообщения не записаны ни в одном из блоков 1 памяти, то передача информации прекращается до поступления очередного сообщения из того или иного объединяемого канала связи.

Сообщения с выхода каждого из .блоков 1- памяти поступают на вход блока 4 управления передачей. С его помощью параллельный двоичный код сообщения преобразуется в последовательно-параллельный код, причем число разрядов в каждом частичном

коде изменяется каждый раз таким образом, что число единиц в передаваемых разрядах равно или меньще допустимого для передачи (меньше в том случае, когда число единиц в оставшихся для передачи разрядах меньше допустимого).

Работа блока 4 управления передачей заключается в следующем. Поступающий на его вход параллельный двоичный код подлежащего передаче сообщения запоминаето ся группой триггеров 5 приема. Одновременно на его основе элементов 12 ИЛИ формируется импульс считывания. С выхода элемента 12 ИЛИ этот импульс поступает на вход второго элемента 13 задержки, в которой задерживается до окончания переходных процессов в группе триггеров 5 приема, связанных с переводом некоторых из этих триггеров в единичное состояние. Выход второго элемента 13 задержки соединен со входами элемента б И первой группы и

0 элемента 7 И второй .группы связанных с первым в группе триггером 5 приема. Кроме того, этот же импульс передается и на вход первого элемента 14 задержки тактовых импульсов передачи.

J Если первый триггер 5 приема находится в нулевом состоянии, то разрещающий потенциал будет поступать на управляющий вход связанного с ним элемента 6 И первой группы. На управляющий вход элемента 7 И второй группы в этом случае подается запреO щающий потенциал. Импульс считывания через элемент 6 первой группы без задержки поступит на в.чоды элемента 7 И второй группы, соединенных со следующим триггером 5 приема. При единичном состоянии первого триггера 5 приема на управляющие входы соединенных с ним элементов И будут поданы противоположные потенциалы. Импульс считывания не пройдет через элемент 6 И первой группы, а следуя через элемент 7 И второй группы поступит на единичный вход первого триггера 9 выдачи. Таким образом единица будет переписана из первого триггера 5 приема в первый триггер 9 выдачи (для других разрядов перезапись единиц из триггеров 5 приема в триггер 9 выдачи осуществляется аналогично).

Импульс считывания будет передан и на вход элемента 8 задержки группы первого разряда, которая обеспечивает его задержку на промежуток времени, достаточный для выдачи частичного кода сообщения из триг-,

0 геров 9 выдачи через элемент 10 И третьей группы в одновибраторы 11 группы на выходы устройства.

Выдача частичного кода осуществляется в моменты появления импульса на выхоS де первого элемента, 14 задержки тактовых импульсов передачи. Время задержки этого элемента t в ш раз (т - допустимое для передачи число единиц в частичном коде)

превышает величину TO. Таким образом, импульс на выходе первого элемента 14 задержки тактовых импульсов передачи появляется каждый раз после того, как импульс считывания пройдет через m линий задержки группы 8, т. е. когда гп из разрядов исходного кода будет переписано в триггер 9 выдачи.

С выхода первого элемента 14 задержки тактовых импульсов передачи импульс подается на первый вход элемента 15 И управления передачей, на второй вход которого в этом режиме подается разрешающий потенциал с одновибратора 17 окончания передачи. Импульс проходит через этот элемент И и поступает на второй вход первого элемента 14 задержки тактовых импульсов передачи, в котором на его основе формируется импульс передачи следующего такта и одновременно на первые входы всех элементов 10 И третьей группы. На вторые входы этих элементов И подаются управляющий потенциал с единичных выходов триггеров 9 выдачи. Поэтому разрешающий потенциал будет на вторых входах не более гп элементов 10 И третьей группы, только через них импульс запуска пройдет на вход соответствующих одновибраторов 11 группы. Эти одновибраторы и формируют требуемые по форме импульсы частичного кода, выдаваемые на выходы устройства.

С выхода элементов 10 И третьей группы импульсы передаются на нулевые входы триггеров 9 выдачи, переводя их в нулевое состояние. С выходов последних в первой группе элемента 6 и элементов 8 группы задержки импульс считывания поступит на вход третьего элемента 16 задержки окончания передачи, которым он задерживается на время, необходимое для выдачи из блока последнего частичного кода. После этого импульс считывания запускает одновибратор 17 окончания передачи, который с первого своего выхода подает запрещающий потенциал на второй вход элементов 15 И управления передачей, прекращая следование импульсов через первый элемент задержки тактовых импульсов передачи. Со второго выхода одновибратора 17 окончания передачи импульс поступает на нулевые входы триггеров 5 приема, устанавливая их в нулевое состояние, а с третьего выхода на второй выход блока и далее на вход генератора 3 тактовых импульсов для синхронизации его работы.

Формула изобретения

Устройство для сопряжения каналов связи с цифровой вычислительной машиной, содержащее группы элементов ИЛИ, п групп блоков памяти, генератор тактовых импульсов, причем выходы элементов ИЛИ группы соединены с первым входом соответствующих блоков памяти первой группы, входы элементов ИЛИ группы и вторые входы блоков памяти первой группы являются входами устройства, первые и вторые выходы блоков хранения предыдущей группы соединены соответственно с первыми и вторыми входами блоков памяти последующей группы, третий вход предыдущего блока памяти каждой группы подключен к третьему выходу последующего блока памяти каждой группы, кроме последнего, а третий

вход последнего блока памяти предыдущей группы, кроме последнего блока памяти последней группы, соединен с третьим выходом первого блока памяти последующей группы, а третий вход последнего блока памяти последней группы подключен к выходу генератора тактовых имнульсов, отличающееся тем, что, с целью повышения надежности работы устройства, в него введен блок управления передачей, содержащий группу триггеров приема, группу триггеров выдачи, первую и вторую и третью группу элементов И, группу одновибраторов, группу элементов задержки, элемент ИЛИ, элемент И, первый и второй и третий элементы задержки, одновибратор, причем первые входы триггеров приема и входы элемента ИЛИ подключены соответственно к четвертым выходам блоков памяти п групп, первые входы каждого триггера приема соединены с первым выходом одновибратора, первый выход каждого триггера приема подключен к первому входу соответствующего элемента И первой группы, второй выход каждого триггера приема соединен с первым входом соответствующего элемента И второй группы, выход предыдущего элемента И первой группы соединен со вторым входом последующего элемента И первой группы, вторые входы элементов И второй группы, кроме первого, подключены ко входам соответствующих элементов задержки группы, кроме последнего, и выходом соответствующих элементов И первой группы, выходы элементов И второй группы соединены со входом соответствующих элементов задержки группы и первым входом соответствующих триггеров выдачи, вторые входы первых элементов И первой и второй группы соединены с первым входом первого элемента задержки и подключены к выходу второго элемента задержки, вход которого соединен с выходом элемента ИЛИ, выходы последнего элемента И первой группы и последнего элемента задержки группы

O подключены ко входу третьего элемента задержки, выход которого подключен ко входу одновибратора, второй выход которого соединен со входом генератора тактовых импульсов, третий выход одновибратора соединен с первым входом элемента И, второй вход которого подключен к выходу первого элемента задержки, выход элемента И подключен ко второму входу первого элемента

9

задержки и первым входам элементов И третьей группы, вторые входы которых соединены с выходами соответствующих триггеров В1-:дачи, а выходы элементов И третьей группы подключены ко вторым входам соответствуюпшх триггеров выдачи и входам одновибраторов группы, выходы которых являются выходами устройства.

К)

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-05-15—Публикация

1977-12-12—Подача