Изобретение относится к автоматике и цифровой вычислительной технике и может найти применение при построении управляющих и вычислительных систем высокой производительности, в том числе систем с массовым параллелизмом, а также подсистем логического управления многоуровневых иерархических автоматизированных систем управления объектами и коллективами объектов широкого класса.

Известно микропрограммное устройство дня управления обменом управляющей информации в распределенной системе, включающее блок памяти микропрограмм, регистры адреса, микрокоманд и приема, буферный запоминающий блок, блок регистров, коммутаторы адреса, выходной и микрокоманд, генератор констант, схему сравнения, мультиплексор логических условий, генератор тактовых импульсов, триггер запуска, элемент задержки, с первого по третий элементы И, первый и второй блоки элементов И, с первого по четвертый элементы ИЛИ и одновибратор (авт. св. 1325477 СССР, кл. G 06 F 9/22, опубл. 23.07.87, БИ N 27).

Недостатком указанного устройства является узкая область применения, обусловленная отсутствием средств синхронизации завершения параллельных ветвей (участков) микропрограмм, закрепленных за различными модулями управляющих систем, формируемых на его основе.

Наиболее близким к предлагаемому устройству по технической сущности является модуль микроконтроллерной сети, содержащий блок памяти микропрограмм, регистры адреса и микрокоманд, мультиплексор логических условий, генератор констант, триггер запуска, первую и вторую схемы сравнения, первый и второй генераторы тактовых импульсов, первый и второй буферные запоминающие блоки, коммутатор адреса, первый и второй выходные коммутаторы, регистр-счетчик событий, триггеры переключения каналов, управления синхронизацией и блокировки, триггер, с первого по четырнадцатый элементы И, с первого по седьмой элементы ИЛИ, с первого по пятый элементы задержки, с первого по третий одновибраторы, элемент ИЛИ-НЕ (патент России N 2112272, кл. G 06 F 9/22, опубл. 27.05.98, БИ N 15).

Недостатком указанного модуля является невысокая оперативность синхронизации параллельных участков при функционировании модуля в составе (мульти)микроконтроллерной сети (обусловленная значительным временем между моментом фактического завершения параллельных участков и моментом появления соответствующего сигнала-признака).

Технической задачей изобретения является повышение оперативности синхронизации параллельных участков микропрограмм в мультимикроконтроллерной сети на основе минимизации времени между моментом завершения параллельных участков и моментом появления соответствующего сигнала-признака при одновременном упрощении модуля.

Техническая задача решается тем, что в модуль мультимикроконтроллерной сети, содержащий блок памяти микропрограмм, регистр микрокоманд, регистр адреса, мультиплексор логических условий, буферный запоминающий блок, первый генератор констант, схему сравнения, триггер запуска, коммутатор адреса, первый генератор тактовых импульсов, второй генератор тактовых импульсов, выходной коммутатор, триггер, с первого по пятый элементы И, с первого по пятый элементы ИЛИ, одновибратор, с первого по третий элементы задержки, причем прямой выход триггера запуска подключен к входу первого генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход которого подключен к информационному входу регистра микрокоманд, выход кода логических условий которого подключен к адресному входу мультиплексора логических условий, первый информационный вход которого соединен с выходом модифицируемого разряда адреса регистра микрокоманд, выход микроопераций которого соединен с выходом микроопераций модуля, вход логических условий модуля подключен ко второму информационному входу мультиплексора логических условий, выход которого в объединении с выходом немодифицируемой части адреса регистра микрокоманд соединен с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, второй выход первого генератора тактовых импульсов подключен к входу одновибратора и к входу синхронизации регистра микрокоманд, выход метки управления синхронизацией которого соединен с первым входом первого элемента ИЛИ, вход пуска модуля соединен с первым входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого подключен к выходу одновибратора, а выход соединен с входом сброса триггера запуска, выход метки конца участка регистра микрокоманд подключен ко второму входу первого элемента ИЛИ, ко второму входу первого элемента И, к первому входу третьего элемента ИЛИ, а также к первому и второму управляющим входам коммутатора адреса, второй информационный вход которого соединен с входом кода операции модуля, выход передачи управления регистра микрокоманд соединен с первым информационным входом выходного коммутатора, вход приема управления модуля образован входом адреса приема управления модуля, входом номера приемника управления модуля и линией синхронизации модуля, которая соединена с входом первого элемента задержки, выход которого соединен с первым входом третьего элемента И, выход которого подключен к входу синхронизации записи буферного запоминающего блока, информационный вход которого соединен с входом приема управления модуля, вход адреса приема управления модуля подключен к третьему информационному входу коммутатора адреса, выход первого генератора констант соединен с первым входом схемы сравнения, второй вход которой подключен к входу номера приемника управления модуля, а выход соединен со вторым входом третьего элемента И и с третьим управляющим входом коммутатора адреса, выход метки передачи управления регистра микрокоманд подключен к третьему входу первого элемента ИЛИ, к первому входу четвертого элемента И и к первому управляющему входу выходного коммутатора, выход метки конца операции регистра микрокоманд подключен к третьему входу первого элемента И, к выходу конца операции модуля, к четвертому и пятому управляющим входам коммутатора адреса, к четвертому входу первого элемента ИЛИ и ко второму входу третьего элемента ИЛИ, выход которого соединен с шестым управляющим входом коммутатора адреса, первый выход второго генератора тактовых импульсов подключен ко второму входу четвертого элемента И и к входу установки триггера, инверсный выход которого соединен с третьим управляющим входом выходного коммутатора, выход которого соединен с выходом передачи управления модуля, второй выход второго генератора тактовых импульсов подключен к входу сброса триггера и к первому входу пятого элемента И, выход которого соединен с входом второго элемента задержки, выход которого подключен к входам синхронизации сдвига и разрешения сдвига буферного запоминающего блока, выход которого соединен со вторым информационным входом выходного коммутатора и с входами четвертого элемента ИЛИ, выход которого подключен к четвертому управляющему входу выходного коммутатора и ко второму входу пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого соединен с выходом передачи управления модуля, выход четвертого элемента И подключен ко второму входу пятого элемента ИЛИ и к входу третьего элемента задержки, выход которого соединен со вторым входом второго элемента ИЛИ, дополнительно введены второй генератор констант, дешифратор номера вершины синхронизации, с первой по третью группы элементов И, первая и вторая группы элементов ИЛИ, причем второй управляющий вход выходного коммутатора соединен с прямым выходом триггера, выход схемы равнения подключен к третьему входу второго элемента ИЛИ, выход которого соединен с входом синхронизации триггера запуска, информационный вход которого подключен к шине логической единицы, выход метки управления синхронизацией регистра микрокоманд соединен с первыми входами элементов И первой группы с первого по n-й (где n - максимальное число вершин синхронизации в микропрограммах), выходы второго генератора констант с первого по n-й подключены к первым входам элементов ИЛИ первой группы с первого по n-й соответственно, выход номера вершины синхронизации регистра микрокоманд подключен к входу дешифратора номера вершины синхронизации, выходы с первого по n-й которого соединены со вторыми входами элементов И первой группы с первого по n-й соответственно и со вторыми входами элементов ИЛИ первой группы с первого по n-й соответственно, выходы элементов И первой группы с первого по n-й подключены к первым входам элементов ИЛИ второй группы с первого по n-й соответственно и к первым входам элементов И второй группы с первого по n-й соответственно, выходы которых соединены с группой входов второго элемента ИЛИ, входы управления синхронизацией модуля с первого по n-й подключены ко вторым входам элементов И второй группы с первого по n-й соответственно и ко вторым входам элементов ИЛИ второй группы с первого по n-й соответственно, выходы элементов ИЛИ первой группы с первого по n-й соединены с первыми входами элементов И третьей группы с первого по n-й соответственно, вторые входы которых подключены к выходам элементов ИЛИ второй группы с первого по n-й соответственно, а выходы соединены с выходами управления синхронизацией модуля с первого по n-й соответственно.

Сущность изобретения состоит в следующем.

Предлагаемый модуль совместно с другими идентичными модулями объединяется в кольцевую структуру, предназначенную для управления функционально сложными объектами (предполагающими параллельное и асинхронное протекание во времени множества процессов) и называемую мультимикроконтроллерной сетью (ММКС). ММКС реализует совокупность различных микропрограмм. Номер выполняемой микропрограммы определяется кодом операции (КОП), который формируется устройством управления верхнего уровня (УУВУ), например центральным процессором, и представляет собой адрес первой микрокоманды. Каждая из микропрограмм в общем случае содержит множество параллельных и последовательных участков, определенным образом распределенных между модулями сети. Каждый модуль ММКС выполняется в виде СБИС с внутренней перепрограммируемой памятью микропрограмм и обеспечивает возможность управления последовательным процессом (реализации последовательного участка микропрограммы), активизации параллельных или последовательных процессов (участков) в других аналогичных модулях (межмодульной передачи управления), а также синхронизации завершения определенных подмножеств параллельных участков микропрограмм. Модули мультимикроконтроллерной сети идентифицируются логическими номерами 0, 1, 2,..., N-1, где N - число идентичных модулей в составе ММКС.

В ходе функционирования модули ММКС вырабатывают последовательности микрокоманд, порядок следования которых задается значениями сигналов логических условий (ЛУ), поступающих от объекта(ов) управления (ОУ). Межмодульная передача управления в ММКС осуществляется аналогично прототипу. Модуль с логическим номером i (далее - i-й модуль или модуль mi), являющийся инициатором передачи управления, вырабатывает специальную управляющую микрокоманду (сообщение) М, которая включает номер модуля-приемника управления (k) и соответствующий адрес передачи управления Aпу. Эта микрокоманда передается через последовательность модулей в кольцевой структуре ММКС до тех пор, пока номер k не совпадет с номером одного из модулей (таким модулем будет mk). После достижения микрокомандой М модуля mk последний выделяет в ее формате адрес Aпу и начинает выполнение микропрограммы с данного адреса.

Процесс синхронизации параллельных участков микропрограмм в ММКС на основе предлагаемого модуля отличается от аналогичного процесса для сети на базе прототипа. В отличие от прототипа, где синхронизация обеспечивается за счет модификации специальной микрокоманды Z, содержащей код количества синхронизируемых участков, которая перемещается по кольцу сети, в предлагаемом модуле синхронизация осуществляется на основе передачи сигналов-признаков опроса через отдельные каналы управления синхронизацией, каждый из которых соответствует определенной точке (вершине) синхронизации параллельных участков.

Для обеспечения синхронизации произвольных групп параллельных участков за каждым модулем ММКС mi, закрепляется вектор Si = (s1 i, s2 i,..., sn i), задающий соответствие между вершинами синхронизации параллельных участков и i-м модулем, где  , n1 - число вершин синхронизации в 1-й микропрограмме, Q - число микропрограмм, реализуемых ММКС. Значение компоненты sq i,

, n1 - число вершин синхронизации в 1-й микропрограмме, Q - число микропрограмм, реализуемых ММКС. Значение компоненты sq i,  , вектора Si определяется следующим образом:

, вектора Si определяется следующим образом:

sq i = 0, если за i-м модулем закреплен участок, завершающийся q-й вершиной синхронизации;

sq i = 1, если i-й модуль не выполняет ни одного участка из множества участков, завершающихся (сходящихся) в q-й вершине синхронизации (или q-я вершина не входит в текущую микропрограмму, что имеет место тогда, когда n1 < q, где 1 - номер текущей микропрограммы).

В группе модулей  , реализующих группу синхронизируемых участков Λq= {L

, реализующих группу синхронизируемых участков Λq= {L . Данному модулю присваивается статус ведущего по отношению к вершине аq. Остальные модули соответственно получают статус ведомых. Функцией ведущего модуля является управление синхронизацией параллельных участков L1 q, L2 q,..., Lp q. Функция ведомых модулей состоит в индикации состояния закрепленных за ними участков.

. Данному модулю присваивается статус ведущего по отношению к вершине аq. Остальные модули соответственно получают статус ведомых. Функцией ведущего модуля является управление синхронизацией параллельных участков L1 q, L2 q,..., Lp q. Функция ведомых модулей состоит в индикации состояния закрепленных за ними участков.

Процесс синхронизации участков L1 q, L2 q,..., Lp q протекает следующим образом. Ведущий модуль  , завершая выполнение соответствующего участка Lh q, вырабатывает сигнал-признак

, завершая выполнение соответствующего участка Lh q, вырабатывает сигнал-признак  опроса состояния параллельных участков. Сигнал-признак

опроса состояния параллельных участков. Сигнал-признак  последовательно распространяется по цепочке модулей ММКС, следующих за ведущим. Распространение сигнала-признака

последовательно распространяется по цепочке модулей ММКС, следующих за ведущим. Распространение сигнала-признака  через некоторый модуль mk зависит от значения компоненты sq k вектора Sk (соответствующего k-му модулю). Если sq k = 1, то признак

через некоторый модуль mk зависит от значения компоненты sq k вектора Sk (соответствующего k-му модулю). Если sq k = 1, то признак  безусловно передается на выход k-го модуля (k-й модуль не влияет на процесс синхронизации параллельных участков L1 q, L2 q,..., Lp q). Если sq k = 0, то k-й модуль реализует некоторый участок L

безусловно передается на выход k-го модуля (k-й модуль не влияет на процесс синхронизации параллельных участков L1 q, L2 q,..., Lp q). Если sq k = 0, то k-й модуль реализует некоторый участок L через модуль mk определяется значением признака gq k состояния участка Lv q. При gq k = 0 (участок Lv q не завершен) распространение сигнала-признака

через модуль mk определяется значением признака gq k состояния участка Lv q. При gq k = 0 (участок Lv q не завершен) распространение сигнала-признака  приостанавливается.

приостанавливается.

Как только gq k приобретает единичное значение, признак  передается следующему модулю ММКС. Аналогичным образом сигнал-признак

передается следующему модулю ММКС. Аналогичным образом сигнал-признак  распространяется через остальные модули сети и после окончания всех параллельных участков группы Λq проявляется на входе ведущего модуля

распространяется через остальные модули сети и после окончания всех параллельных участков группы Λq проявляется на входе ведущего модуля  . После получения признака

. После получения признака  модуль

модуль  возобновляет исполнение микропрограммы - синхронизация группы параллельных участков Λq обеспечена.

возобновляет исполнение микропрограммы - синхронизация группы параллельных участков Λq обеспечена.

Распространение сигналов-признаков опроса и управляющих микрокоманд М, используемых при передаче управления, происходит независимо. Кроме того, возможно одновременное распространение сигналов-признаков опроса в нескольких каналах управления синхронизацией, что позволяет обеспечить одновременную синхронизацию нескольких групп параллельных участков (групп участков, сходящихся к разным вершинам синхронизации).

Поскольку в предлагаемом модуле в отличие от прототипа при синхронизации отсутствует обмен сообщениями и, следовательно, отсутствует необходимость промежуточного хранения таких сообщений в буферных блоках, время между моментом окончания всех параллельных участков L1 q, L2 q,..., Lp q и моментом получения признака окончания участков ведущим модулем снижается. Оно фактически определяется только задержкой распространения сигнала-признака  через последовательность модулей ММКС. При этом цепь распространения сигнала

через последовательность модулей ММКС. При этом цепь распространения сигнала  в каждом промежуточном модуле (как будет показано ниже) включает два логических элемента. Таким образом, имеет место повышение оперативности процесса синхронизации. Оценка преимуществ предлагаемого модуля перед прототипом приведена в конце описания.

в каждом промежуточном модуле (как будет показано ниже) включает два логических элемента. Таким образом, имеет место повышение оперативности процесса синхронизации. Оценка преимуществ предлагаемого модуля перед прототипом приведена в конце описания.

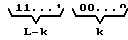

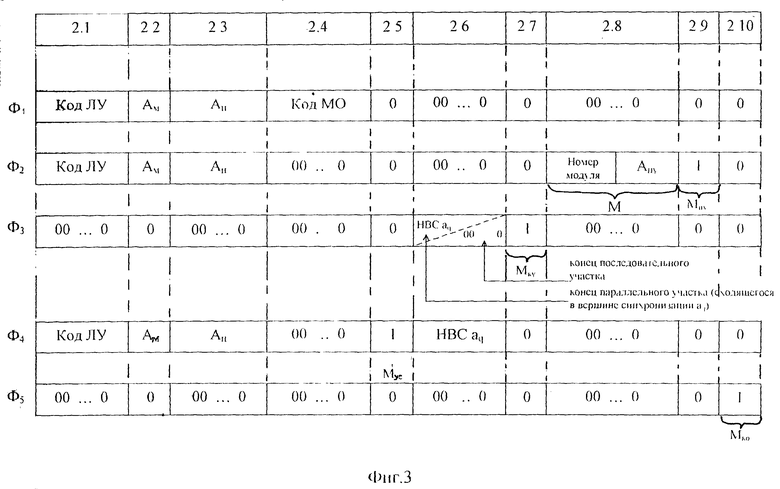

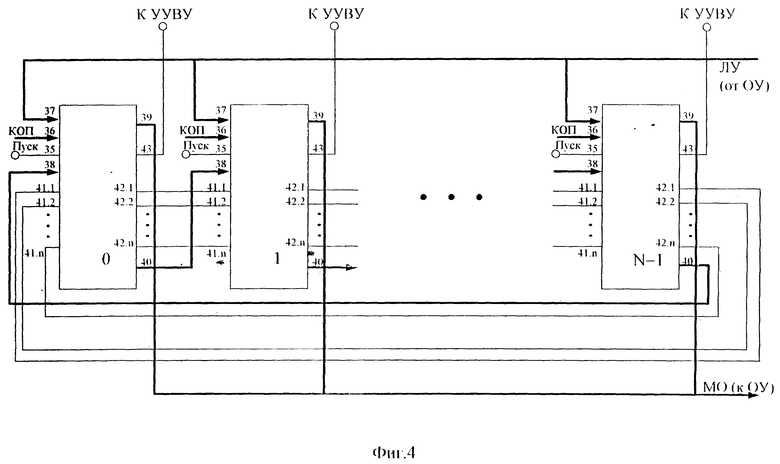

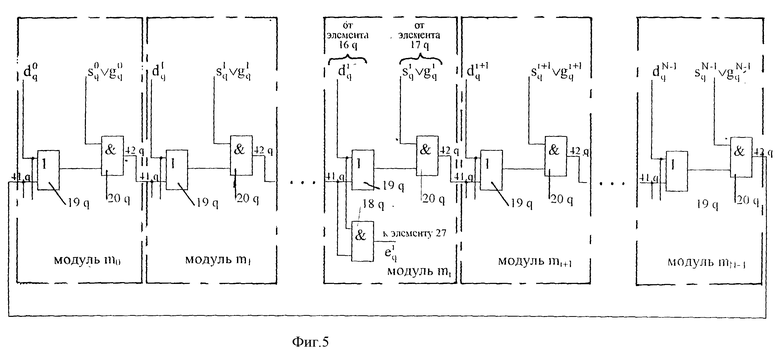

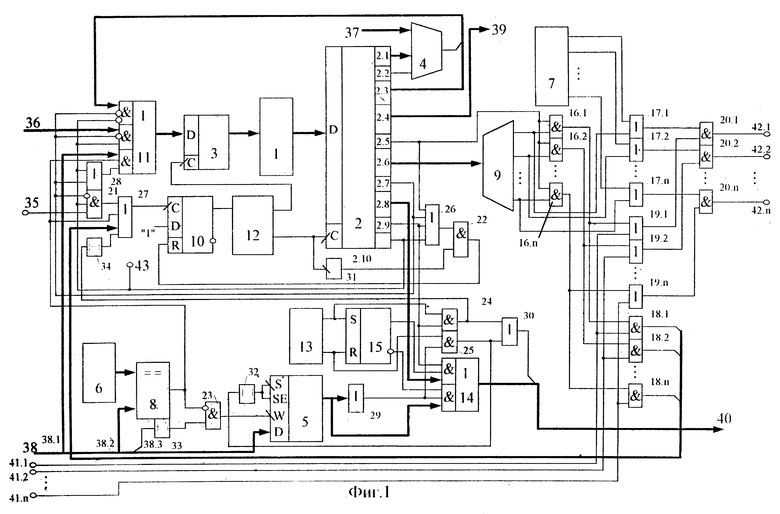

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема модуля мультимикроконтроллерной сети; на фиг. 2 показана функциональная схема буферного запоминающего блока; на фиг. 3 представлены форматы микрокоманд, реализуемые модулем; на фиг. 4 дана структурная схема мультимикроконтроллерной сети, построенной на основе предлагаемого модуля; на фиг. 5 приведена схема канала управления синхронизацией ММКС.

Модуль мультимикроконтроллерной сети (фиг.1) содержит блок 1 памяти микропрограмм, регистр 2 микрокоманд с выходами 2.1 кода логических условий, 2.2 модифицируемого разряда адреса, 2.3 немодифицируемой части адреса, 2.4 микроопераций, 2.5 метки управления синхронизацией, 2.6 номера вершины синхронизации, 2.7 метки конца участка, 2.8 передачи управления, 2.9 метки передачи управления, 2.10 метки конца операции, регистр 3 адреса, мультиплексор 4 логических условий, буферный запоминающий блок 5, первый генератор 6 констант, схему 8 сравнения, триггер 10 запуска, коммутатор 11 адреса, первый генератор 12 тактовых импульсов, второй генератор 13 тактовых импульсов, выходной коммутатор 14, триггер 15, первый 21, второй 22, третий 23, четвертый 24 и пятый 25 элементы И, первый 26, второй 27, третий 28, четвертый 29 и пятый 30 элементы ИЛИ, одновибратор 31, первый 33, второй 32 и третий 34 элементы задержки, причем прямой выход триггера 10 запуска подключен к входу генератора 12 тактовых импульсов, первый выход которого соединен с входом синхронизации регистра 3 адреса, выход которого соединен с адресным входом блока 1 памяти микропрограмм, выход которого подключен к информационному входу регистра 2 микрокоманд, выход 2.1 кода логических условий которого подключен к адресному входу мультиплексора 4 логических условий, первый информационный вход которого соединен с выходом 2.2 модифицируемого разряда адреса регистра 2 микрокоманд, выход 2.4 микроопераций которого соединен с выходом 39 микроопераций модуля, вход 37 логических условий модуля подключен ко второму информационному входу мультиплексора 4 логических условий, выход которого в объединении с выходом 2.3, немодифицируемой части адреса регистра 2 микрокоманд соединен с первым информационным входом коммутатора 11 адреса, выход которого соединен с информационным входом регистра 3 адреса, второй выход генератора 12 тактовых импульсов подключен к входу одновибратора 31 и к входу синхронизации регистра 2 микрокоманд, выход 2.5 метки управления синхронизацией которого соединен с первым входом элемента ИЛИ 26, вход 35 пуска модуля соединен с первым входом элемента И 21, выход которого подключен к первому входу элемента ИЛИ 27, выход элемента ИЛИ 26 соединен с первым входом элемента И 22, второй вход которого подключен к выходу одновибратора 31, а выход соединен с входом сброса триггера 10 запуска, выход 2.7 метки конца участка регистра 2 микрокоманд подключен ко второму входу элемента ИЛИ 26, ко второму (инверсному) входу элемента И 21, к первому входу элемента ИЛИ 28, а также к первому и второму управляющим входам коммутатора 11 адреса, второй информационный вход которого соединен с входом 36 кода операции модуля, выход 2.8 передачи управления регистра 2 микрокоманд соединен с первым информационным входом выходного коммутатора 14, вход 38 приема управления модуля образован входом 38.1 адреса приема управления модуля, входом 38.2 номера приемника управления модуля и линией 38.3 синхронизации модуля, которая соединена с входом элемента 33 задержки, выход которого соединен с первым входом элемента И 23, выход которого подключен к входу синхронизации записи (W) буферного запоминающего блока 5, информационный вход которого соединен с входом 38 приема управления модуля, вход 38.1 адреса приема управления модуля подключен к третьему информационному входу коммутатора 11 адреса, выход генератора 6 констант соединен с первым входом схемы 8 сравнения, второй вход которой подключен к входу 38.2 номера приемника управления модуля, а выход соединен со вторым (инверсным) входом элемента И 23 и с третьим управляющим входом коммутатора 11 адреса, выход 2.9 метки передачи управления регистра 2 микрокоманд подключен к третьему входу элемента ИЛИ 26, к первому входу элемента И 24 и к первому управляющему входу выходного коммутатора 14, выход 2.10 метки конца операции регистра 2 микрокоманд подключен к третьему входу элемента И 21, к выходу 43 конца операции модуля, к четвертому и пятому управляющим входам коммутатора 11 адреса, к четвертому входу элемента ИЛИ 26 и ко второму входу элемента ИЛИ 28, выход которого соединен с шестым управляющим входом коммутатора 11 адреса, первый выход генератора 13 тактовых импульсов подключен ко второму входу элемента И 24 и к входу установки триггера 15, инверсный выход которого соединен с третьим управляющим входом выходного коммутатора 14, выход которого соединен с выходом 40 передачи управления модуля, второй выход генератора 13 тактовых импульсов подключен к входу сброса триггера 15 и к первому входу элемента И 25, выход которого соединен с входом элемента 32 задержки, выход которого подключен к входам синхронизации сдвига (S) и разрешения сдвига (SE) буферного запоминающего блока 5, выход которого соединен со вторым информационным входом выходного коммутатора 14 и с входами элемента ИЛИ 29, выход которого подключен к четвертому управляющему входу выходного коммутатора 14 и ко второму входу элемента И 25, выход которого соединен с первым входом элемента ИЛИ 30, выход которого соединен с выходом 40 передачи управления модуля, выход элемента И 24 подключен ко второму входу элемента ИЛИ 30 и к входу элемента 34 задержки, выход которого соединен со вторым входом элемента ИЛИ 27, а также дополнительно введенные второй генератор 7 констант, дешифратор 9 номера вершины синхронизации, первую группу элементов И 16.1-16. n, вторую группу элементов И 18.1-18.n, третью группу элементов И 20.1-20.n, первую группу элементов ИЛИ 17.1-17.n, вторую группу элементов ИЛИ 19.1-19.n, причем второй управляющий вход выходного коммутатора 14 соединен с прямым выходом триггера 15, выход схемы 8 сравнения подключен к третьему входу элемента ИЛИ 27, выход которого соединен с входом синхронизации триггера 10 запуска, информационный вход которого подключен к шине логической единицы, выход 2.5 метки управления синхронизацией регистра 2 микрокоманд соединен с первыми входами элементов И 16.1-16.n, выходы генератора 7 констант с первого по n-й подключены к первым входам элементов ИЛИ 17.1-17.n соответственно, выход 2.6 номера вершины синхронизации регистра 2 микрокоманд подключен к входу дешифратора 9 номера вершины синхронизации, выходы с первого по n-й которого соединены со вторыми входами элементов И 16.1-16.n соответственно и со вторыми входами элементов ИЛИ 17.1-17.n соответственно, выходы элементов И 16.1-16.n подключены к первым входам элементов ИЛИ 19.1-19.n соответственно и к первым входам элементов И 18.1-18.n соответственно, выходы которых соединены с группой входов элемента ИЛИ 27, входы 41.1-41.n управления синхронизацией модуля подключены ко вторым входам элементов И 18.1-18. n соответственно и ко вторым входам элементов ИЛИ 19.1-19.n соответственно, выходы элементов ИЛИ 17.1-17.n соединены с первыми входами элементов И 20.1-20.n соответственно, вторые входы которых подключены к выходам элементов ИЛИ 19.1-19.n соответственно, а выходы соединены с выходами 42.1-42.n управления синхронизацией модуля соответственно.

Буферный запоминающий блок 5 (фиг.2) предназначен для приема, временного хранения и выдачи управляющих микрокоманд (сообщений) М в порядке их поступления и содержит группу регистров 44.1-44.L (где L - максимальная длина очереди сообщений в блоке), группу коммутаторов 45.1-45.L-1, дешифратор 46, группу элементов И 47.1-47.L, группу элементов ИЛИ 48.1-48.L, элемент ИЛИ 49, триггер 50 и элемент 51 задержки, причем вход синхронизации сдвига блока подключен к входу элемента 51 задержки, выход которого соединен с входом сброса (R) триггера 50, вход синхронизации сдвига блока подключен к первому входу элемента ИЛИ 49, второй вход которого подключен к входу синхронизации записи блока, выход элемента ИЛИ 49 подключен к входам синхронизации регистров 44.1-44. L, инверсные выходы которых подключены к входам элементов И 47.1-47. L соответственно, выходы которых соединены с входом дешифратора 46, выходы с первого по L-й которого подключены к первым входам элементов ИЛИ 48.1-48. L соответственно, выходы которых подключены к V-входам регистров 44.1-44. L соответственно, прямые выходы регистров 44.2-44.L соединены с первыми информационными входами коммутаторов 45.1 - 45.L-1 соответственно, а прямой выход регистра 44.1 является выходом блока, вход разрешения сдвига которого соединен с входом установки (S) триггера 50, прямой выход которого подключен к первым управляющим входам коммутаторов 45.1 - 45.L-1 и к вторым входам элементов ИЛИ 48.1-48. L, инверсный выход триггера 50 соединен с вторыми управляющими входами коммутаторов 45.1 - 45.L-1, вторые информационные входы которых и информационный вход регистра 44.L соединены с информационным входом блока, выходы коммутаторов 45.1 - 45.L-1 соединены с информационными входами регистров 44.1 - 44.L-1 соответственно.

Назначение элементов и блоков модуля мультимикроконтроллерной сети (фиг. 1) состоит в следующем.

Блок 1 памяти микропрограмм предназначен для постоянного хранения и выдачи микрокоманд, входящих в различные участки микропрограмм, закрепленные за текущим модулем.

Регистр 2 микрокоманд служит для приема и фиксации микрокоманд, считываемых из блока 1 памяти микропрограмм, на время их обработки, а регистр 3 адреса - для фиксации адреса следующей микрокоманды выполняемого участка микропрограммы, кода очередной операции или адреса приема управления.

Мультиплексор 4 логических условий предназначен для опроса значений ЛУ, образующихся на входе 37 логических условий модуля, и изменения значения модифицируемого разряда адреса следующей микрокоманды (выход 2.2 регистра 2) в точках ветвления микропрограмм.

Первый генератор 6 констант предназначен для формирования кода логического номера модуля.

Второй генератор 7 констант введен для формирования значений компонент вектора Si, соответствующего текущему модулю mi.

Схема 8 сравнения служит для сравнения кода логического номера текущего модуля с кодами приемников управляющих микрокоманд (сообщений) М и формирования сигнала приема управления, определяющего либо прием сообщения М текущим модулем, либо транзитную передачу сообщения М на выход 40 передачи управления модуля.

Дешифратор 9 номера вершины синхронизации предназначен для формирования сигналов g1 i, g2 i,..., gn i - признаков состояния параллельных участков, завершающихся вершинами синхронизации a1, а2,..., an соответственно.

Триггер 10 запуска предназначен для управления работой генератора 12 тактовых импульсов.

Коммутатор 11 адреса предназначен для передачи адреса следующей микрокоманды на информационный вход регистра 3 адреса с одного из трех возможных направлений: с выхода 2.3 регистра 2 микрокоманд и выхода мультиплексора 4 логических условий, с входа 36 кода операции модуля или с входа 38 приема управления модуля.

Генератор 12 тактовых импульсов служит для формирования двух сдвинутых друг относительно друга импульсных последовательностей τ1 и τ2, синхронизирующих процесс считывания микрокоманд.

Генератор 13 тактовых импульсов служит для формирования двух сдвинутых друг относительно друга импульсных последовательностей t1 и t2, синхронизирующих процессы выдачи и приема управляющих микрокоманд (сообщений) М. Генератор 13 не имеет управляющих входов и начинает вырабатывать последовательности t1 и t2 непосредственно после включения питания модуля.

Для обеспечения устойчивой работы модуля и исключения повторной выдачи управляющих микрокоманд М частоты F1 и F2 следования тактовых импульсов, вырабатываемых соответственно генератором 12 и генератором 13, должны удовлетворять соотношению F1 > F2.

Выходной коммутатор 14 обеспечивает передачу управляющих микрокоманд М, формируемых текущим модулем, и микрокоманд М, поступающих с входа 38 приема управления модуля и фиксируемых в буферном запоминающем блоке 5, на выход 40 передачи управления модуля.

Триггер 15 используется для управления коммутатором 14 (обеспечивает попеременную активизацию первого и второго информационного входа коммутатора 14).

Элементы И 16.1, 16.2,..., 16.n служат для формирования единичных сигналов-признаков d1 i, d2 i,..., dn i опроса состояния групп параллельных участков, завершающихся вершинами синхронизации a1, а2,..., an соответственно. Сигнал-признак dq i (q∈{1,2,...,n}) образуется при завершении i-м модулем одного из параллельных участков, сходящихся в вершине аq, и переходе модуля в режим управления синхронизацией.

Элементы ИЛИ 17.1, 17.2,..., 17.n предназначены для объединения сигналов-признаков состояния параллельных участков g1 i, g2 i,..., gn i с соответствующих выходов дешифратора 9 с сигналами с выходов генератора 7, соответствующими компонентам s1 i, s2 i,..., sn i вектора Si (сопоставленного i-му модулю). Сигнал на выходе элемента ИЛИ 17.q (q∈{1,2,...,n}) определяет состояние i-го модуля (и реализуемого им участка микропрограммы) по отношению к вершине синхронизации аq.

Элементы И 18.1, 18.2, . .., 18.n введены для формирования сигналов-признаков e1 i, e2 i,..., en i окончания групп параллельных участков. Единичный сигнал eq i = 1 (q∈{1,2,...,n}) устанавливается на выходе элемента И 18.q только тогда, когда i-й модуль является ведущим по отношению к q-й вершине синхронизации (единичный сигнал-признак dq i на выходе элемента И 16.q) и все параллельные участки, сходящиеся в q-й вершине синхронизации, завершены (единичный сигнал-признак dq i на входе 41.q i-го модуля).

Элементы ИЛИ 19.1, 19.2,..., 19.n служат для объединения сигналов с выходов элементов И 16.1, 16.2,..., 16.n с сигналами, поступающими с входов 41.1, 41.2,..., 41.n модуля.

Элементы И 20.1, 20.2,..., 20.n предназначены для блокировки распространения сигналов-признаков d1 i, d2 i, ..., dn i с выходов элементов ИЛИ 19.1, 19.2, ..., 19.n на выходы 42.1, 42.2,..., 42.n модуля. Единичный сигнал-признак dq i (q∈{1,2,...,n}) передается через элемент 20.q на выход 42.q i-го модуля только тогда, когда параллельный участок, реализуемый модулем, завершен (т. е. (s

Элемент И 21 используется для запрещения прохождения импульса пуска ММКС от УУВУ до момента окончания всех участков микропрограммы.

Элемент И 22 обеспечивает блокировку передачи импульса с выхода одновибратора 31 на вход сброса триггера 10 запуска.

Элемент И 23 служит для запрещения передачи импульса, синхронизирующего прием сообщения М в блок 5, на вход синхронизации записи (W) блока 5.

Элементы И 24,25 предназначены для попеременного запрещения/разрешения выдачи импульсов, обеспечивающих синхронизацию приема сообщений М, поступающих с выхода 2.8 регистра 2 и с выхода блока 5 соответственно, на выход 40 модуля. Дополнительно, элемент 24 используется для формирования импульса активизации текущего модуля после выдачи сообщения М, а элемент 25 - для формирования импульса сдвига очереди сообщений в блоке 5.

Элемент ИЛИ 26 служит для объединения сигналов с выходов 2.5, 2.7, 2.9 и 2.10 регистра 2 и управления блокировкой элемента И 22.

Элемент ИЛИ 27 предназначен для объединения импульсов и сигналов активизации текущего модуля, поступающих с выхода элемента И 21 (импульс пуска от УУВУ), с выходов элементов И 18.1-18.n (сигналы окончания групп параллельных участков e1 i, e2 i,..., en i), с выхода схемы 8 сравнения (сигнал приема управления) и с выхода элемента 34 задержки (сигнал активизации после выдачи сообщения М).

Элемент ИЛИ 28 служит для объединения сигналов с выходов 2.7 и 2.10 регистра 2.

Элемент ИЛИ 29 используется для формирования сигнала, характеризующего состояние блока 5.

Элемент ИЛИ 30 обеспечивает передачу импульсов с выходов элементов И 24 и 25 на выход 40 модуля для синхронизации приема сообщений М следующим модулем ММКС.

Одновибратор 31 используется для формирования импульса τ3 сброса триггера 10 запуска.

Элемент 32 задержки служит для задержки передачи импульса сдвига с выхода элемента И 25 на входы разрешения сдвига (SE) и синхронизации сдвига (S) блока 5 на время выдачи очередного сообщения М из данного блока следующему модулю ММКС.

Элемент 33 задержки предназначен для сдвига импульса синхронизации приема сообщения М в блок 5 на время, достаточное для установления этого сообщения на информационном входе блока 5.

Элемент 34 задержки использован для задержки поступления импульса активизации модуля (после выдачи сообщения М) на вход синхронизации триггера 10 на время присутствия единичного сигнала на его входе сброса.

Вход 35 пуска модуля служит для приема импульса пуска ММКС от УУВУ.

Вход 36 кода операции модуля служит для приема КОП от УУВУ (КОП представляет собой адрес первой микрокоманды реализуемой микропрограммы в блоке 1).

Вход 37 логических условий модуля предназначен для приема сигналов ЛУ, поступающих от ОУ.

Вход 38 приема управления модуля используется для приема сообщений М от предшествующего модуля ММКС, а выход 40 передачи управления модуля - для выдачи сообщений М следующему модулю ММКС. Выход 40 i-го модуля, i=0, 1, 2,... , N-2, соединяется с входом 38 (i+1)-гo модуля, а выход 40 (N-1)-гo модуля - с входом 38 модуля m0 (фиг.4).

Выход 39 микроопераций модуля предназначен для выдачи сигналов микроопераций (МО) на вход ОУ.

Входы 41.1, 41.2,..., 41.n модуля введены для приема сигналов-признаков d1 i, d2 i, . .., dn i соответственно от предшествующего модуля ММКС, а выходы 42.1, 42.2,.., 42.n - для выдачи указанных признаков следующему модулю. Выходы 42.1, 42.2,..., 42.n i-го модуля, i=0, 1, 2,.., N-2, соединяются с входами 41.1, 41.2, . . ., 41.n (i+1)-гo модуля ММКС соответственно, а выходы 42.1, 42.2,..., 42.n (N-1)-гo модуля - с входами 41.1, 41.2,..., 41.n модуля m0 соответственно (фиг. 4).

Выход 43 конца операции модуля служит для выдачи УУВУ признака завершения микропрограммы - метки конца операции с выхода 2.10 регистра 2.

Рассмотрим процесс функционирования предлагаемого модуля. Учитывая, что модуль предназначен для работы в составе ММКС (фиг.4), его функционирование будем рассматривать во взаимосвязи с другими аналогичными модулями.

Первоначально все элементы памяти модуля (фиг. 1), включая регистры 44.1-44. L и триггер 50 буферного запоминающего блока 5 (фиг.2), установлены в состояние логического нуля. Исключение составляет только разряд (поле) 2.10 метки конца операции (Мко) регистра 2 - данный разряд находится в состоянии логической единицы. Исходя из этого на выходе элемента ИЛИ 29 находится нулевой сигнал, индицирующий отсутствие сообщений М в блоке 5, генератор 12 тактовых импульсов выключен, элемент И 21 открыт, а коммутатор 11 адреса настроен на прием кода операции с входа 36 модуля. На выходе генератора 6 констант присутствует код логического номера (i) текущего модуля, а на выходах генератора 7 констант находятся значения компонент вектора Si, определяющего соответствие между вершинами синхронизации параллельных участков микропрограмм и текущим модулем (mi). (Цепи приведения элементов модуля на фиг.1 и 2 с целью упрощения условно не показаны.)

Функционирование модуля (и ММКС в целом) начинается с момента подачи на вход 36 модуля кода выполняемой операции. (КОП формируется УУВУ и передается модулю ММКС, за которым закреплена первая микрокоманда соответствующей микропрограммы. ) Код операции через открытый коммутатор 11 адреса проходит на информационный вход регистра 3 адреса. Одновременно на вход 35 модуля подается импульс пуска. Этот импульс проходит через открытый элемент И 21 и элемент ИЛИ 27 и воздействует на вход синхронизации триггера 10 запуска. Поскольку на информационном входе триггера 10 находится единичный сигнал, передний фронт импульса пуска вызывает переход данного триггера в единичное состояние. Единичный сигнал с прямого выхода триггера 10 поступает на вход генератора 12, включает его и тем самым разрешает формирование на его выходах импульсных последовательностей τ1 и τ2.

Импульс τ1 с первого выхода генератора 12 подается на вход синхронизации регистра 3 и передним фронтом фиксирует в нем КОП. КОП с выхода регистра 3 поступает на адресный вход блока 1 и тем самым формирует на его выходе первую микрокоманду выполняемой микропрограммы. Импульс τ2 со второго выхода генератора 12 подается на вход синхронизации регистра 2 и передним фронтом записывает в него считанную микрокоманду. Одновременно импульс τ2 поступает на вход одновибратора 31 и задним фронтом возбуждает на его выходе импульс τ3, по форме и длительности аналогичный τ2.

Дальнейший ход работы модуля определяется форматом считанной микрокоманды.

Случай 1. Считанная микрокоманда имеет формат Ф1 (фиг. 3). В этом случае на выходе 2.1 регистра 2 образуется код опрашиваемого ЛУ, на выходе 2.4 формируется код МО, на выходах 2.2 и 2.3 появляются соответственно модифицируемый разряд (Ам) и немодифицируемая часть (Aн) адреса следующей микрокоманды. На остальных выходах регистра 2 устанавливаются нулевые сигналы.

Код МО передается на выход 39 модуля и далее поступает на вход объекта управления. Нулевые сигналы с выходов 2.5, 2.7, 2.9 и 2.10 регистра 2 формируют нулевой сигнал на выходе элемента ИЛИ 26. Этот сигнал закрывает элемент И 22 и тем самым запрещает прохождение импульса τ3 с выхода одновибратора 31 на вход сброса триггера 10 запуска. Нулевой сигнал с выхода 2.5 регистра 2 блокирует элементы И 16.1-16.n, а нулевой код с выхода 2.6 формирует на выходах дешифратора 9 нулевые сигналы. Нулевой сигнал с выхода 2.9 закрывает элемент И 24. Нулевые сигналы с выходов 2.7 и 2.10 регистра 2 поступают на первый и четвертый управляющие входы коммутатора 11 и коммутируют его выход с первым информационным входом.

Одновременно с описанными выше действиями происходит формирование адреса следующей микрокоманды. В этом процессе участвуют выходы (поля) 2.1-2.3 регистра 2, а также мультиплексор 4 логических условий, который обеспечивает модификацию адреса следующей микрокоманды в точках ветвления микропрограмм.

Код ЛУ с выхода 2.1 и модифицируемый разряд адреса с выхода 2.2 регистра 2 поступают соответственно на адресный и первый информационный входы мультиплексора 4. Если код ЛУ не является нулевым, то на выход мультиплексора 4 передается сигнал с соответствующего разряда входа 37 логических условий модуля, в противном случае на выход мультиплексора 4 поступает исходное значение модифицируемого разряда адреса с выхода 2.2 регистра 2. Таким образом, на выходе мультиплексора 4 образуется измененное значение модифицируемого разряда адреса, которое в объединении с немодифицируемой (старшей) частью адреса с выхода 2.3 регистра 2 определяет адрес следующей микрокоманды.

Сформированный адрес поступает на первый информационный вход коммутатора 11 адреса. Так как на первом и четвертом управляющих входах коммутатора 11 присутствуют нулевые сигналы, адрес передается на информационный вход регистра 3. В момент появления на входе синхронизации регистра 3 переднего фронта очередного тактового импульса τ1 адрес следующей микрокоманды заносится в регистр 3. Далее этот адрес адресует блок 1 памяти микропрограмм и обеспечивает считывание очередной микрокоманды. Текущий модуль приступает к выполнению считанной микрокоманды. Дальнейшее функционирование модуля происходит аналогично рассмотренному.

Случай 2. Считанная микрокоманда имеет формат Ф2 (фиг. 3). В этом случае текущий модуль переходит в режим передачи управления другому аналогичному модулю ММКС или запуска группы параллельных участков микропрограмм, закрепленных за другими модулями. На выходе 2.9 регистра 2 (фиг. 1) появляется единичная метка передачи управления (Мпу), на выходе 2.8 формируется управляющая микрокоманда - сообщение М, реализующее межмодульную передачу управления. (Сообщение М содержит два поля (фиг. 3): в первом из них указывается номер модуля, которому необходимо передать управление; во втором поле фиксируется адрес передачи управления (Апу). На выходе 2.4 регистра 2 устанавливается нулевой код (передача МО на ОУ отсутствует). Состояние остальных выходов регистра 2 аналогично их состоянию в случае 1: на выходах 2.1-2.3 образуется информация, используемая для формирования адреса следующей микрокоманды, на выходах 2.5-2.7 и 2.10 формируются сигналы логического нуля.

Нулевой сигнал с выхода 2.5 регистра 2 блокирует элементы И 16.1-16.n, нулевой код с выхода 2.6 формирует нулевые сигналы на выходах дешифратора 9, а нулевые сигналы с выходов 2.7 и 2.10 настраивают коммутатор 11 на прием информации (адреса следующей микрокоманды) с его первого информационного входа.

Единичная метка Mпу через элемент ИЛИ 26 проходит на первый вход элемента И 22 и обеспечивает передачу импульса τ3 с выхода одновибратора 31 на вход сброса триггера 10. Триггер 10 переключается в состояние логического нуля. Нулевой сигнал с прямого выхода триггера 10 подается на вход генератора 12 и запрещает формирование импульсов τ1 и τ2 на его выходах. Процесс выполнения участка микропрограммы текущим (i-м) модулем временно приостанавливается.

Одновременно метка Мпу поступает на первый вход элемента И 24, а также на первый управляющий вход коммутатора 14, а сообщение М с выхода 2.8 регистра 2 поступает на первый информационный вход коммутатора 14. Очередной импульс t1 с первого выхода генератора 13 поступает на вход установки триггера 15 и устанавливает его в единичное состояние. Единичный сигнал с прямого выхода указанного триггера подается на второй управляющий вход коммутатора 14 и обеспечивает передачу сообщения М на его выход (передача информации со второго информационного входа коммутатора 14 на его выход запрещается нулевым сигналом с инверсного выхода триггера 15). Далее сообщение М поступает на выход 40 текущего модуля и передается на вход 38 следующего ((i+1)-го) модуля ММКС (фиг.4).

В то же время импульс t1 с первого выхода генератора 13 (фиг. 1) через открытый элемент И 24 и элемент ИЛИ 30 проходит на выход 40 текущего модуля и обеспечивает синхронизацию приема сообщения М следующим модулем. Кроме того, импульс t1 с выхода элемента И 24 через элемент 34 задержки и элемент ИЛИ 27 подается на вход синхронизации триггера 10. По переднему фронту этого импульса триггер 10 возвращается в единичное состояние. На выходах генератора 12 снова начинается формирование импульсных последовательностей τ1 и τ2. Текущий модуль возобновляет функционирование.

(Необходимость приостановки процесса функционирования модуля на время выдачи сообщений М вызвана возможностью смены информации на выходе 2.8 регистра 2 до появления очередного импульса t1, поскольку F1 > F2.)

Одновременно с процессом выдачи сообщения М на выход 40 модуля происходит формирование адреса следующей микрокоманды. Этот процесс осуществляется так же, как и в случае 1 (см. выше). Адрес следующей микрокоманды, получаемый объединением информации с выхода 2.3 регистра 2 и выхода мультиплексора 4, через коммутатор 11 проходит на информационный вход регистра 3. По переднему фронту очередного импульса τ1 с первого выхода генератора 12 этот адрес заносится в регистр 3. Далее адрес с выхода регистра 3 поступает на адресный вход блока 1 и обеспечивает считывание следующей микрокоманды. Процесс обработки следующей микрокоманды определяется ее форматом (фиг.3) и протекает аналогично рассмотренному.

Если текущий модуль функционирует в режиме передачи управления, то очередная микрокоманда будет иметь формат Ф3 с нулевым кодом в поле 2.6 (окончание последовательного участка микропрограммы). После ее выполнения модуль перейдет в пассивное состояние. Если же модуль осуществляет активизацию группы параллельных участков, то очередная микрокоманда снова будет иметь формат Ф2. Модуль вновь выдаст сообщение М другому аналогичному модулю ММКС (за которым закреплен следующий активизируемый параллельный участок). Далее текущий модуль выработает очередное сообщение М и т.д. до тех пор, пока не будут активизированы все параллельные участки. После выдачи последнего сообщения М модуль может продолжить выполнение микропрограммы или, аналогично режиму передачи управления, перейти в пассивное состояние. В последнем из названных случаев очередной считанной микрокомандой будет Ф3 с нулевым кодом в поле 2.6 (процесс обработки микрокоманд формата Ф3 детально будет рассмотрен ниже).

Рассмотрим процесс передачи сообщений М и работу модуля в режиме их приема и анализа. Сообщение М, выработанное модулем mi, последовательно транслируется по кольцу ММКС и в конце концов поступает на вход 38 приема управления некоторого модуля mj, j ≠ i. Номер модуля - приемника управления с входа 38.2 модуля подается на второй вход схемы 8 сравнения и сравнивается с номером (j) текущего модуля mj, формируемым на выходе генератора 6 констант. Адрес передачи управления Апу с входа 38.1 модуля передается на третий информационный вход коммутатора 11. Одновременно сообщение М подается на информационный вход буферного запоминающего блока 5.

При совпадении номера приемника управления с номером текущего модуля mj на выходе схемы 8 сравнения устанавливается единичный сигнал приема управления. Единичный сигнал с выхода схемы 8 передается на третий управляющий вход коммутатора 11. Так как хотя бы на одном из входов элемента ИЛИ 28 имеется единичный сигнал (рассматриваемый модуль завершил выполнение какого-либо участка или микропрограммы в целом), то на шестом управляющем входе коммутатора 11 также присутствует единичный сигнал и Апу через коммутатор 11 поступает на информационный вход регистра 3 адреса.

В то же время импульс синхронизации, сопровождающий сообщение М, с линии 38.3 модуля подается на вход элемента 33 задержки, спустя заданное время появляется на его выходе и поступает на первый вход элемента И 23. Так как элемент И 23 заблокирован единичным сигналом приема управления с выхода схемы 8, импульс синхронизации не проходит на его выход, а следовательно, и на вход синхронизации записи W буферного запоминающего блока 5. Таким образом, запись поступившего сообщения М в блок 5 с целью дальнейшей передачи не производится.

Одновременно положительный перепад уровня сигнала (0 ---> 1), возникающий на выходе схемы 8, через элемент ИЛИ 27 передается на вход синхронизации триггера 10 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 10 запускает генератор 12. Таким образом, модуль mj осуществляет прием управления от модуля mi (источника сообщения М).

Первый импульс τ1 с первого выхода генератора 12 подается на вход синхронизации регистра 3 и обеспечивает фиксацию поступившего на его информационный вход адреса Апу. Модуль mj начинает выполнение микропрограммы с адреса Апу. В дальнейшем работа j-го модуля ничем не отличается от функционирования модуля mi при выполнении начального последовательного участка микропрограммы (см. выше).

Если совпадения номера приемника управления и номера j-го модуля не происходит, то на выходе схемы 8 сравнения сохраняется нулевой уровень сигнала. Импульс с линии 38.3 модуля через элемент 33 задержки и открытый элемент И 23 проходит на вход синхронизации записи W буферного запоминающего блока 5 и обеспечивает запись поступившего сообщения М в блок 5 для передачи следующему модулю сети; состояние j-го модуля остается неизменным.

Запись сообщений М в буферный запоминающий блок 5 происходит следующим образом.

Очередное сообщение с информационного входа буферного запоминающего блока 5 (фиг. 2) передается на информационный вход регистра 44.L и на вторые информационные входы коммутаторов 45.1 - 45.L-1. Так как триггер 50 находится в состоянии логического нуля, единичный сигнал с его инверсного выхода поступает на вторые управляющие входы коммутаторов 45.1 - 45.L-1 и обеспечивает передачу сообщения на информационные входы регистров 44.1 - 44.L-1. В то же время нулевой сигнал с прямого выхода триггера 50 блокирует поступление на выходы коммутаторов 45.1 - 45.L-1 информации с их первых информационных входов.

Сигналы с инверсных выходов регистров 44.1-44. L поступают на входы элементов И 47.1-47.L соответственно и формируют на их выходах код, характеризующий текущее состояние очереди сообщений в блоке. Пусть в регистрах 44.1-44. k (k < L) зафиксированы ранее поступившие сообщения, а остальные регистры находятся в состоянии логического нуля. Так как на инверсных выходах каждого из регистров 44.1-44.k присутствует по крайней мере один нулевой сигнал, а на инверсных выходах регистров 44.k+1 - 44.L установлены единичные сигналы, то на выходах элементов И 47.1-47.L образуется код  . Этот код поступает на вход дешифратора 46 и возбуждает единичный сигнал на его (k+1)-м выходе. Указанный сигнал через элемент ИЛИ 48. k+1 передается на V-вход регистра 44.k+1, разрешая тем самым прием информации в данный регистр.

. Этот код поступает на вход дешифратора 46 и возбуждает единичный сигнал на его (k+1)-м выходе. Указанный сигнал через элемент ИЛИ 48. k+1 передается на V-вход регистра 44.k+1, разрешая тем самым прием информации в данный регистр.

Импульс с входа синхронизации записи блока через элемент ИЛИ 49 поступает на входы синхронизации регистров 44.1-44.L и задним фронтом фиксирует очередное сообщение в регистре 44.k+1. Так как на V-входах остальных регистров 44.1-44.k, 44.k+2 - 44.L сохраняется запрещающий (нулевой) уровень сигнала, их состояние остается неизменным. После фиксации сообщения в регистре 44. k+1 на выходе элемента И 47.k+1 появляется нулевой сигнал, который в объединении с сигналами с выходов элементов И 47.1-47.k, 47.k+2 - 47.L поступает на вход дешифратора 46 и возбуждает единичный сигнал на его следующем, т. е. (k+2)-м выходе. Аналогичным образом очередное сообщение будет записано в регистр 44.k+2 и т.д.

Считывание сообщений из буферного запоминающего блока 5 производится в порядке их поступления. Сообщение М, размещенное в регистре 44.1, появляется на выходе блока и передается на входы элемента ИЛИ 29 (фиг. 1) и на второй информационный вход коммутатора 14. Единичный сигнал, образующийся на выходе элемента ИЛИ 29, подается на четвертый управляющий вход коммутатора 14 и открывает элемент И 25. Очередной импульс t2 со второго выхода генератора 13 переключает триггер 15 в нулевое состояние. Единичный сигнал с инверсного выхода триггера 15 поступает на третий управляющий вход коммутатора 14 и обеспечивает передачу сообщения М с выхода блока 5 на выход 40 модуля с целью выдачи следующему ((j+1)-му) модулю ММКС. Одновременно импульс t2 проходит через открытый элемент И 25, элемент ИЛИ 30 и синхронизирует прием выдаваемого сообщения.

Этот же импульс 12 обеспечивает сдвиг очереди сообщений в блоке 5.

Импульс t2 с выхода элемента И 25 поступает на вход элемента 32 задержки и со сдвигом во времени подается на входы разрешения сдвига (SE) и синхронизации сдвига (S) блока 5. Импульс с входа разрешения сдвига блока 5 (фиг. 2) поступает на вход установки триггера 50 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 50 подается на первые управляющие входы коммутаторов 45.1 - 45.L-1 и обеспечивает передачу информации с прямых выходов регистров 44.2-44.L на информационные входы регистров 44.1 - 44. L-1 соответственно. Этот же сигнал через элементы ИЛИ 48.1-48.L проходит на V-входы регистров 44.1-44.L и разрешает запись информации во все указанные регистры. В то же время импульс t2 с входа синхронизации сдвига блока поступает на вход элемента 51 задержки и, кроме того, через элемент ИЛИ 49 передается на входы синхронизации регистров 44.1-44.L. Так как на V-входах регистров 44.1-44. L находятся разрешающие сигналы, по заднему фронту импульса 12 информация из регистров 44.L-44.2 переписывается в регистры 44.L-1 - 44.1 соответственно, а в регистр 44.L заносится нулевой код. Состояние регистра 44. k+1 становится нулевым, на выходе элемента И 47.k+1 формируется единичный сигнал, а сообщение М, ранее размещавшееся в регистре 44.2, появляется на выходе блока. Импульс с выхода элемента 51 задержки спустя время сдвига очереди поступает на вход сброса триггера 50 и возвращает его в нулевое состояние.

Если после сдвига очереди состояние регистра 44.1 становится нулевым, то на выходе элемента ИЛИ 29 (фиг. 1) устанавливается нулевой сигнал. Этот сигнал блокирует элемент И 25 и предотвращает распространение следующего импульса t2 на выход 40 текущего модуля и на вход элемента 32 задержки. Процесс выдачи сообщений на выход 40 модуля и сдвига очереди сообщений в блоке 5 приостанавливается. С поступлением в блок 5 очередного сообщения М транзитная передача сообщений на выход 40 модуля возобновляется.

Случай 3. Считанная из блока 1 микрокоманда имеет формат Ф3 (фиг. 3). В этом случае текущий модуль mi завершает исполнение параллельного или последовательного участка микропрограммы и переходит в состояние ожидания. На выходах 2.1-2.5, 2.8-2.10 регистра 2 формируются сигналы логического нуля, на выходе 2.7 образуется единичный сигнал-метка конца участка (Мку). Если завершенный участок является последовательным, то на выходе 2.6 регистра 2 появляется нулевой код. Если завершенный участок параллельный, то на выходе 2.6 устанавливается ненулевой код номера вершины синхронизации (НВС) аq, в которой сходится выполненный участок. (Завершенный участок принадлежит группе параллельных участков Λq, сходящихся в вершине синхронизации аq.)

Нулевой сигнал с выхода 2.5 регистра 2 блокирует элементы И 16.1-16.n. Единичный сигнал - метка Мку - с выхода 2.7 регистра 2 через элемент ИЛИ 26 проходит на первый вход элемента И 22 и обеспечивает поступление импульса τ3 с выхода одновибратора 31 на вход сброса триггера 10 запуска. Триггер 10 переключается в нулевое состояние и нулевой сигнал с его прямого выхода выключает генератор 12. Считывание микрокоманд из блока 1 прекращается. Одновременно метка Мку блокирует элемент И 21, а также поступает на первый, второй и - через элемент 28 - на шестой управляющие входы коммутатора 11. В результате передача информации с первого и второго информационных входов коммутатора 11 на его выход запрещается и последний настраивается на последующий прием управления от другого модуля по единичному сигналу с выхода схемы 8 сравнения.

Если выполненный i-м модулем участок является последовательным, то нулевой код с выхода 2.6 регистра 2 формирует нулевые сигналы на всех выходах дешифратора 9. Таким образом, i-й модуль не оказывает никакого влияния на процесс распространения сигналов через элементы И 20.1-20.n. Если же выполненный участок параллельный, то код НВС aq с выхода 2.6 регистра 2 формирует единичный сигнал-признак (gq i) состояния параллельного участка на q-м выходе дешифратора 9. Этот сигнал поступает на второй вход элемента ИЛИ 17.q и формирует единичный сигнал на его выходе. (На первом входе элемента ИЛИ 17. q присутствует нулевой сигнал sq i=0 с q-го выхода генератора 7 констант. Значение sq i = 0 определяет, что i-й модуль реализует некоторый параллельный участок Lv q, завершающийся в q-й вершине синхронизации.) Единичный сигнал с выхода элемента 17. q открывает элемент И 20.q. Таким образом, i-й модуль индицирует окончание закрепленного за ним параллельного участка Lv q. В результате обеспечивается возможность передачи на выход 42.q модуля сигнала-признака dq k опроса состояния параллельных участков, вырабатываемого модулем mk (который выполняет функции ведущего по отношению к вершине синхронизации aq).

Учитывая, что на выходах 2.1-2.5, 2.8-2.10 регистра 2 находятся нулевые сигналы, других действий модуль в рассматриваемом режиме не производит.

Случай 4. Считанная микрокоманда имеет формат Ф4 (фиг. 3). В данном случае текущий модуль mi завершает выполнение закрепленного за ним участка Lv q и переходит в режим управления синхронизацией группы параллельных участков Λq= {L

На выходе 2.5 регистра 2 (фиг. 1) появляется единичный сигнал-метка управления синхронизацией (Мус), на выходе 2.6 формируется код номера вершины синхронизации aq. На выходе 2.1 регистра 2 образуется код опрашиваемого ЛУ, на выходах 2.2 и 2.3 устанавливаются соответственно модифицируемый разряд (Ам) и немодифицируемая часть (Ан) адреса следующей микрокоманды, на выходах 2.4, 2.7-2.10 формируются сигналы логического нуля.

Единичный сигнал (метка Mус) с выхода 2.5 регистра 2 через элемент ИЛИ 26 проходит на первый вход элемента И 22 и обеспечивает поступление импульса τ3 с выхода одновибратора 31 на вход сброса триггера 10 запуска. Триггер 10 переходит в нулевое состояние. Нулевой сигнал с его прямого выхода выключает генератор 12, запрещая тем самым формирование импульсных последовательностей τ1 и τ2, синхронизирующих процесс считывания микрокоманд.

Одновременно с описанными действиями происходит формирование адреса следующей микрокоманды. (По этому адресу будет осуществлен переход после окончания группы параллельных участков Λq .) Процесс формирования указанного адреса протекает так же, как и в случае 1 с использованием полей 2.1-2.3 обрабатываемой микрокоманды (см. выше). Полученный адрес поступает на первый информационный вход коммутатора 11 и, учитывая, что на первом и четвертом управляющих входах последнего находятся нулевые сигналы с выходов 2.7 и 2.10 регистра 2, проходит на информационный вход регистра 3.

В то же самое время текущий модуль инициирует процесс опроса состояния группы параллельных участков Λq.

Код HBC aq с выхода 2.6 регистра 2 поступает на вход дешифратора 9 и возбуждает сигнал логической единицы (признак gq i состояния реализуемого модулем параллельного участка Lv q) на его q-м выходе. Этот сигнал (признак) подается на второй вход элемента ИЛИ 17.q и формирует на его выходе единичный сигнал (на первом входе элемента 17.q находится нулевой сигнал с q-го выхода генератора 7 констант, определяющий нулевое значение компоненты sq i - ведущий модуль mi всегда реализует один из участков группы Λq).

Одновременно единичный сигнал (метка Мус) с выхода 2.5 регистра 2 поступает на первые входы элементов И 16.1-16.n. На входах элемента 16.q происходит совпадение единиц и на его выходе образуется единичный сигнал-признак dq i опроса состояния параллельных участков Λq. Этот сигнал открывает элемент И 18.q, а также проходит через элемент ИЛИ 19.q на второй вход элемента И 20. q. Поскольку на первый вход элемента 20.q поступает единичный сигнал с выхода элемента ИЛИ 17.q, единичный сигнал dq i передается на его выход и соответственно на выход 42.q текущего модуля. Таким образом, начинается процесс распространения сигнала-признака dq i через цепочку модулей ММКС с целью опроса состояния параллельных участков Λq.

Распространение сигнала dq i происходит в q-м канале управления синхронизацией ММКС, который соответствует q-й вершине синхронизации. q-й канал управления синхронизацией включает последовательность пар элементов 19.q, 20.q различных модулей сети и связей, соединяющих эти элементы. Схема канала управления синхронизацией ММКС показана на фиг.5. (На фиг.5 выделены элементы и связи, образующие q-й канал управления синхронизацией ММКС.) Независимо от сигнала dq i может происходить распространение других аналогичных сигналов {dt j}, t≠q, через другие пары элементов 19.t, 20.t (в других каналах управления синхронизацией). Тем самым обеспечивается возможность физически одновременной синхронизации нескольких групп параллельных участков микропрограмм. Максимальное число таких групп определяется числом n1 вершин (точек) синхронизации параллельных участков в выполняемой микропрограмме. (Это число определяет количество независимых каналов управления синхронизацией в ММКС.)

Процесс распространения сигнала dq i и опроса параллельных участков происходит следующим образом. Единичный сигнал dq i с выхода 42.q i-го модуля поступает на вход 41.q следующего, т.е. (i+1)-го модуля ММКС (фиг. 1, 4, 5). Далее этот сигнал проходит через элемент ИЛИ 19.q (i+1)-го модуля и подается на второй вход элемента И 20.q. Если (i+1)-й модуль не выполняет ни одного участка, завершающегося в q-й вершине синхронизации, то на q-м выходе генератора 7 констант присутствует единичный сигнал (sq i+1 =1). Этот сигнал формирует единичный сигнал на выходе элемента ИЛИ 17.q. Единичный сигнал с выхода элемента 17.q открывает элемент И 20.q и тем самым обеспечивает прохождение сигнала-признака dq i с выхода элемента 19.q на выход 42.q (i+1)-го модуля (фиг. 1, 5), Сигнал dq i передается следующему, т.е. (i+2)-му модулю ММКС. Таким образом, (i+1)-й модуль не влияет на процесс распространения сигнала dq i (безусловно передает его очередному модулю).

Если (i+1)-й модуль реализует некоторый параллельный участок Lf q группы Λq, то на q-м выходе генератора 7 констант находится сигнал логического нуля (sq i+1= 0) и уровень сигнала на выходе элемента ИЛИ 17.q определяется сигналом-признаком gq i+1 состояния параллельного участка Lf q, поступающим с q-го выхода дешифратора 9. Если на q-м выходе дешифратора 9 присутствует нулевой сигнал (параллельный участок Lf q не завершен), то на выходе элемента ИЛИ 17.q также находится нулевой сигнал. Этот сигнал закрывает элемент И 20. q и тем самым запрещает прохождение сигнала dq i с выхода элемента 19.q на выход 42.q (i+1)-го модуля. На выходе элемента 20.q и соответственно на выходе 42.q (i+1)-го модуля сохраняется сигнал логического нуля.

Как только (i+1)-й модуль завершает выполнение участка Lf q, на q-м выходе дешифратора 9 образуется единичный сигнал (gq i+1 = 1). Этот сигнал формирует единичный сигнал на выходе элемента ИЛИ 17.q и тем самым открывает элемент И 20. q. В результате единичный сигнал dq i с выхода элемента 19.q проходит через элемент 20.q и далее с выхода 42.q (i+1)-го модуля передается на вход 41.q следующего, т.е. (i+2)-го модуля ММКС. Аналогичным образом происходит распространение сигнала-признака dq i через (i+2)-й, (i+3)-й и т.д. (N-1)-й, нулевой (m0), первый (m1) и остальные модули сети (фиг.4, 5).

Таким образом, прохождение сигнала-признака dq i через модули {mk}, которые не реализуют участков группы Λq(s

В конце концов сигнал-признак dq i проходит через все модули ММКС и появляется на входе 41.q ведущего модуля mi (фиг. 1, 5). Сигнал dq i поступает на второй вход элемента ИЛИ 19.q и подтверждает единичный уровень сигнала на его выходе - распространение сигнала dq i через модули ММКС прекращается. Одновременно сигнал dq i подается на второй вход элемента И 18.q. Так как на первом входе элемента 18.q все еще присутствует единичный сигнал с выхода элемента И 16.q, на входах элемента 18.q происходит совпадение единиц и на его выходе формируется единичный сигнал-признак eq i окончания параллельных участков группы Λq. Единичный сигнал с выхода элемента 18.q через элемент ИЛИ 27 проходит на вход синхронизации триггера 10 запуска. Триггер 10 переключается в состояние логической единицы и единичный сигнал с его прямого выхода включает генератор 12. На выходах генератора 12 вновь начинается формирование импульсов синхронизации τ1 и τ2.

Импульс τ1 поступает на вход синхронизации регистра 3 и фиксирует в нем адрес следующей микрокоманды, сформированный при переходе ведущего модуля в режим управления синхронизацией параллельных участков (см. выше). Адрес с выхода регистра 3 подается на адресный вход блока 1 и формирует на его выходе очередную микрокоманду. Импульс τ2 со второго выхода генератора 12 подается на вход синхронизации регистра 2 и записывает в него считанную микрокоманду. Одновременно по заднему фронту импульса τ2 на выходе одновибратора 31 образуется импульс τ3.

Дальнейшая работа i-го модуля полностью определяется форматом считанной микрокоманды (фиг. 3) и происходит аналогично рассмотренному.

Считанная микрокоманда может иметь любой из форматов, представленных на фиг. 3, в том числе и формат Ф4. Таким образом, текущий модуль может последовательно управлять синхронизацией нескольких различных групп параллельных участков микропрограмм.

После появления на выходах регистра 2 очередной микрокоманды на q-м выходе дешифратора 9 будет сформирован нулевой сигнал. Соответственно, нулевой сигнал появится и на выходе элемента 16.q. (Если считанная микрокоманда имеет формат Ф4, то одновременно появится единичный сигнал на p-м выходе (p≠q) дешифратора 9 и соответственно на выходе элемента И 16.р.) Нулевой сигнал с выхода элемента 16.q вновь закроет элемент И 18.q; на выходе последнего, а следовательно, и на входе синхронизации триггера 10, установится нулевой уровень сигнала. Нулевой сигнал появится также на выходе элемента ИЛИ 17.q, что приведет к блокировке элемента И 20.q. На выходе 42.q i-го модуля будет восстановлен нулевой сигнал. Этот сигнал, распространяясь по цепочке модулей ММКС (фиг.4, 5), последовательно заблокирует элементы И 20.q всех модулей, а также, возвратившись на вход 41.q i-го модуля, подтвердит нулевой сигнал на выходе элемента И 18.q и сформирует нулевой сигнал на выходе элемента ИЛИ 19. q. Единичные сигналы на q-x выходах дешифраторов 9 (и соответственно на первых входах элементов И 20.q) ведомых модулей сохранятся до последующего запуска этих модулей со стороны других модулей ММКС.

Случай 5. Если считанная микрокоманда имеет формат Ф5 (фиг. 3), то текущий модуль (и ММКС в целом) завершает исполнение микропрограммы. На выходе 2.10 регистра 2 появляется единичный сигнал-метка конца операции (Мко), состояние остальных выходов регистра 2 становится нулевым. Метка Мко с выхода 2.10 регистра 2 через элемент ИЛИ 26 проходит на первый вход элемента И 22. В результате импульс τ3 с выхода одновибратора 31 проходит через элемент И 22 и переводит триггер 10 в нулевое состояние, выключая тем самым генератор 12. В то же время метка Мко поступает на четвертый и пятый, а также - через элемент ИЛИ 28 - на шестой управляющие входы коммутатора 11 и настраивает коммутатор 11 либо на прием очередного кода операции с входа 36 модуля, либо на прием адреса передачи управления с входа 38.1 модуля. Кроме того, метка Мко совместно с нулевым сигналом с выхода 2.7 регистра 2 открывает элемент И 21 для последующего приема импульса пуска от УУВУ. Одновременно метка Мко поступает на выход 43 конца операции модуля и сообщает УУВУ о завершении выполнения текущей микропрограммы. На этом процесс функционирования модуля (и ММКС) завершается.

Оценим преимущества предлагаемого технического решения перед прототипом.

В микроконтроллерной сети, построенной на основе прототипа (далее - в прототипе), синхронизация параллельных участков микропрограмм обеспечивается за счет передачи и модификации специальной микрокоманды Z, содержащей номер точки (вершины) синхронизации и число синхронизируемых участков (количество ожидаемых событий). Время синхронизации, т.е. время между моментом фактического окончания требуемых параллельных участков Λq и моментом получения признака окончания ведущим модулем определяется временем передачи микрокоманды Z в сети и способом межмодульного распределения участков.

Пусть mi - ведущий модуль, а mi - модуль, за которым закреплен параллельный участок L

Рассмотрим случай 1.

Время синхронизации в этом случае определяется временем передачи микрокоманды Z от модуля mj модулю mi

t0(mj, mi) = (r(mj, mi) + 1) • t0,

где r(mj, mi) - число промежуточных (транзитных) модулей между модулем mj и mi; t0 - время обработки (ретрансляции) микрокоманды Z одним транзитным модулем (добавление единицы требуется для учета времени ретрансляции микрокоманды Z модулем mj).

Величина t0 определяется длительностью промежутка между появлением импульса синхронизации, сопровождающего микрокоманду Z, на входе 55 транзитного модуля и формированием аналогичного импульса, синхронизирующего выдачу этой микрокоманды на выход 58 модуля. Время t0 складывается из следующих составляющих: времени t43 задержки элемента 43, времени t47 срабатывания одновибратора 47, задержки t31 элемента И 31, среднего времени t5 пребывания микрокоманды Z в буферном запоминающем блоке 5 и периода Т13 следования импульсов П2, вырабатываемых генератором 13. Исходя из сказанного t0 = t43 + t47 + t31 + t5 + T13.

Поскольку не исключена возможность одновременной синхронизации нескольких групп параллельных участков, в блоке 5 транзитного модуля в среднем находится L* (1 < L* < L) микрокоманд Z (L - максимальная длина очереди микрокоманд Z в блоке 5). Таким образом, t5 = (L*-1) • Т13. Т13 фактически представляет собой время сдвига очереди микрокоманд Z в блоке 5 при выдаче очередной микрокоманды. Исходя из этого, окончательно можно записать t0 = t43 + t47 + t31 + L*T13.

Рассмотрим случай 2.

В этом случае необходим дополнительный цикл опроса (чтобы учесть состояние участка Lf q, завершенного после записи микрокоманды Z в блок 5). Максимальное время синхронизации при этом составит

t0 *(mj, mi) = t0(mj,mj) + t0(mj,mi),

где t0(mj,mj) - время прохождения микрокоманды Z с выхода j-го модуля на его вход.

Таким образом, время синхронизации параллельных участков в прототипе заключено в пределах от t0(mj,mi) (случай 1) до t0 *(mj,mi) (случай 2 - наихудший случай).

В сети, построенной на базе предлагаемого модуля (далее - в предлагаемом модуле), для синхронизации группы параллельных участков Λq необходим единственный цикл опроса. Время синхронизации определяется временем распространения сигнала-признака dq i от модуля mj к ведущему модулю mi. Учитывая, что передача сигналов {dt k} осуществляется независимо через отдельные каналы управления синхронизацией (фиг. 1, 5), это время может быть выражено как

t(mj,mi) = r(mj,mi) • (t19.q + t20.q),

где t19.q, t20.q - задержка элементов 19.q и 20.q соответственно.

Очевидно, что t0 >> t19.q + t20.q (так как L*T13 >> t19.q + t20.q, t19.q ≈ t20.q ≈ t31), поэтому t0(mj,mi) >> t(mj,mi) (t0 *(mj,mi) >> t(mj,mi)). Следовательно, предлагаемый модуль обеспечивает существенное снижение времени синхронизации параллельных участков, а значит, и повышение ее оперативности. Это позволяет расширить класс микропрограмм (алгоритмов управления), реализуемых ММКС, за счет включения микропрограмм, критичных к оперативности синхронизации параллельных участков, и, следовательно, расширить область применения модуля.

Одновременно с увеличением оперативности синхронизации предлагаемое техническое решение позволяет упростить модуль ММКС за счет существенного упрощения средств синхронизации. Последнее достигается исключением из состава модуля одного буферного запоминающего блока, одной схемы сравнения, регистра - счетчика событий, одного выходного коммутатора, трех триггеров, а также пятнадцати логических элементов, элементов задержки и одновибраторов. Вместо указанных элементов и блоков вводятся дешифратор 9 (по сложности эквивалентен выходному коммутатору), генератор 7 констант (по сложности эквивалентен регистру - счетчику событий), а также пять групп логических элементов. Количество элементов в каждой группе определяется максимальным числом n вершин синхронизации в реализуемой микропрограмме (для большинства случаев, имеющих место на практике, n составляет от единиц до нескольких десятков). Связи между введенными элементами являются однотипными, что обусловливает регулярность средств синхронизации (см. фиг. 1).

Таким образом, предлагаемое техническое решение обеспечивает возможность повышения оперативности синхронизации параллельных участков микропрограмм в ММКС при одновременном упрощении модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может найти применение при построении управляющих и вычислительных систем высокой производительности, а также подсистем логического управления многоуровневых иерархических автоматизированных систем управления. Технической задачей изобретения является повышение оперативности синхронизации параллельных участков микропрограмм в мультимикроконтроллерной сети за счет минимизации времени между моментом завершения параллельных участков и моментом появления соответствующего сигнала-признака при одновременном упрощении модуля. Устройство содержит блок памяти микропрограмм, регистр микрокоманд, регистр адреса, мультиплексор логических условий, буферный запоминающий блок, два генератора констант, схему сравнения, триггер запуска, коммутатор адреса, два генератора тактовых импульсов, выходной коммутатор, триггер, пять элементов И, пять элементов ИЛИ, одновибратор, три элемента задержки, дешифратор номера вершины синхронизации, три группы элементов И и две группы элементов ИЛИ. 5 ил.