Изобретение относится к вычислительной технике и может быть использовано при исследовании надежности низкочастотных электронных схем на стадии Их проектирования, опытной отработки и крупносерийного производства.

Известно устройство для моделирования электронных схем, содержащее датчик равномерно распределенных случайных чисел, выход которого через дешифратор соединен . с первыми входами блоков задания начальных значений параметров и блоков задания текуш.их значений параметров, выходы которых через элемент ИЛИ соединены с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, а выход элемента И соединен с первыми входами счетчиков памяти, реверсивных счетчиков и входом элемента обратной связи, выход которого соединен со вторыми входами блоков задания начальных значений параметров и блоков задания текущих значений параметров, третьи входы которых соединены с выходом коммутатора, вторыми входами счетчиков памяти и вторыми входами реверсивных счетчиков, третьи входы которых соединены с выходом блока управления, третьими входами счетчиков памяти, четвертыми входами блоков задания начальных значений параметров и блоков задания текущих значений параметров, первым входом коммутатора и входом датчика равномерно распределенных случайных чисел, выходы реверсивных счетчиков соединены со входами соответствующих наборных полей, сумматоры, генераторы тактовых импульсов, выходы которых через соответствующие сумматоры соединены с четвертыми входами со10ответствующих реверсивных счетчиков, выходы счетчиков памяти соединены со входами соответствующих сумматоров, исследуемую схему, входы которой соединены с выходами наборных полей, блок измерений, вход которого соединен с выходом исследуемой с.хе15мы 1.

Известное устройство позволяет моделировать процессы изменения параметров электронных, схем по появлению первого постепенного отказа или до какого-то заранее заданного фиксир.ованного момента времени.

20 То-есть ,с помощью известного устройства можно исследовать надежность лишь невосстанавливаемых схем. Однако электронные схемы в большинстве своем являются восстанавливаемыми. Поэтому исследование электронных схем лишь до первого отказа является недостаточным, так как не дает полной информации об их надежности. В связи с этим возникает задача создания устройства для моделирования процессов изменения параметров электронных схем с более широкими функциональными возможностями, позволяющего исследовать как невосстанавлива мые, так и восстанавливаемые электронные схемы.

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования процесса восстановления.

Для достижения поставленной цели устройство содержит первый, второй, третий и четвертый регистры памяти, блок вычитания, блок сравнения, дополнительный блок управления, дополнительный коммутатор, первую и вторую группы блоков памяти, блок регистрации, вход которого соединен с выходами наборных полей, а выход блока регистрации соединен со входом первого регистра памяти, выход которого подключен к первому входу блока вычитания, второй вход которого соединен с выходом второго регистра памяти, а выход блока вычитания соединен с первыми входами третьего регистра памяти и блока сравнения, второй вход которого подключен к выходу третьего регистра памяти, а выход блока сравнения подключен к выходу третьего регистра памя-ти, а выход блока сравнения подключен ко входу дополнительного блока управления, выход которого соединен со вторым входом третьего регистра памяти, со входом дополнительного коммутатора и с первым входом четвертого регистра памяти, выход которого подключен ко второму входу коммутатора, а второй вход четвертого регистра памяти соединен с выходом дополнительного коммутатора и с четвертыми входами реверсивных счетчиков, пятый и шестой входы которых соединены с выходами первой и второй г,рупп блоков памяти соответственно, первые входы которых объединены между собой и с третьими входами реверсивных счетчиков, вторые входы которых объединены со вторыми входами второй группы блоков памяти.

Основные предпосылки, на которых основана работа предлагаемого устройства, заключаются в следующем. Исследуемая схема состоит из п элементов, каждый из которых характеризуется определяющим параметром Х|, i 1,2,...,п. Выходной параметр схемы Y функционально связан с параметрами элементов зависимостью у f (х 1,хг,..,х„) Схема является исправной, если ее выходной параметр находится в пределах поля допуска

Ymm.Y YraAX

Ynnn YniAx соответственно нижняя и верхняя границы поля допуска

В процессе эксплуатации из-за износа и старения параметры элементов х(1)изменяются случайным образом, вызывая изменения выходного параметра схемы (i. При достижении последним одной из границ поля

допуска фиксируется отказ схемы.

Работоспособность схемы восстанавливается путем замены одного из комплектующих элементов новым. В результате такой замены выходной параметр у возвращается в поле допуска. Однако качество восстановления схемы при замене различных комплектующих элементов не одинаково, поэтому цеелесообразно выбрать такой элемент, замена которого приведет к более качественному восстановлению (назовем такой элемент аварийным). Для выявления «аварийного

элемента необходима количественная оценка, которая позволила бы стравнивать качество восстановления при замене разных комплектующих элементов новыми. Такой оценкой является разность

Yi. -Уйот

где у„ог71-номинальное значение выходного параметра исследуемой схемы (известное, например из технических условий);

Y - значение выходного параметра 5схемы в момент отказа при возвращении параметра i-io элемента в начальное состояние.

В качестве «аварийного элемента принимается такой элемент, замена которого дает возможность максимально приблизить выходной параметр схемы к его номинальному значению. То есть критерием для выбора «аварийного элемента является величина

AYrnm min /Y; - Ynom/ п ilРассмотрим восстановление схемы в моь5ент

j первого отказа t.. Если в начальный момент времени 1 0 параметры всех эле.ментов имели значения Х(0), i 1,2,...,п, то к моменту отказа t tt они изменились и приняли значения Xi(t,). В результате наступил постепенный откан схем1з1, то есть ее выходной параметр принял одно из значений Y(rO Ymin или (i) Для выявления «аварийного Эс.чемента производится поочередная замена каждого комплектующего элемента новым и при этом из.меряется значение выходного параметра. Для этого вначале первому элементу задают начальное значение параметра х(О), а параметры всех остальных элементов остаются в том состоянии х,(10 i 2,3,...,п, в каком они оказались в момент отказа. Измеряют знаg чение выходного параметра yi и вычисляют разность I&YI Y Ynom- Затем в начальное состояние хг(0) возвращают пара.метр второго элемента, а параметры всех остальных элементов, в том числе и первого, должны иметь значения X(ti), i f 2. Снова из5 меряют значения выходного параметра у

и вычисляют разность Дуа }z-Углт и т. д.

Сравнение всех разностей Ду, i 1,2,..,Г7,

позволяет определить, какой из элементов

схемы в данном случае является «аварийным. Затем выявленный «аварийный элемент заменяется новым,и исследуемая схема работает до следующего отказа, при появлении которого снова производится восстановление работоспособности схемы и т. д. Таким образом, получен поток отказов одного экземпляра исследуемой схемы.

Для расчета показателей надежности восстанавливаемой схемы необходимо аналогичным образом получить данные о потоках отказов множества экземпляров схемы. Эти данные можно получить, если непосредственно в действующем макете исследуемой схемы задать для всех п комплектующих элементов схемы случайные начальные значения параметров х(0) и случайные скорости их изменения; одновременно для всех комплектующих элементов воспроизвести реализации случайных процессов x-Jt) в соответствии с сформированными начальными значениями и скоростями, измеряя при этом выходной параметр схемы (i), при наступлении отказа выявить «аварийный элемент и заменить его новым, то есть сформировать для этого элемента новое начальное значение параметра и скорость его изменения.

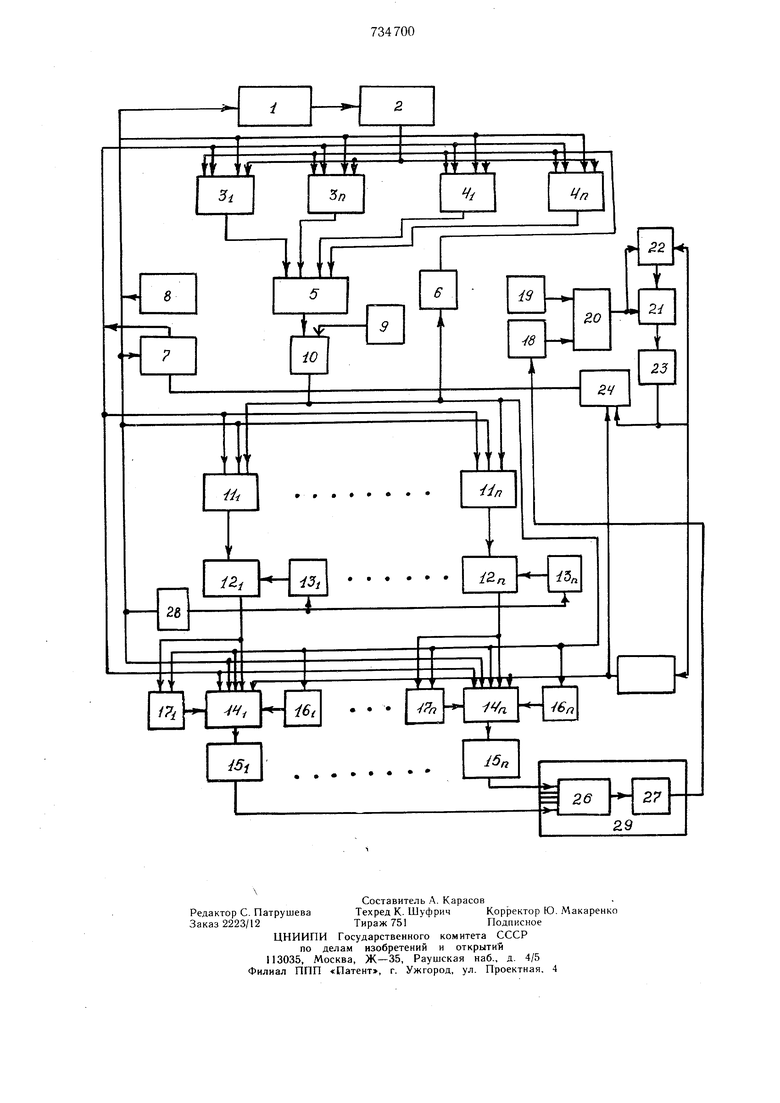

На чертеже представлена блок-схема устройства.

Устройство содержит датчик 1 равномерно распределенных случайных чисел дещифратор 2, блоки 3i-Зп задания начальных значений параметров (они формируют законы распределения начальных значений параметров элементов), блоки 4i-4.задания текущих значений параметров (они формируют законы распределения скоростей изменения параметров элементов), элемент 5 ИЛИ, элемент 6 обратной связи,коммутатор 7, блок 8 Управления, генератор 9, элемент 10 И, счетчики - « памяти, сумматоры , генераторы 3(-13п тактовых импульсов, реверсивные счетчики 4), наборные поля , первую группу блоков 164-16п памяти, вторую группу блоков 171-17ппамяти, первый регистр 18 памяти. второй регистр 19 памяти, блок 20 вычитания, блок 2 сравнения, третий регистр 22 памяти, дополнительный блок 23 управления четвертый регистр 24 памяти, дополнительный Коммутатор 25, имитатор 26 исследуемой электронной схемы, блок 27 измерений, генератор 28 тактовых импульсов. Блоки 26 и 27 образуют блок 29 регистрации.

Датчик i равномерно распределенных случайных чисел предназначен для выработки по командам из блокаВ управления независимых случайных чисел, распределенных по равномерному закону. Числа с датчика 1 поступают на вход дешифратора 2, который устроен так, что обеспечивает возможность получения на его выходах сигналов с различными, заранее известными вероятностями появления. Блоки 3i-Зп задания начальных значений параметров и блоки i-4п

задания текущих значений параметров предназначены для формирования требуемых законов распределения. При этом в блоках с помощью коммутационных панелей формируются требуемые законы распределения начальных значений параметров элементов. В блоках аналогичным образом формируются требуемые законы распределения скоростей изменения параметров элементов. Выходы блоков и 4t-4п подключены через элемент 5 ИЛИ к первоо му входу элемента 10 И, ковторому входу которого подключен генератор 9 регулярных импульсов. Такое соединение позволяет выработать 2п случайных последовательностей импульсов, используя только один датчик случайных чисел с дешифратором и только один элемент обратной связи. Элемент 6 обратной связи предназначен для преобразования значения вероятности в такое количество импульсов, которое равно числу, соответствующему этой вероятности в сформированном законе распределения. Выработанные случайные последовательности импульсов с выхода элемента 10 И поступают в счетчики ( памяти, реверсивные счетчики 4 ,- 4п, в первую группу блоков памяти, и во вторую группу блоков 71-17„

памяти. Сумматоры в совокупности с генераторами 13i-13п образуют преобразователи число-частота. Каждый из них преобразует число, занесенное в счетчик 1 памяти, в последовательность импульсов, часU тота которых пропорциональна числу счетчика 1.

Реверсивные счетчики 4i-14п совместно с наборными полями 15i-15п выполняют функции исполнительного органа. Счетчики 14 1-14п выполнены реверсивными для

5 того, чтобы иметь возможность воспроизводить реализации случайных процессов как с положительной, так и с отрицательной скоростью.

Выходы реверсивных счетчиков соединены со входами соответствующих на борных полей , на которых набраны упорядоченные по моделируемому параметру ряды однотипных элементов. В данном случае ряды элементов представляют собой макеты реальных элементов, изменение параметров которых моделируется в исследуемой электронной схеме. При этом изменение параметра моделируется путем подключения к выходам наборного поля 15, а значит и в исследуемую схему 26, элементов с различным значением моделируемого параметра.

Блок 27 измерения предназначен для измерения выходного параметра схемы и перевода его в двоичный код, который заносится в регистр 18.

Регистр 18 предназначен для хранения двоичного , соответствующего номинальному значению выходного параметра. Блок 21 сравнения предназначен для сравнения поступающей с блока 20 вычитаiiriH разности uYi, зкачеиня uYmin которое хранится Б регистре 22. Номер элемента, которому соответствует .А,у„;,загюминаетея в регистре 24. Блок 8 управления, блок 23 управления и коммутаторьч 7 и 25 имеют М11ожест(ю различных но функциональному назначению выходов. Для унроняения чертеж., выходы каждого из них показаны одной линией. Блоки 8 23 Ю заранее заданной программе реализуют цикл гуюделирования, а коммутаторы 7 и 25 по командам из блока управления включают в работу соответетвуюш.ие блоки и устройства. Устройство работает следующим образо .м. Перед началом моделирования в блоках 3i-Зп и устанавливаются соответствующие законы распределения. В регистр 19 заносится номинальное значение выходного параметра исследуемой схемы Y пот з двоично.м коде. На наборных полях 15.;-15п устанавливаются упорядоченные ряды элементов. Командой из блока 8 устройство нриводится в исходное состояние: коммутатор 7 переводится в нулевое положение, а счетчики i 11-lin, 14 1-14n, 13 , блоки памяти 16r--l6n, и 17,- 17п сбрасываются в моль. По команде из блока 8 коммутатор 7 устанавливается в первое ноложепие, а з датчике 1 формируется случайное число, которое через деп1ифратор 2 поступает на вход блока 3.. Для получения заданного значения случайной величины ||реобразозанное случайное число с выхода блока 3- поступает через .элемент 5 ИЛИ на элемент 10 И и дает разреиюпие на прохождение регулярпьгк ИМПУЛЬСОВ с i-enepaTopa 9 на элемент 6 обратной связи, на счетчик 14, в блоки памяти 16; и 17 |. При совг1аде;:пп в б.локе 3 сигнала, соответствуюп1его сфер ми pofsa иной вероятности, и С-икала, поступающего с элемента 6, стирается pa3peHjeHHe нй npcjхождение импульсов через элемент 10 И и прекращается поступле:-1|.1е и.мнульсов на счетчик 14; в блоки 16 и 17| памяти. Таким образо.м, в счетчик 14 ь блохи, 15-: и 17 i па.мяти заносится число, соответствующее 15ероятностп, сфор.мировапной блоком 3-,. Из упорядоченной совокупности эле.ментов, установленных на первом наборном поле 5i, нара.метр Этого эле.мепта сс ответствует С(()ормированному в блоке 3ч начальному значению параметра .первого элемента xi (0). С блока 8 подается команда на перевод коммутатора 7 во второе положение и на «рормирование в датчике нового случайного числа. В исследуемую схему включается один из элементов, установленных на наборном ноле 152, с параметром ха (0) в соответствии с вероятностью, сформированной в блоке За. Коммутатор 7 переключается в следующие положения и в исследуемую .электронную схему аналогичным образом подключаются оставшиеся (п-2) элемента с параметрами соответственно х;-,(()),.,. 734 .... Xf(,{0). Таким образом, носле п-го щага коммутатора 7 значения параметров комплектующих элементов исследуемой схемы и ее выхо.дных параметров соответствуют начальному мо.менту времени (t 0). Затем производится формирование случайных чисел, соответствующих скоростям изменения параметров комплектующих эле.ментов, и запоминание их в счетчиках 111 - lln. Для этого по команде из блока 8 снимается разрегненне на прохождение сигналов на блоки 3v -Зп, реверсивные счетчики 14,-14п, блоки I6j - 16п и 17 - 17п памяти, одновременно подается разрещение на прохождение сигналов на блоки 4,-4f, и счетчики 11.1-51ii- Командой из блока 8 коммутатор 7 переводится в первое положение. В датчике 1 формируется случайное число, которое с помонлью б.пока 4, элемента 5, элемента 10, 1енератора 9 и элемента 6 преобразуется в число, соответствующее вероятности, сформированной блоком 4i. Это число соответствует скорости изменения первого э.1емента и заносится в счетчик 11 . Преобразование выполняется так же, как для случая формирования числа, заносимого в счетчик 14 (. По команде из блока 8 ком.мутатор 7 переводится во второе положение, а в датчике 1 формируется новое случайное число, которое аналогичпым образом преобразуется в число, пропорциональное скорости измене|;ия параметра второго элемента, и заносится в счетчик 11 2. Точно также заносятся случайные числа в остальные (п - 2) счетчики I 1.3 -11п. На этом заканчиваются подготовигельные онера 1ии, в резу;1ьтате которых сформированы случайные начальные значения и скорости изменения пар- етров веех ко.мп;р-ктующих эле.ме -1тов од. .о экземпляра исследуемой схемы. Для ьюте.пирования нро:j,eccoB изменения г ара:четроз элементов подается из блока 8, но которой на счетчики 13;-13я поступа:-от импульсы от генератора 28. На выходе блока 12 при совиадснии кодов на его входах появляется импульс. Частота появления имнульсов на выходе каждого из блоков 12 ,-12„ иропорциональпая числу, занесенному в соответствующие с1-:етчики памяти п. С выходив блоков 12, 12п импульсы-поступают ьа входы соответствующих реверсивных счетч1;кон 14 - 14п, пересчитывающих эти им:;у.пьсь, и в блоки 17 г--17ц памяти. В соответствии с числами в счетчиках 14)- 4п в исследуемую схему 26 подключаются элементы, установленные на наборных полях 15 . Ч.астота подключения элементов, а следовательно, и скорости из.менения параметров, прямо пропорциональны числам в соответствующих счетчиках 11 (-1 ly, памяти. Для измерения выходного параметра исследуемой электронной схемы в заданные моменты времени блок 8 управления в эти моменты времени подает занрет на прохождение импульсов от генератора 28 на счетчики 131-13,. При этом прекращается выдача всех команд из блока 8 управления. Переключение элементов, установленных на наборных полях 15, также прекращается. На исследуемую электронную схему подается питание и измеряется ее выходной параметр. Процесс моделирования продолжается до тех пор, пока в какой-то момент времени t ti, не будет зафиксировано достижение выходным параметром исследуемой схемы одной из границ поля допуска, что является постепенным отказом. С этого момента по команде оператора моделирование процессов изменения выходного параметра схемы прекращается и начинается процесс восстановления, заключающийся в отыскании и замене «аварийного элемента. Командой из блока 23 устройство приводится в исходное положение: регистры 18, 24 и коммутатор 25 сбрасываются в нулевое положение, в регистр 22 заносится максимально возможное число. По команде из блока 23 дополнительный коммутатор 25 устанавливается в первое положение, в реверсивном счетчике 14i сбрасывается хранившееся там число, соответствующее значению параметра xj (ti), и заносится число из блока памяти 161, соответствующее начальному значению Xi (0) параметра первого элемента. В соответствии с этим числом в схему включается элемент со значением параметра X| (0) из упорядоченной совокупности элементов, установленных на наборном поле 15 i. По команде из блока управления 23 на схему подается питание и измеряется выходной параметр YI, значение которого из блока 27 заносится в регистр 18. Питание схемы отключается. По команде из блока 23 содержимое регистров 18 и 19 поступает на блок 20 вь1читания, где вычисляется разность Лу i Y -Ynom которая в блоке 21 сравнивается с числом регистра 22. Если число Д YI в блоке 20 вычитания меньше или равно числу в регистре 22, то блок 21 выдает команду на сброс числа в регистре 22 и перенос в этот регистр числа из блока вычиfaния 20. Этой же командой в регистр 24 заносится номер положения дополнительного коммутатора 25. Таким образом, в регистр 24 заносится номер элемента, имеющего наименьщее в данный момент значение. Поскольку при сбросе в исходное состояние в регистр 22 было занесено максимально возможное число, то разность Ду1 всегда будет не больше этого числа. Поэтому в первом положении дополнительного коммутатора 25 в регистр 24 всегда будет заноситься число «1. Затем из блока 23 подается команда на перевод коммутатора 25 во второе положение, в котором производится сброс в счетчиках 4 и 14а хранившихся там чисел и перенос в эти счетчики чисел из блоков памяти со ответственно 17i и 16г. В соответствии с числа ми в счетчиках 14i и 14г происходит подключе ние в схему .элементов со значениями параметров xi (ti) и ха (0), установленных на на-борных полях 151 и ISa- Переключения приводят исследуемую схему в такое состояние, когда все комплектующие ее элементы, кроме второго, имеют такое же значение параметра х;., что и в момент отказа, а параметр второго элемента возвращен в начальное состояние Х2 (0). Аналогично вычисляется разность Дуг и полученное значение сравнивается с Дуь хранящимся в регистре 22. Меньшая из разностей заносится в регистр 22, а соответствующий ей номер элемента заносится в регистр 24. Последовательным выполнением операций над всеми остальными (п-2) элементами исследуемой схемы, определяется минимальная разность UYmin., которая запоминается в регистре 22, и номер элемента, соответствующего этой минимальной разности, то есть номер «аварийного элемента, который запоминается в регистре 24. Таким образом, задача выявления «аварийного элемента выполнена. Теперь необходимо заменить этот элемент новым, то есть сформировать для него новое начальное значение параметра и скорость его изменения. Для этого по команде из блока 23 номер «аварийного элемента заносится из регистра 24 в коммутатор 7, и дальнейщее управление передается блоку 8 управления. По команде из блока 8 в соответствии с положением коммутатора 7 производится сброс прежних начального значения и скорости изменения параметра «аварийного элемента, формирование новых случайных чисел и занесение их в счетчики 11, 14 и блоки 16, 17 памяти. Все эти операции выполняются только для одного «аварийного элемента. Параметры всех остальных элементов остаются в том же состоянии, в каком они оказались в момент отказа t t. После восстановления работоспособности схемы снова продолжается процесс моделирования изменения параметров до момента времени t tj, когда произойдет второй отказ. Снова производится восстановление работоспособности схемы. Затем моделирование и восстановление производится до третьего и последующих отказов. При этом работа предлагаемого устройства в процессе моделирования и восстановления при всех других отказах производится аналогично тому, как это описано для первого отказа. В результате проведения одного цикла моделирования получают поток отказов одного экземпляра исследуемой схемы. Для получения потока отказов второго экземпляра схемы проводят второй цикл моделирования, для чего устройство для моделирования приводится в исходное состояние, формируются новые случайные начальные значения и скорости изменения параметров всех комплектующих элементов и производится процесс моделирования и восстановления. Многократное повторение циклов моделирование дает возможность получить статические данные, необходимые для расчета показателей надежности восстанавливаемой электронной схемы. Постепенные отказы электронных схем являются следствием изменения по времени параметров комплектующих элементов. Рабо тоспособность схемы после отказа может быть восстановлена путем замены нескольких или одного комплектующего элемента новым. Следовательно, восстановление работоспособности электронных схем не вызывает особых затруднений. В связи с этим электронные схемы в большинстве своем являются восстанавливаемыми. Известное устройство, являющееся прототипом предлагаемого изобретения, позволяет моделировать процессы изменения параметров электронных схем до появления первого постепенного отказа. То есть с помощью известного устройства можно прогнозировать показатели надежности лишь невосстанавливаемых схем. Формула изобретения Устройство для моделирования электронных схем, содержащее датчик равномерно распределенных случайных чисел, выход которого через дешифратор соединен с первыми входами блоков задания начальных значений параметров и блоков задания текущих значений параметров, выходы которых через элемент ИЛИ соединены с первым входом элемента И, второй вход которого соедйнен с выходом генератора импульсов, а выход элемента И соединен с первыми входами счетчиков памяти, реверсивных счетчиков и входом элемента обратной связи, выход которого соединен со вторыми входами блоков задания начальных значений параметров и блоков задания текущих значений параметров, третьи входы которых соединены с выходом- коммутатора, вторыми входами счетчиков памяти и вторыми входами реверсивных счетчиков, третьи входы которых соединены с выходом блока управления, третьими входами счетчиков памяти, четверты.ми входами блоков задания начальных значений параметров и блоков задания текущих значений параметров, первым входом коммутатора и входом датчика равномерно распределенных случайных чисел, выходы реверсивных счетчиков соединены со входами соответствующих наборных полей, сумматоры, генераторы тактовых импульсов, выходы которых через соответствующие сумматоры соединены с четвертыми входами соответствующих реверсивных счетчиков, выходы счетчиков памяти соединены со входами соответствующих сумматоров, исследуемую схему, входы которой соединены с выходами наборных полей, блок измерений, вход которого соединен с выходом исследуемой схемы, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования процесса восстановления, оно содержит первый, второй, третий и четвертый регистры памяти, блок вычитания, блок сравнения, дополнительный блок управления, дополнительный коммутатор, первую и вторую группы блоков памяти, блок регистрации, вход которого соединен с выходами наборных полей, а выход блока регистрации соединен со входом первого регистра памяти, выход которого подключен к первому входу блока вычитания, второй вход которого соединен с выходом второго регистра памяти, а выход блока вычитания соединен с первыми входами третьего регистра памяти и блока сравнения, второй вход которого подключен к выходу третьего регистра памяти, а выход блока сравнения подключен ко входу дополнительного блока управления, выход которого соединен со вторым входом третьего регистра памяти, со входом дополнительного коммутатора и с первым входом четвертого регистра памяти, выход которого подключен ко второму входу коммутатора, а второй вход четвертого регистра памяти соединен с выходом дополнительного коммутатора и с четвертыми входами реверсивных счетчиков, пятый и шестой входы которых соединены с выходами первой и второй групп блоков памяти соответственно, первые входы которых объединены между собой и с третьими входами реверсивных счетчиков, вторые входы которых объединены со вторыми входами второй группы блоков памяти. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2348583/18-24, кл. G 06 F 1/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процессов изменения параметров электронных схем | 1976 |

|

SU634283A1 |

| Устройство для моделирования электронных схем | 1974 |

|

SU518775A1 |

| Устройство для моделированияэлЕКТРОННыХ CXEM | 1978 |

|

SU813440A1 |

| Устройство для моделирования электронныхСХЕМ | 1978 |

|

SU805334A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

| Устройство для моделирования отказов в электронных схемах | 1986 |

|

SU1401476A1 |

| Устройство для моделирования электронных схем | 1976 |

|

SU640303A2 |

| Устройство для моделирования систем управления | 1980 |

|

SU935965A1 |

| Устройство для моделирования отказов | 1986 |

|

SU1363231A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ НАДЕЖНОСТИ ФУНКЦИОНИРОВАНИЯ СИСТЕМ | 1969 |

|

SU255657A1 |

Авторы

Даты

1980-05-15—Публикация

1977-07-20—Подача