входы которых подключены к выходу эле- мента обратной связи, вторые входы - к выходу коммутатора, третьи входы - к первому выходу блока управления, четвертые входы .- к выходу дешифратора, а выходы - ко входам элемента ИЛИ,

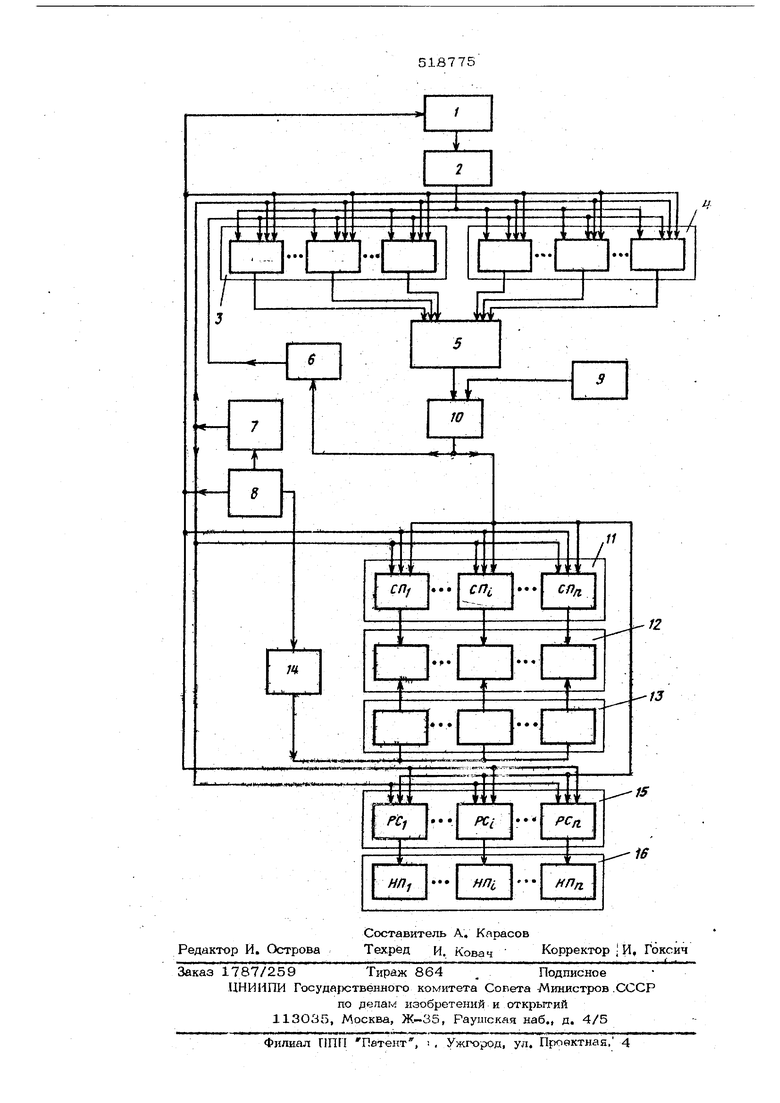

Блок-схема дискретного устройства изображена нч чертеже.

Устройство состоит из датчики равномерно распределенных случайных чисел 1, дешифратора 2, п блоков начальных зна« ченнй параметра ЗиЛ блоков текущих значений параметра 4, элемента 5 ИЛИ, элемеята обратной связи 6, коммутатора Т,; {блока управления 8, генератора им- пульсов 9, элемента 10 И, f счетчиков пам5гги 11, ri блоков сравнения 12, Л I счетчиков воспроизведения 13, генератора тактовых импульсов 14, п реверсивных счеттаков 15, п наборных полей 16. i

Датчик 1 предназначен для выработки

равномерно распределе1шых случайных чисел и соединен с входами дешифратора 2, который обесцвечивает возможность получения на его выходах сигналов с различнымь заранее известными вероятностями. Выходы дешифратора 2 подсоединены ко входам гг бглоков 3 начальных значений параметров элементов схемы и 1ко входам п блокбв 4 текущих значений параметров элементов схемы, в которых набирается необходимый закон распреде ления случайной велич шы. Выходы каждЬго блока подключены ко входам элемента 5 ИЛИ, что позволяет вырабатызать 2 tt случайных последовательностей импульсов, используя при этом только один элемент обратной связи 6 (ЭОС), ЭОС 6 предназначен/дли,преобразования вероятности в такое количество импульсо которое равно числу, сьоответствующему этой вероятности в сформированном законе распределения. Выход ЭОС 6 соединен со входами блоков 3 и 4. Генера- |тор импульсов 9 и выход элемента 5 ИЛИ подключены ко вхсдам элемента 10 И и обеспечивают генерирование последо вательностей импульсов в реверсивные счетчики 15 и счетчики памяти 11. Однвременно выход элемента 1О И подклю.чен ко входу ЭОС 6.

Каждый ИЗвыходов.коммутатора 7 подключен ко входам соответствующих блоков 3 и 4, ко входам соответствующих счетчиков памяти 11 и входам соответствующих реверсивных счетчиков 15 и совместно с блоком управления 8, сигнальные цепи которого также подключены ко входам ук;азанных блоков, обес1.печ11вают при последовательном переключении коммутатора 7 прохождение сигнала блоков 3 и 4 в реверсивнью счетчики 15 и в счетчики памяти 11, входы которых соединены с выходами блоков 3 и 4 через элементы 5 ИЛИ и элемент 10 И, Реверсивные счетчики 15 моделируют точность и процессы износа элементов р&альной исследуемой схемы, которые набраны в огфеделенной последовательности на наборных полях 36 установки. Выходы счетчиков памяти 11 соединены со входами соответствующих блоков сравнения 12, к другим входам которых подсоединены счетчики воспроизведения 13, ко входам последних подключен генератор тактовых

пульсов 14, Выходы набранных-по лей соединены между собой так, что это соединение образует макет исследуемой схемы. В каждый рассматриваемый момент времени к макету подключен только один

из элементов каждого наборного поля.

Работа дискретной установки заключается в следующем. Перед началом работы с блока управления 8 подается команда, приводйщая все блоки в исходное состоя-

ние. Затем с блока управления 8 поступает Следующая команда, по которой в датчике 1 формируется случайное число, а коммутатор 7 перемещается в первое , : положение. Случайное многоразрядное чиспо датчика 1 преобразуется дешифратором 2 в соответствующий случайный сигнал, который в первом положении коммутатора 7 поступает на вход только первого блока 3, С помощью коммутацио1шого поля

й пришедший случайный сигнал приводится в соответствие с определенным числом, которое необходимо выработать. Для выработки этого числа случайный сигнал после блока 3 через эле..1ент 5 ИЛИ поступает на один из входов элемента 10 и дает разрешение на прохождение регу- , лярных импульсов с генератора импульсов 9 на ЭОС 6 и одновременно в рс версив-,

ный счетчик 15 (РС1 ) для отработки на-

чального значения 1-го элемента. Импул1 сы с генератора 9 будут проходить через элемент 10 И до тех цор, пока в блоке 3 не произойдет совпадеШ1е сигналов, что приведет к снятшо разрешения на прохож-

дение импульс в. Таким образом, за время разрешения на реверсивный .счетчик PC пройдет такое число импульсов, которое , соответствует сформированной блоком 3 вероятности. Эти импульсы, поступая на

вход РС , переключат элементы первого Ha6pajffloro поля НП и Подключат к схеме тот элемент, который соответствует определенной вероятности, выработанной при лшшом такте моделирования точности, Дашее с блока управления 8 поступит коман-

)ца, по которой в датчике 1 сформируется новое аначение случаШого числа, а коммутатор 7 перейдет во второе положение Весь цикл работы установки повторяется, и на наборном поле НП отрабатываются ;начальные значения 2-го элемента схемы, ;Этот процесс; отработки будет продолжатьЬя до тех пор пока не будут отработаны на;чальные значения элементов на всех г наборных полях. На этом заканчивается первый так- моделирования точности исследуемой схемы. После этого подается напряжение на исследуемую схему, элементы которой набраны на наборных полях, и замеряется выходной параметр схемы. Проведя множество таких тактов моделирования и измерений, можно получить закон распределения выходного параметра исследуемой схемы и определить различные ее точностные характеристики,

В случае моделирования процесса износа комплектующих элементов работа установки будет проходить в два этапа. Во время 1-го этапа установка срабатывает один такт моделирования точности схемы, после чего начинается второй этап, состоящий из подготовительного и рабочего такта. Подготовительный такт начинается с того, что блок управления снимает разрешение на прохождение сигналов на блоки 3, а .также на прохождение сигналов непосредственно от элемента 5 ИЛИ и элемента 10 И в реверсивные счетчики 15, При этом подается разрешение на прохождение сигналов на блоки 4 от дешифратора 2 и на прохождение импульсов элемента 5 ИЛИ, элемента 1О И а счетчики памяти 11, После этого с блока управления 8 поступает следующая команда, которая формирует в датчике 1 новое случайное число и переводит кок мутатор 7 в первое положение. При моделировании процессов износа случайное число датчика 1, преобразованное дешифратором 2 в ;лучайный сигнал, в первом положении коммутатора 7 будет ууце поступать на вход только первого блока 4, При этом генерирование числа импульсов, соответствующее определенной веро- I ятности, сформированной в соответствии за данным законом распределегия в блоке 4, бу дет проводитьсяточнотаКИМ же способом, :как и генерирование импульсов при мо- . делировании точности. Однако при моделировании износа импульсы от 1 енератора 9 в первом положении коммутатора 7 поступят через элемент 1О И только в ; первый счетчик памяти 11 (СП), Г

При поступлении с блока управления.8 очередной ком;знды коммутатор 7 перехо|Дит во второе положение и П1 дключае1

1блок 4 через элемент ИЛИ и элемеггг 10 iH ко второму счетчику памяти 11 (СП), в который также заносится число импуль.сов, соответствующее вероятности, сфор|МИрованной уже во втором, блоке 4, Таким образом, после п переключений коммутатора 7 в счетчики памяти будут за|несены случайные последовательности им- пульсов, число которых будет соответство|вать огфеделенной вероятности, выработанной в соответствующих блоках законов распределения скорости. изменения опред&;ляющих параметров, комплектующих |му элементов. На ьгом заканчивается ;ди)д|г товительный такт 2-го этапа и начина ется рабочий такт, заклю аюпшйся в одновременном моделировании процесса изно;са элементов, набранных на наборных по |лях в соответствии с реализациями слу- чайныхфункдий, коэффициенты которых раоОпределены по любому закону, набранному в в блоках 4, Моделирование процесса иэноса в каждом набранном поле начинается от того элемента, который был отработан на 1-ом этапе работы установки, т.е.

при моделировании точности.

Рабочий такт моделирования процесса износа начинается с поступления команды от блока управления 8 на запуск, ге

нератора 14, который выдает импульсы фиксированной частоты на входы вс&х счетчиков воспроизведения 13. При достижении в каждом i i-M счетчике вос1фо Низведения { 1 1, 2 ,,,,, Гг ) равенства

8вс числом, занесенным в соответствующий |счетчик памяти, с выхода 1 -и схемы сравнения выдается импульс на сброс счетчика воспроизведения и одновременно па вход i -го реверсивного счетчика для

40

переключения одного .элемента от того.

который был отработан при моделировании начальных значе.ний параметров элементов схемы (1-й этап работы). После переключения одного элемента на I -м 45|наборном поле импульсы с генератора 14 |снова поступают в I -и счётчик воспроизведения 13 (i) и при достижении равенства и числа импульсов, занесенных в счетчик памяти, происходит очередной сброс I Мг -счетчика воспроизведения и выдача очередного импульса в I -и реверсивный счетчик на переключение элемента в t-м наборном поле и так далее до какого-то фиксированного момента времени t ,. Так как в каж55

дый счетчик памяти 11 было занесено свое случайное число, то и переключение элемен- JTOB в каждом I -м набранном поле будет происходить со своей частотой, отличной от частоты переключения всех остальных

во ячеек. Одиовременное переключение эле7

ентов каждого i -го наборного поля со воей частотой до хакого-то фиксированного момента времени составляет один, такт моделкрования процесса износа исследуемой схемы.

При исследовании надежности схемы процесс моделирования заключается в поспецоватепьном;моделировании до fj -х моментов времени ( J 1, 2 ...... К).

При достижении каждого j -го сечения установка pc,TaHa nHBaeTCHj.Ha схему подается питание, входной сигнал, и измеряется выходной параметр схемы. После-; довательным измерением выходного параметра схемы в tj -е моменты времени получаем, соединив точки измерения прагмой линиеей, одну реализацию изменения выходного параметра схемы во времени. После достижения t / сечения блок управления 8 осуществляет сброс всех счетчиков дискретных ячеек в начальное состояние, после чего начинается второй такт моделирования процессов износа исследуемой схемы. В результате получаем вторую реализацию изменения выходного параметра схемы во времени. При каждчм такте моделирования в L -и. счетчик памяти 11 будет заноситься новое случайное число, в результате частота переключений элементов при каждом такте будет случайной и соответствовать той вероятности, которая была выработана при данном такте моделирования исходя из закона распределения, выбранного в I -м блоке 4,

После множества таких тактов получаем множество реализаций случайного процесса изменения выходного параметра схемы вовремени. Процесс моделирования изменения выходного параметра схемы можно производить или до какого-то фиксироващюго момента времени или до момента, когда выходной паршметр схемы выйдет -эа пределы допуска, что соответствует ее отказу. Полученные данные позволяют определить различные показатели надежности исследуемой схемы, а также характеристики реализаций случай8

ной функцлд изменения выходного параметра схемы во времени.

Формула изобретения

Устройство для моделирования электронных схем, содержащее датчик равномерно распределенных случайных чисел, дещифратор, вход которого соединен с выходом датчика равномерно распределенных случайных чисел, элемент ИЛИ, элемент И, первый вход которого соединен с выходом элемента ИЛИ, а второй вход с выходом генератора импульсов, коммутатор, блок управления, первый выход которого подключен ко входу датчика равномерно распределе1шых случайных чисел, а второй выход - ко входу коммутатора, генератор тактовых импульсов, вход которого соединен с третьим выходом блока управления, отличающееся тем, что, с целью повышенияточьтости; моделирования, устройство дополнительно содериь жкт элемент обратной связи, вход которого подключен к выходу элемента И, it счетчиков памяти, первые входы которых соединены с выходом коммутатора, вторые входы - с первым выходом блока управления, а третьи входы - с выходом элемента И, п блоков сравнения, первые входы которых подключены к выходам счетчиков памяти соответственно, п счетчиков воспроизведения, выходы которых подключены к вторым входам блоков сравнения соответственно, а входы - к выходу генератора тактовых импульсов, п реверси&ных счетчиков, первые входы которых соединены с выходом коммутатора, вторые входы - с первым выходом блока управления; а третьи. входы - с выходом элемента И, п наборных полей, входы кото-

0 рых подключены к выходам реверсивных счетчиков соответственно, П блоков начальных значений параметра и п блоков текущих значений параметра, первые входы ксо-орых подключены к выходу элемента обратной связи, вторые входы - к выходу коммутатора, третьи входы - к первому выходу блока управления, четвертые входы - к выходу дешифратора, а выходы ко входа / элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования электронныхСХЕМ | 1978 |

|

SU805334A1 |

| Устройство для моделирования электронных схем | 1976 |

|

SU640303A2 |

| Устройство для моделирования электронных схем | 1977 |

|

SU734700A1 |

| Устройство для моделированияэлЕКТРОННыХ CXEM | 1978 |

|

SU813440A1 |

| Устройство для моделирования отказов в электронных схемах | 1986 |

|

SU1401476A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1976 |

|

SU634283A1 |

| Устройство для моделирования отказов | 1986 |

|

SU1363231A1 |

| Устройство для вероятностного моделирования работы транспортных систем | 1988 |

|

SU1612313A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

Авторы

Даты

1976-06-25—Публикация

1974-12-30—Подача