1

Изобретение относится к области вычислительной техники и может быть использовано для оптимизации параметров и анализа надежности низкочастотных электронных схем на стадии их проектирования и опытной отработки.

Наиболее близким по технической сущности к изобретению является устройство для моделирования электронных схем по авт. св. № 518775.

Известное устройство содержит датчик равномерно распределенных случайных чисел, дешифратор, вход которого соединен с выходом датчика равномерно распределенных случайных чисел, элемент ИЛИ, элемент И, первый вход которого соединен с выходом элемента ИЛИ, а второй вход - с выходом генератора импульсов, коммутатор, блок управления, первый выход которого подключен ко входу датчика равномерно распределенных случайных чисел, а второй выход - ко входу коммутатора, генератор тактовых импульсов, вход которого соединен с третьим выходом блока управления, элемент обратной связн, вход которого полключен к выходу элемента И, п счетчиков памяти, первые входы которых соединены с выходом коммутатора, вторые входы - с первым выходом блока управления, а третьи входы - с выходом элемента И, п блоков сравнения, первые входы которых подключены к выходам счетчиков памяти соответственно, п счетчиков воспроизведения, выходы которых подключены к вторым входам блоков сравнения соответственно, а входы - к выходу генератора тактовых имнульсов, п реверсивных счетчиков, первые входы которых соединены с выходом коммутатора, вторые входы - с первым выходом блока управления, а третьи входы - с выходом элемеита И, и л наборных полей, входы которых подключены к выходам реверсивных счетчиков соответственно, п блоков текущих значении параметра, первые входы которых подключены к выходу элемента обратной связи, вторые входы - к выходу коммутатора, третьи входы - к первому выходу блока управления, четвертые входы - к выходу дешнфратора, а выходы - ко входам элемента ИЛИ.

Известное устройство не позволяет производить оптимизацию параметров элементов низкочастотных электронных схем.

Целью изобретения является расширение функциональных возможностей устройства, позволяющих одновременно производить оптимизацию параметров элементов низкочастотных электронных схем и анализ их надежности.

Для этого в устройство введены дополнительно блок анализа и д каналов, каждый из которых содержит блок изменения номинальных-значений параметра, блок задания вероятности увеличения параметра, блок памяти, дополнительный реверсивный счетчик и блок ограиичений, выход которого соединен с иервыми входами блока изменения номинальных значений параметра и блока задания вероятности увеличения параметра, выход которого подключен ко второму входу блока изменения номинальных значений параметра, выход которого через блок памяти, соответствующего канала соединен со вторым входом блока задания вероятности увеличения параметра и с одним входом дополнительного реверсивного счетчика, другие входы которого подключены к соответствующим выходам блока памяти и блока управления, выход дополнительного реверсивного счетчика соединен со вторым входом наборного поля соответствующего канала, выход каждого из которых подключен ко входу блока ограничений соответствующего канала и к одному из входов блока анализа, выход которого соединен с третьими входами блоков задания вероятности увеличения параметра и со входом блока управления, выход которого подключен к четвертым входам блоков задания вероятности увеличения параметра и к третьему входу блока изменения номинальных значений параметра, четвертые входы которых подключены к выходу дешифратора.

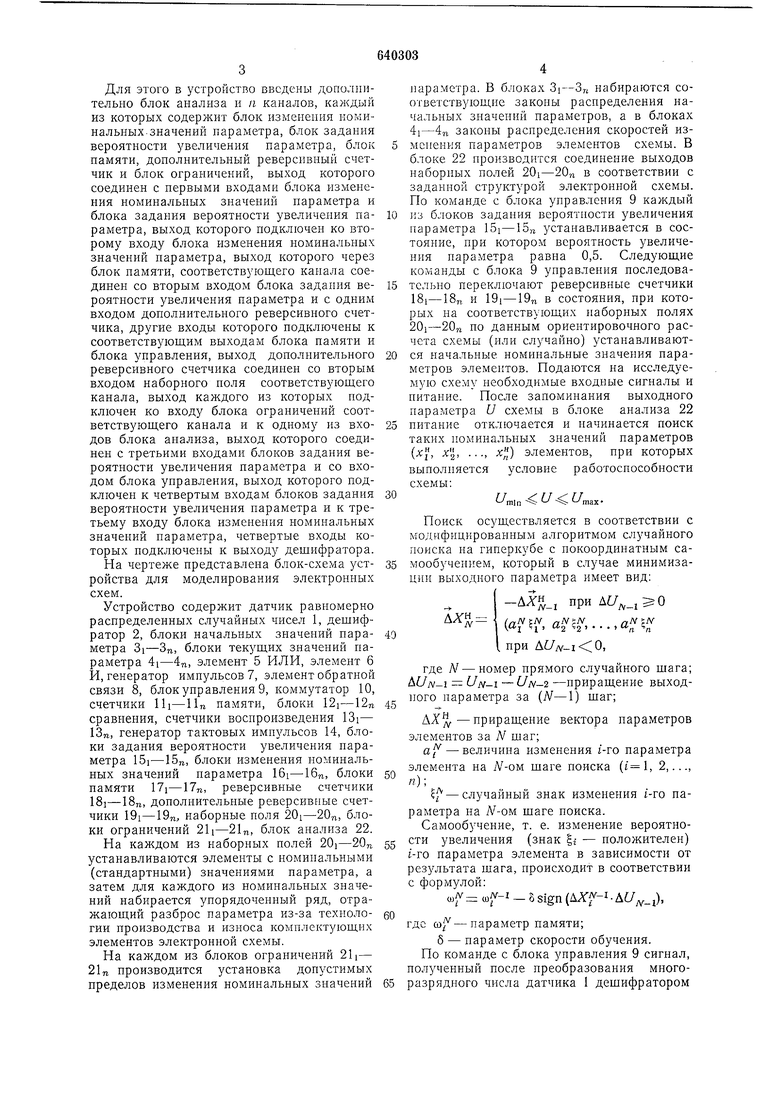

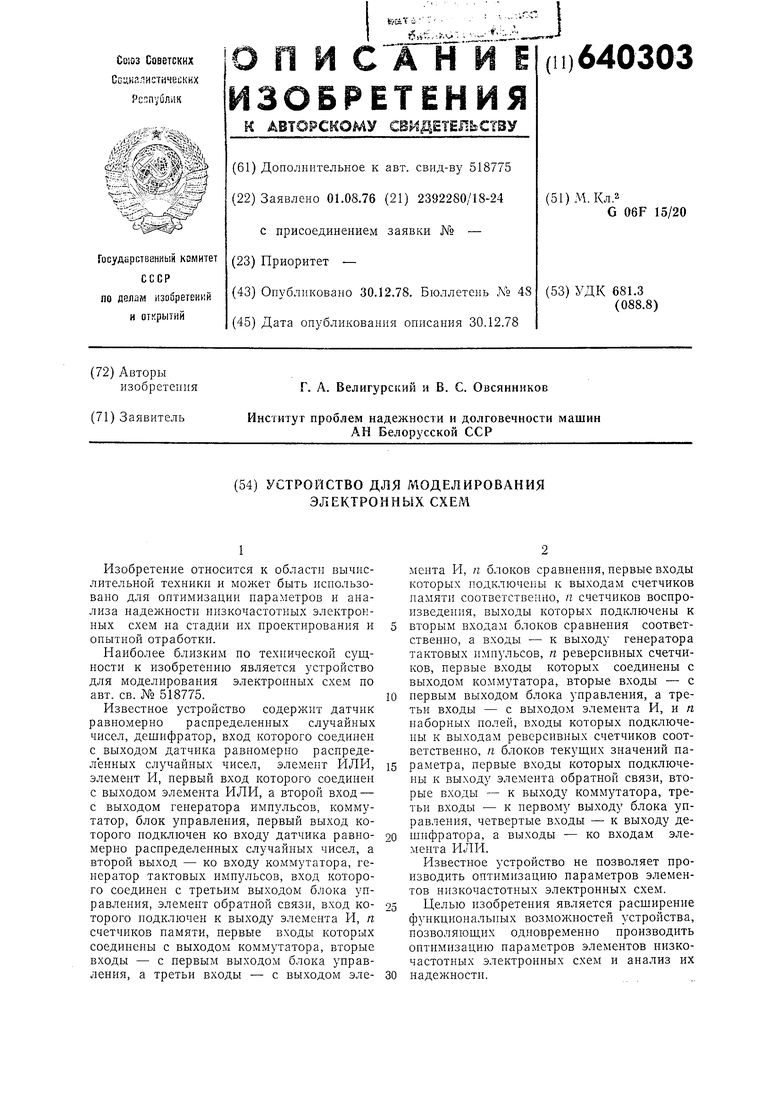

На чертеже представлена блок-схема устройства для моделирования электронных схем.

Устройство содержит датчик равномерно распределенных случайных чисел 1, дешифратор 2, блоки начальных значений параметра 3i-Зи, блоки текущих значений параметра 4i-4п, элемент 5 ИЛИ, элемент 6 И, генератор импульсов 7, элемент обратной связи 8, блок управления 9, коммутатор 10, счетчики 111-Ни памяти, блоки 12i-12и сравнения, счетчики воспроизведения 13i- 13и, генератор тактовых импульсов 14, блоки задания вероятности увеличения параметра 15i-15п, блоки изменения номинальных значений параметра 16i-16„, блоки памяти 17i-17и, реверсивные счетчики , дополнительные реверсивные счетчики 19i-19п, наборные поля 20i-20„, блоки ограничений 211-21„, блок анализа 22.

На каждом из наборных полей ,1 устанавливаются элементы с номинальными (стандартными) значениями параметра, а затем для каждого из номинальных значений набирается упорядоченный ряд, отражающий разброс параметра из-за технологии производства и износа комплектующих элементов электронной схемы.

На каждом из блоков ограничений 211- 21и производится установка допустимых пределов изменения номинальных значений

параметра. В блоках 3i-3„ набираются соответствующие закоиы распределения начальных значений параметров, а в блоках 4i-4„ законы распределения скоростей изменения параметров элементов схемы. В блоке 22 производится соединение выходов наборных полей 20i-20„ в соответствии с заданной структурой электронной схемы. Ио команде с блока управления 9 каждый

из блоков задания вероятности увеличения параметра 15i-15„ устанавливается в состояние, при котором вероятность увеличения параметра равна 0,5. Следующие команды с блока 9 унравления последовательно переключают реверсивные счетчики 18i-18„ и 19i-19„ в состояния, при которых на соответствующих иабориых полях по данным ориентировочного расчета схемы (или случайно) устанавливаются начальные номинальные значения параметров элементов. Подаются на исследуемую схему необходимые входные сигналы и питание. Иосле запоминания выходного параметра U схемы в блоке анализа 22

питание отключается и начинается поиск таких номинальных значений параметров

(х, х ) элементов, при которых

выполняется условие работоспособности схемы:

Г7 II

-% i- -% - шахПоиск осуществляется в соответствии с модифицироваиным алгоритмом случайного поиска на гиперкубе с покоординатным самообученнем, который в случае минимизации выходного параметра имеет вид:

, при Ш,

(fjJVtN ,yNflV

1 «2 2 rt га

. при ,

где Л - номер прямого случайного щага; N-1 - N-2 -приращение выходного параметра за () щаг;

А -приращение вектора параметров элементов за Л шаг;

а - величина изменения 1-го параметра элемента на N-ou шаге поиска (, 2,...,

);

f - случайный знак изменения 1-го параметра на Л-oM шаге поиска.

Самообучение, т. е. изменение вероятности увеличения (знак j - положителен) i-ro параметра элемента в зависимости от результата шага, происходит в соответствии с формулой:

(«л - 8 sign (. ,

где cof -параметр памяти;

б-параметр скорости обучения. По комаиде с блока управления 9 сигнал, полученный после преобразования многоразрядного числа датчика 1 дешифратором

2, поступает на соответствующие входы блоков 16i-16,1. По СоТедующен команде с блока управления 9 сигнал с выхода блока 16 переключит реверсивпый счетчик 19i, в результате чего на наборном поле 20 произойдет изменение (увеличение или уменьшение с вероятностью, равной 0,5) поминального значения параметра Х и одновременно в блоке памяти 17i запоминается знак изменения этого параметра. Затем с блока 9 снова подается команда, по которой случайный сигнал с вы.хода дешифратора 2 поступает на входы блоков 16i-16„, а по следующей команде сигнал с выхода блока 1б2 переключает реверсивный счетчик 192 в состояние, нри котором на наборном поле 202 с вероятностью, равной 0,5, происходит увеличение либо уменьшение параметра Х При этом знак изменения этого параметра запоминается в блоке памяти 172- Аналогичным образом изменяются номинальные значения остальных (п-2) параметров схемы и запоминаются знаки их изменений в соответствующих блоках 17з-17п- После этого на схему подается питание и производится анализ результата случайного прямого шага (случайных изменений параметров) в блоке анализа 22. Если произошло уменьшение (при минимизации) выходного параметра схемы по сравнению с первоначальным (), то шаг признается удачным и в блоке анализа 22 запоминается новое значение выходного параметра. Питание отключается. После этого с блока управления 9 на входы блоков 15i-15п подается команда, по которой каждый из них на основании информации с соответствующих блоков 17i-17п и блока анализа 22 увеличивает вероятность изменения параметра в направлении предыдущего удачного шага в соответствии с выражением (2). Делается новый слзчайный шаг. Если же , то шаг призиается неудачным. Питание схемы отключается. С блока 9 подается команда на входы реверсивных счетчиков , в результате чего на основании информации с блоков памяти 17i-17ri на соответствующих наборных полях устанавливаются первоначальные номинальные значения параметров Х, Х , ... Х , т. е. производится обратный шаг. После этого делается новый случайный шаг.

После этого делается новый случайный шаг. В случае достижения t-ным параметром (, 2, ...п) нижней (верхней) границы допустимого диапазона изменения номинальных значений, с выхода блока 21г дается запрет на уменьшение (увеличение) параметра в блоке 16j и на изменение вероятности увеличения параметра в блок 15;. В результате ряда удачных шагов определяются такие параметры элементов, для которых выходной параметр схемы находится

в трсбуслплх пределах. После этого проводится анали:; iuiJioxiiocTii для напдсппо ко.;бинац1 и номипальпых значспи liapaMcipOB элементов, то-есть реверсивные счетч11К11 19;-IQn фиксируются в положениях, соответствующих этой комбинации. По командам с блока 9 ком1х утатор 10 переводится в первое положение, датчик 1 формирует случайное число, резерсивиые

счетчики 18i-18„ устанавливаются в исходное еоето; 11ие. По следуюгцей команде елучайный сигнал с дешифратора 2 поступает на вход блока Зь с выхода которого случайное число через элемепт ИЛИ 5 поступает па один из вхсдов элемента И 6 и дает разрешс-uiie ка прохождение регулируемых импульсов с генератора импульсов 7 на вход элемента 8 и вход ревереивпого счетчика 18). При совпадете в блоке 3 еигнала, соответствующего сфор; п рованной вероятности, и сигнала с выхода элемента 8 элемент PI 6 запирается, реверсивный счетчик 18i фиксируется в состояннн, при котором на наборном поле 20i устанавливается

значение параметра Xi в соответетвии с сформированной вероятностью. Аналогичным образом устанавливаются остальные (п-1) параметров элементов схемы. Затем на схему иодается пптанпе и пзмеряетея

выходной параметр U, соответствующий начальному моменту времени (t 0). После установки начальных значений п параметров производится моделирование процесса изпоса элементов схемы. По команде с блока управления 9 дастся запрет на прохождение сигналов с дешифратора 2 на блоки 3i-Зп и одновременно поступает разрешение на прохождение этих сигналов па блоки 4i-4„. По следующпм командам с блока 9 формируется число в датчике 1, коммутатор 10 переводится в первое положение, затем случайный сигнал с выхода дешифратора 2 преобразуется с помощью блока 4, элементов 5 н 6, генератора 7, элемента 8 в число, соответствующее сформированной вероятности. Преобразование выполняется также, как и для момепта времени 0. Полученное число заносится в счетчик 111.

Аналогичным образом происходит заиоминание случайных чисел в остальных счетчиках 112-Ик- Затем по команде с блока 9 производится запуск генератора 14, который выдает импульсы фиксировапной частоты на входы счетчиков 13i-13,г. При достижении в каждом 1-ом счетчике воспроизведения (, 2 ... п) равенства с числом соответствующего счетчика памяти с выхода t-ro блока сравнения выдается

импульс на сброс в исходное состояние i-ro счетчика воспроизведения и одновременно на вход f-ro реверснвного счетчика (18,-) для изменения f-ro параметра па соответствующем наборном поле. После этого

происходит новое сравнение чисел счетчи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процессов изменения параметров электронных схем | 1976 |

|

SU634283A1 |

| Устройство для моделирования электронных схем | 1977 |

|

SU734700A1 |

| Устройство для моделированияэлЕКТРОННыХ CXEM | 1978 |

|

SU813440A1 |

| Устройство для моделирования электронныхСХЕМ | 1978 |

|

SU805334A1 |

| Устройство для моделирования процессов изменения параметров электронных схем | 1980 |

|

SU924712A1 |

| Устройство для моделирования отказов в электронных схемах | 1986 |

|

SU1401476A1 |

| Устройство для моделирования электронных схем | 1974 |

|

SU518775A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Генератор случайных чисел | 1983 |

|

SU1124294A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

Авторы

Даты

1978-12-30—Публикация

1976-08-01—Подача