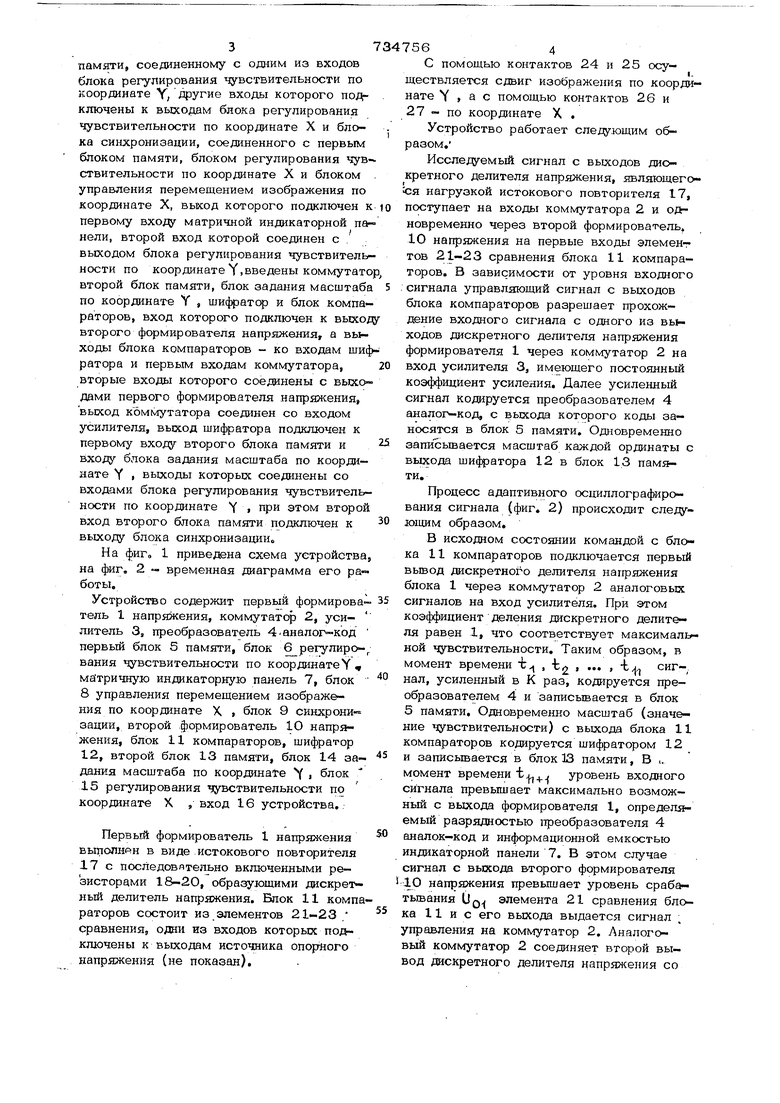

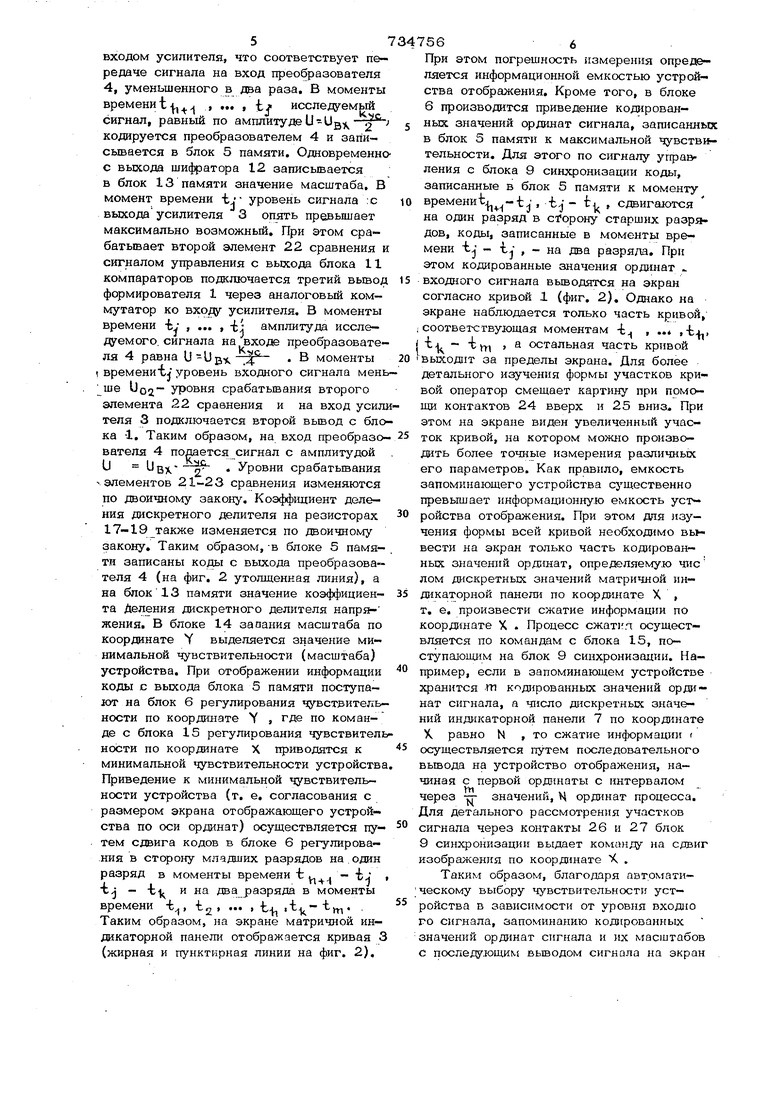

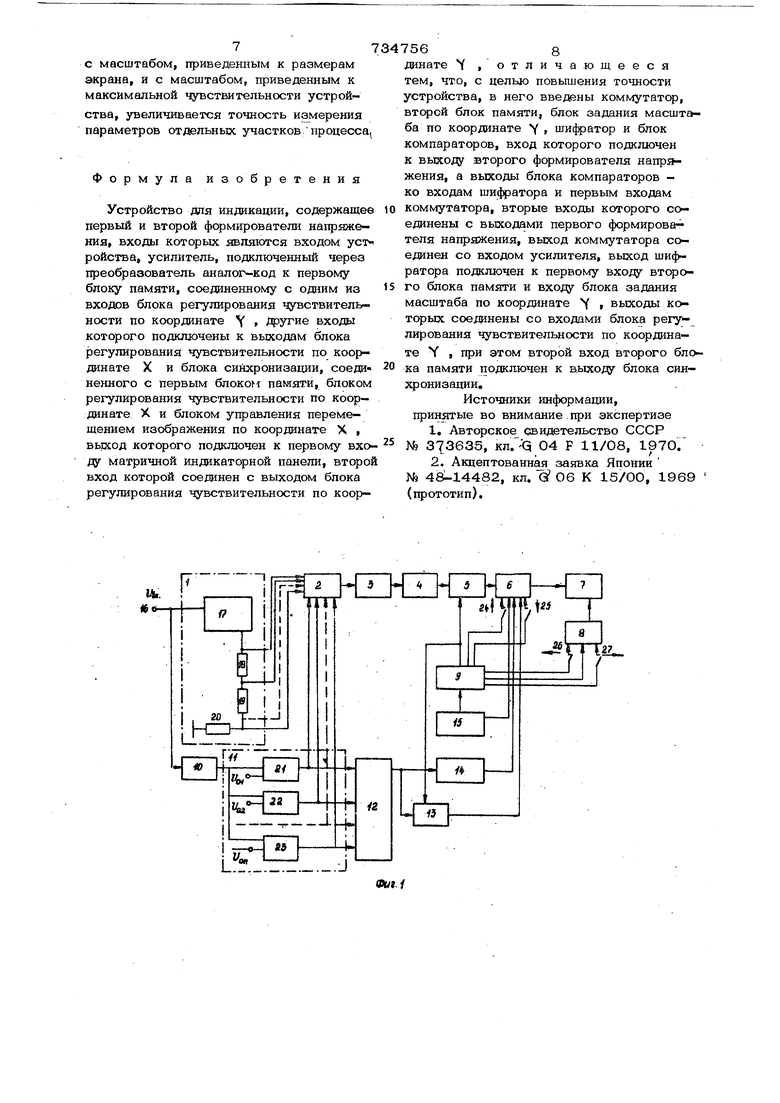

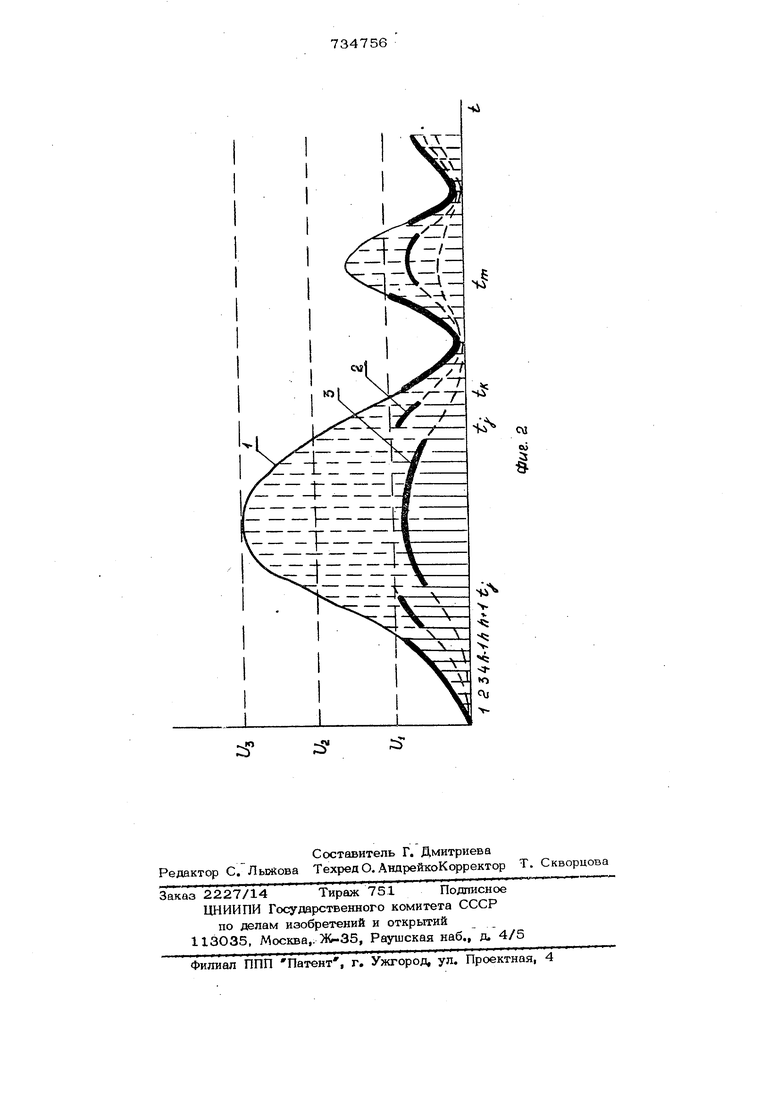

| зобретйние относится к вычислительной технике и может быть использовано в устройствах для индикации с использованием матричной индикаторной панели. Известно устройство, содержащее пснследовательно соединенные датчик, yci литель, преобразователь аналог-код, подключенный к блоку памяти, соединенному с блоком управления, счетчик, триггер, соединенный с элементом И, генератор тактовых импульсов, подключенный к элементу И ll. Недостаток известного устройства - невысокая точность. Наиболее близким по технической сущ кости к изобретению является устройство, содержащее первый и второй формирователи напряжения, входы которых являются входом устройства, усилитель, подключенный через преобразователь ана:лог-код к первому блоку памяти, соеда .ненному с одним из входов блока регулирования чувствительности по координате У , другие входы которого подключены к выходам блока регулирования чувствительности по координате X и блока синхронизации, соединенного с первым блоком памйти, блоком регулирования чувствительности по координате X и блоком управления перемещением изображения по координате К , выход которого подклк чен к первому входу матричной индикаторной панели, второй вход которой соединен с выходом блока регулирования чувотвительности по координате Y Недостаток данного устройства - недостаточно высокая точность, обусловленная отсутствием возможности автоматического выбора чувствительности Bei тикального отклонения. Целью изобретения является повььшение точности устройства. Поставленная цель достигается тем, что в устройство, содержащее первый и второй формирователи напряжения, входы которых Являются входом устройства, усилитель, подключенный через преобразователь аналор-код к первому блоку памяти, соединенному с одним из входов блока регулирования чувствительности по координате Y, лругие входы которого подключены к выходам блока регулирования чувствительности по координате X и блока синхронизации, соединенного с первым блоком памяти, блоком регулирования чувствительности по координате X и блоком управления перемещением изображения по координате X, вькод которого подключен к первому входу матричной индикаторной па нели, второй вход которой соединен с выходом блока регулирования чувствитель ности по координате Y,введены коммутато второй блок памяти, блок задания масштаба по координате Y , ши4чзатор и блок компараторов, вход которого подключен к выхо; второго формирователя напряжения, а вь ходы блока компараторов - ко входам ши4 ратора и первым входам коммутатора, вторые входы которого соединены с выходами первого формирователя напряжения, выход коммутатора соединен со входом усилителя, выход шифратора подключен к первому входу второго блока памяти и входу блока задания масштаба по координате Y вь1ходы Которых соединены со входами блока регулирования чувствитель ности по координате Y i при этом второй вход второго блока памяти подключен к выходу блока синхронизации На фиг 1 приведена схема устройства на фиг, 2 - временная диаграмма его работы. Устройство содержит первый формироваталь 1 напряжения, коммутатор 2, усилитель 3, преобразователь 4.аналог-код первый блок 5 памяти, блок 6 регулирования чувствительности по координатеY ч матричную индикаторную панель 7, блок 8 управления перемещением изображения по координате X блок 9 синхрони- зации, второй формирователь 10 Hanpsiжения, блок 11 компараторов, шифратор 12, второй блок 13 памяти, блок 14 заДания масштаба по координате Y блок 15 регулирования лувствительности по координате X , вход 16 устройства. Первый формирователь 1 напр51жения выполнен в виде истокового повторителя 17 с последов ятельно включенными резисторами 18-20, образующими дискретный делитель напряжения. Блок 11 компа раторов состоит из элементов 21-23 , сравнения, одни из входов которых подключены к выходам источника опорного напряжения {не показан). С помощью контактов 24 и 25 осуествляется сдвиг изображения по коордиате Y а с помощью контактов 26 и 27 - по координате X . Устройство работает следующим обазом. Исследуемьй сигнал с выходов дискретного делителя напряжения, являющегоя нагрузкой истокового повторителя 17, поступает на входы коммутатора 2 и одновременно через второй формирователь 10 напряжения на первые входы элемент тов 21-23 сравнения блока 11 компараторов, В зависимости от уровня входного сигнала управляющий сигнал с выходов блока компараторов разрешает прохождение входного сигнала с одного из вь ходов дискретного делителя напряжения формирователя 1 через коммутатор 2 на вход усилителя 3, имеющего посто5шный коэффициент усиления. Далее усиленный сигнал кодируется преобразователем 4 аналог-код, с эыхода которого коды заносятся в блок 5 памяти. Одновременно запиЪьшается масштаб каждой ординаты с выхода шифратора 12 в блок 13 . Процесс адаптивного осциллографирования сигнала (фиг, 2) происходит следующим образом, В исходном СОСТО5ШИИ командой с блока 11 компараторов подключается первый вьюод дискретного делителя напряжения блока 1 через коммутатор 2 аналоговых сигналов на вход усилителя. При этом коэффициент деления дискретного делителя равен 1, что соответствует максималь ной чувствительности. Таким образом, в момент времени 4: , 2 ... i t сиг-, нал, усиленный в К раз, кодируется преобразователем 4 и записывается в блок 5 памяти. Одновременно масштаб (значение чувствительности) с выхода блока 11 компараторов кодируется шифратором 12 и записьюается в блок 13 памяти, В i, момент времени ( уровень входного сигнала превьпиает максимально возможный с выхода формирователя 1, определяемый разрядностью преобразователя 4 аналок-код и информационной емкостью индикаторной панели 7. В этом случае сигнал с выхода второго формирователя 10 напряжения превьпоает уровень срабатьтания UQ элемента 21 сравнения блока 11 и с его выхода выдается сигнал управления на коммутатор 2, Аналоговый коммутатор 2 соединяет второй вывод даскретного делителя напряжения со

ходом усипителя, что соответствует пеедаче сигнала на вход преобразователя 4, уменьшенного в два раза. В моменты ремени tj, , ... , i,f исследуемый игнал, равный по амплитудеУ-Ug - } 5 кодаруется преобразователем 4 и запиьтается в блок 5 памяти. Одновременновыхода ши атора 12 записывается в блок 13 памяти значение масштаба. В момент времени t-- уровень сигнала :с ю выхода усилителя 3 опять превьпяает максимально возможный. При этом срабатывает второй элемент 22 сравнения и сигналом управления с выхода блока 11 компараторов подключается третий вьтод 15 формирователя 1 через аналоговый коммутатор ко входу усилителя. В моменты времени -k: , ... , -t амплитуда исследуемого, сигнала на входе преобразователя 4 равна U Д В моменты 20 времениЬ уровень входного сигнала мень- ше UGJ- уровня срабатывания второго элемента 22 сравнения и на вход усилителя 3 подключается второй вывод с блока -1. Таким образом, на вход преобразо- 25 вателя 4 подается сигнал с амплитудой U iJax 2 Уровни срабатьтания элементов 21-23 сравнения изменяются по двоичному закону. Коэффициент деления дискретного делителя на резисторах 0 17-19 также изменяется по двоичному закону. Таким образом, -в блоке 5 памяти записаны коды с выхода преобразователя 4 (на фиг. 2 утолщенная линия), а на блок13 памяти значение коэффициен- 35 та Деления дискретного делителя напр жения. В блоке 14 запания масштаба по координате Y выделяется значение минимальной чувствительности (масштаба) устройства. При отображении информации коды с выхода блока 5 памяти поступают на блок 6 регулирования чувствительности по координате Y , где по команде с блока 15 регулирования чувствительности по координате X приводятся минимальной чувствительности устройства. Приведение к минимальной чувствительности устройства (т. е. согласования с размером экрана отображающего устройства по оси ординат) осуществляется пу- ° тем сдвига кодов в блоке 6 регулирования в сторону младших разрядов на один разряд в моменты времени fc у. - Ь fc,j - -fc и на два разряда в моменты времени i, 2 . ... . t| . . . Таким образом, на экране матричной индикаторной панели отображается кривая 3 (жирная и пунктирная линии на фиг. 2).

При этом погрешность измерения определяется информационной емкостью устройства отображения. Кроме того, в блоке 6 производится приведение кодированных значений ординат сигнала, записанны в блок 5 памяти к максимальной чувствительности. Для этого по сигналу управления с блока 9 синхронизации коды, записанные в блок 5 памяти к моменту времениC| -t,|, - t , сдвигаются на один разряд в сГорону старших разрядов, коды, записанные в моменты времени tj - i,j- , - на два разряда. При этом кодированные значения ординат входного сигнала выводятся на экран согласно кривой 1 (фиг. 2), Однако на экране наблюдается только часть кривой, j соответствующая моментам -t. , .. ,-Ьг, i i - -t )т, , а остальная часть кривой ВЫХОДИТ за пределы экрана. Для более детального изучения формы участков кривой оператор смещает картину при помощи контактов 24 вверх и 25 вниз. При этом на экране виден увеличенный участок кривой, на котором можно производить более точные измерения различных его параметров. Как правило, емкость запоминающего устройства существенно превышает информационную емкость устройства отображения. При этом для изучения формы всей кривой необходимо вь вести на экран только часть кодированных значений ординат, определяемую чис лом дискретных значений матричной индикаторной панели по координате X , т. е. произвести сжатие информации по координате X . Процесс сжатия осуществляется по командам с блока 15, по- ступшошлм на блок 9 синхронизации. Например, если в запоминающем устройстве хранится т кодированных значений ординат сигнала, а число дискретных значений индикаторной панели 7 по координате К равно N , то сжатие информации осуществляется путем последовательного вьтода на устройство отображения, начиная с первой ординаты с интервалом через тт- значений, Н ординат процесса. Для детального рассмотрения участков сигнала через контакты 26 и 27 блок 9 синхронизации выдает команду на сдвиг изображения по координате Ч .

Таким образом, благодаря ческому выбору чувствительности устройства в зависимости от уровня входно го сигнала, запоминанию кодированных значений ординат сигнала и их масштабов с последующим вьшодом сигнала на экран с масштабом, приведенным к размерам экрана, и с масштабом, приведенным к максимальной чувствительности устройства, увеличивается точность измерения параметров отдельных участков процесса Формула изобретения Устройство для индикации, содержащее первый и второй формирователи напряжения, входы которых являются входом устч ройства, усилитель, подключенный через преобразователь аналог-код к первому блоку памяти, соединенному с одним из входов блока регулирования чувствительности по координате Y , Другие входы которого подключены к выходам блока регулирования чувствительности по координате X и блока синхронизации, соеди ненного с первым блокои памяти, блоком регулирования чувствительности по координате X и блоком управления перемещением изображения по координате X , вьгход которого подключен к первому вхо ду матричной индикаторной панели, второ вход которой соединен с выходом блока регулирования чувствительности по коор- 56 динате V ,отличающееся тем, что, с целью повьпиения точности устройства, в него введены коммутатор, второй блок памяти, блок задания масштаба по координате у шифратор и блок компараторов, вход которого подключен к выходу второго формирователя Hanpj жения, а выходы блока компараторов ко входам ши4 атора и первым входам коммутатора, вторые входы которого соеданены с выходами первого формирователя напряжения, выход коммутатора соединен со входом усилителя, выход шифратора подключен к первому входу второго блока памяти и входу блока задания масштаба по координате ( , выходы которых соединены со входами блока регулирования чувствительности по координате Y , при этом второй вход второго блока памяти подключен к в.ыхо; блока синхронизации. Источники информации, принятые во внимание.при экспертизе 1,Авторское свидетельство СССР № 373635, клГСЗ 04 F 11/08, 1970. 2.Акцептованная заявка Японии N9 4ё-14482, кл. « Об К 15/ОО, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для отображения информации | 1976 |

|

SU640341A1 |

| Матричный индикатор | 1976 |

|

SU579639A1 |

| Устройство отображения формы электрического сигнала | 1983 |

|

SU1151820A1 |

| Устройство для отображения графической информации на экране газоразрядной индикаторной панели | 1987 |

|

SU1509986A1 |

| СПОСОБ КАЛИБРОВКИ МАТРИЧНОГО ФОТОПРИЕМНИКА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1985 |

|

RU1314800C |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

| Устройство для регистрации однократныхпРОцЕССОВ | 1978 |

|

SU842936A1 |

| Устройство для отображения информации на экране матричной индикаторной панели | 1982 |

|

SU1115090A1 |

| Устройство для отображения графической информации | 1984 |

|

SU1223283A1 |

Авторы

Даты

1980-05-15—Публикация

1978-01-09—Подача