(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Голографическое запоминающее устройство | 1980 |

|

SU888734A1 |

| Устройство для выбора свободных зон в памяти | 1981 |

|

SU980159A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Логическое запоминающее устройство | 1979 |

|

SU790017A1 |

| Устройство для считывания графической информации | 1980 |

|

SU955133A1 |

| Однородный спектро-коррелометр | 1981 |

|

SU970382A1 |

| Устройство для допускового контроля частоты следования импульсов | 1982 |

|

SU1034165A1 |

| Блок управления для доменного запоминающего устройства | 1982 |

|

SU1022217A1 |

| Многовходовый счетчик импульсов | 1976 |

|

SU819970A1 |

;1

Буферное запоминающее устройство относится к автоматике и вычислительной технике И может быть использовано в импульсных И цифровых устройствах.

Известны буферные запоминающие устройства последовательного действия, которые имеют недостаточно высокое быстродействие, так как позволяют производить считывание информации только после окончания записи И не позволяют производить считывание одновременно с записью 1.

Наиболее близким к предложенному является буферное запоминающее устройство, содержащее двоичный счетчик, выход которого через элемент памяти соединен с щиной выходных импулЬсов, щину опроса, соединенную с другим входом Элемента памяти. Шина входных импульсрв и шина вы-ходных импульсов подключены ко входам первого элемента И и через элемент задержки к первым входам соответственно второго И. третьего элементов И. Выход первого элемента И через блок формирования сигнала запрета соединен со вторыми входами второго И третьего элементов И. Выход второго элемента И подключен к суммирующему входу счетчика, а выход третьего элемента И-ко входу узла управления, выход которого подключен к вычитающему входу счетчика 2.,

Недостатками известного буферного запоминающего устройства являются ограниченный частотный диапазон работы устройства И недостаточно высокое быстродейст: вие. Так как двоичный счетчик работает с суммарной частотой двух сигналов - вход10ных сигналов И сигналов опроса, то устройство надежно работает при условии, что сул марная частота не превыщает предельную рабочую частрту счетчика. В связи с ЭТИМ частоты двух сигналов выбирают от-.

is носительно невысокими и, следовательно, быстродействие устройства также недостаточно высоко. Кроме того, данное устройство характеризуется относительно невысокой разрешающей способностью, обусловленной тем, что в некоторых случаях при пере ° крывании входных сигналов и сигналов опроса схема запрета не вырабатывает выходной сигнал, И перекрывающиеся импульсы действуют на счетчик.

Цель изобретения - повышение быстродействия и разрешающей способности устройства.

Поставленная цель достигается тем, что в устройство введены триггер, элементы ИЛИ и НЕ и блок формирования импульсов разностной частоты, один вход которого подключен к выходу накопителя, другой - к первому входу второго элемента И, один выход блока формирования разностной частоты соединен со входом вычитания счетчика, другой - через элемент ИЛИ со входом сложения счетчика и одним из входов триггера, второй вход которого через элемент НЕ соединен с выходом счетчика, выходы триггера подключены ко вторым входам элементов И, выход второго элемента И подключен к соответствующему входу элемента ИЛИ.

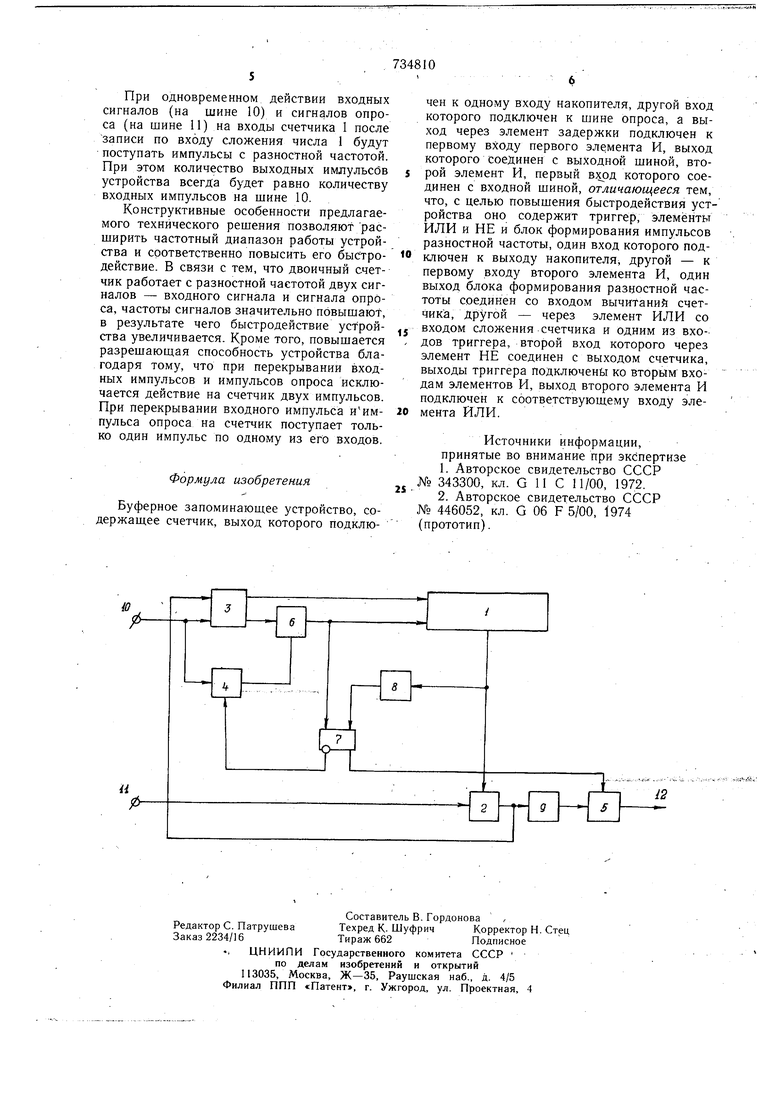

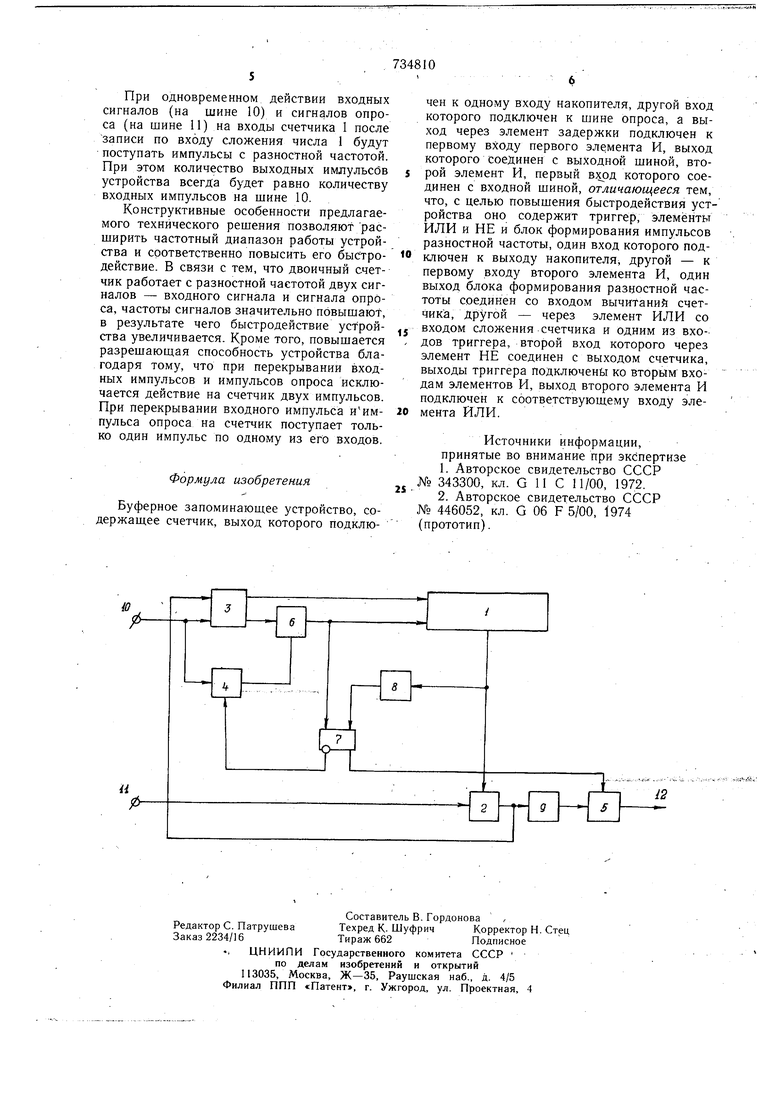

На чертеже приведена блок-схема буферного запоминающего устройства.

Буферное запоминающее устройство содержит счетчик 1, накопитель 2, блок 3 формирования импульсов разностной частоты, элементы 4, 5 И, элемент 6 ИЛИ, триггер 7, элемент 8 НЕ, элемент 9 задержки, щину 10 входных импульсов, щину 11 Опроса, выходную шину 12.

Работает устройство следующим образом

В исходном состоянии счетчик 1 и триггер 7 находятся в нулевом состоянии. Элемент 4 И закрыт по первому входу низким (запрещающим) потенциалом шины 10 входных импульсов и открыт по втором/входу высоким (разрешающим) потенциалом нулевого выхода триггера 7. Элемент 5 И закрыт по обоим входам. Элемент 9 задержки выбран . из расчета, что время задержки (TIAA) равно или больше суммарного времени задержки сигнала на блоке 3 формирования импульсов разностной частоты, на первом разряде счетчика 1, на элементе 8 НЕ и на триггере 7.

Блок 3 формирования импульсов разностной частоты работает таким образом, что на обоих его выходах сигналы отсутствуют, если на первый и на второй входы сигналы поступают поочередно. Если после поступления сигнала на первый вход, на второй вход поступят два и более сигналов подряд.то первым из них блок подготавливается для прохождениясигналов по второму каналу, а второй и последующий сигналы проходят на второй вь1ход устройства. С приходом затем сигнала на первый вход блок подготавливается для прохождения последующих сигналов по первому каналу и т. д.

Входные импульсы (импульсы записи) с щины 10 поступают на первый вход блока 3 формирования импульсов разностной частоты и на первый вход элемента 4 И. Первый импульс подготавливает блок 3 формирования импульсов разностной частоты для прохождения последующих импульсов

по первому каналу (на первый выход) и, открывая элемент 4 И, поступает через элемент 6 ИЛИ на единичный вход триггера 7 и на вход сложения счетчи1 а 1, записывая в него число 1. При этом на выходе счетчика 1 появляется высокий потенциал, в результате чего в накопитель 2 записывается единица. По переднему фронту импульса с выхода элемента 6 ИЛИ устанавливается в единичное состояние триггер 7. При этом высоким потенциалом единичного выхода триггера открывается по второму входу элемент 5 И, низким (запрещающим) потенциа,лом нулевого выхода триггера закрывается по второму входу элемент И 4. Последующие входные импульсы проходят через блок 3 формирования импульсов разностной частоты на ее первый выход и затем через элемент 6 ИЛИ на вход сложения счетчика 1, увеличивая каждый раз его содержимое на единицу.

Импульсы опращивающей частоты, поступающие с шины 11 на вход накопителя 2 вызывают появление импульсов на его выходе до тех пор, пока в накопителе 2 записана единица. Импульсы с выхода накопителя 2 поступают на второй вход блока 3 формирования импульсов разностной частоты и через элемент 9 задержки - на вход элемента 5 И. При этом первьш выходной импульс накопителя 2, поступив на второй вход блока 3 формирования импульсов разностной частоту, не пройдет на второй выход, а только подготовит его для прохождения последующих импульсов. Одновременно первый импульс, задержанный элементом 9 задержки, пройдет через элемент 5 И на выходную шину 12 устройства. Второй импульс с выхода накопителя 2 пройдет через блок 3 формирования импульсов разностной частоты (по второму ка,налу) на вход вычитания счетчика 1, уменьшив на единицу его содержимое, и поступит снова на выход устройства и т. д. N + 1 импульс опращивающей частоты с выхода накопителя 2 (где N - количество входных импульсов, поступающих с щины 10 на вход сложения счетчика 1), пройдя через блок 3 формирования импульсов разностной частоты на вход вычитания счетчика 1, обнуляет его. При этом на выходе счетчика 1 появляется запрещающий потенциал, а на выходе элемента 8 НЕ - соответственно разрещающий потенциал, по переднему фронту которого триггер 7 возвращается в исходное (нулевое) состояние. Запрещающий потенциал единичного выхода триггера 7 закрывает по второму входу элемент 5 И, поэтому N+1 импульс с выхода накопителя 2 задерживается элементом 9 задержки, на выход устройства не пройдет. Таким образом, количество импульсов, поступивщих на выходную щину 12 устройства равно количеству входных импульсов на шине 10.

При одновременном действии входных сигналов (на шине 10) и сигналов опроса (на шине 11) на входы счетчика 1 после записи по входу сложения числа 1 будут поступать импульсы с разностной частотой. При этом количество выходных имлульсбв устройства всегда будет равно количеству входных импульсов на шине 10.

Конструктивные особенности предлагаемого технического решения позволяют расширить частотный диапазон работы устройства и соответственно повысить его быстродействие. В связи с тем, что двоичный счетчик работает с разностной частотой двух сигналов - входного сигнала и сигнала опроса, частоты сигналов значительно повышают, в результате чего быстродействие устройства увеличивается. Кроме того, повышается разрешаюшая способность устройства благодаря тому, что при перекрывании входных импульсов и импульсов опроса исключается действие на счетчик двух импульсов. При перекрывании входного импульса иимпульса опроса на счетчик поступает только один импульс по одному из его входов.

Формула изобретения

Буферное запоминающее устройство, со держашее счетчик, выход которого подключей к одному входу накопителя, другой вход которого подключен к шине опроса, а выход через элемент задержки подключен к первому входу первого элемента И, выход которого соединен с выходной шиной, второй элемент И, первый вход которого соединен с входной шиной, отличающееся тем, что, с целью повышения быстродействия устройства оно содержит триггер, элементы ИЛИ и НЕ и блок формирования импульсов разностной частоты, один вход которого подoключен к выходу накопителя, другой - к первому входу второго элемента И, один выход блока формирования разностной частоты соединен со входом вычитаний счетчика, другой - через элемент ИЛИ со входом сложения счетчика и одним из вхо5дов триггера, второй вход которого через элемент НЕ соединен с выходом счетчика, выходы триггера подключены ко вторым входам элементов И, выход второго элемента И подключен к соответствуюш.ему входу элемента Или.

0

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-05-15—Публикация

1978-01-03—Подача