1

(21)Mi39 51/2k-2b

(22)10.06.88

() 23.0tt.90. Бюл. Г 15 (72) А.Е. Горбель, Н.Ф. Сидоренко, А.Г. Гуз, И.Е. Авраменко и В.Я. Петренко(53) 681.327.6(088.8)

(56)Авторское свидетельство СССР № , кл. G 06 Р 12/00, 1986.

Авторское свидетельство СССР № 1119077, кл. G 11 С 19/00, 198Д.

( ВУ6ЕРНОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57)Изобретение относится к автоматике и вычислительной технике, и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков, работающих по принципу приборов с зарядовой связью, в автоматических системах управления фокусированием изображения в оптических устройствах. Целью изобретения является повышение быстродействия устройства,

повышение достоверности принимаемой информации и обеспечения обращения к устройству асинхронных источника и приемника информации. Буферное оперативное запоминающее устройство содержит два накопителя, мультиплексор, счетчик адреса и триггер. Введение в устройство четырех триггеров, генератора, пяти регистров, двух сумматоров, дешифратора адреса управления, дешифратора адреса выдачи информации, дешифратора выбора информации, блока синхронизации записи, блока контроля записи, блока контроля чтения, блока синхронизации чтения, десяти элементов И, четырех элементов ИЛИ, элемента НЕ и группы из n-элементов НЕ позволит сократить объем передаваемой информации, увеличить объем последующей обработки информации, повысить достоверность принимаемой информации, обеспечить согласование асинхронных источника и приемника информации. 9 ил.

СП СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков, работающих по принципу приборов с зарядовой связью, в автоматических системах управления фокусированием изображения в оптических устройствах. Целью изобретения является повышение быстродействия устройства, повышение достоверности принимаемой информации и обеспечения обращения к устройству асинхронных источника и приемника информации. Буферное оперативное запоминающее устройство содержит два накопителя, мультиплексор, счетчик адреса и триггер. Введение в устройство четырех триггеров, генератора, пяти регистров, двух сумматоров, дешифратора адреса управления, дешифратора адреса выдачи информации, дешифратора выбора информации, блока синхронизации записи, блока контроля записи, блока контроля чтения, блока синхронизации чтения, десяти элементов И, четырех элементов ИЛИ, элемента НЕ и группы из N элементов НЕ позволит сократить объем передаваемой информации, увеличить объем последующей обработки информации, повысить достоверность принимаемой информации, обеспечить согласование асинхронных источника и приемника информации. 9 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков, работающих по принципу приборов с зарядовой связью, в автоматических системах управления фокусированием изображения в оптических устройствах.

Цель изобретения - повышение быстродействия устройства, повышение достоверности принимаемой информации и обеспечения обращения к устройству асинхронных источника и приемника информации.

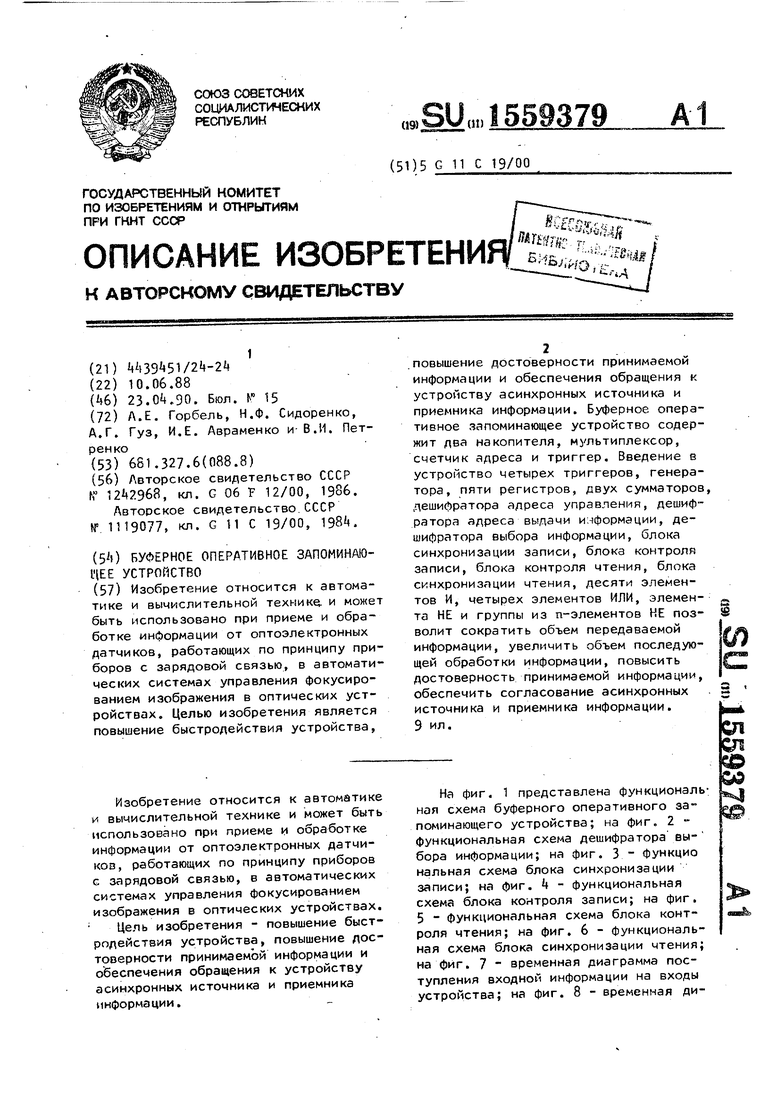

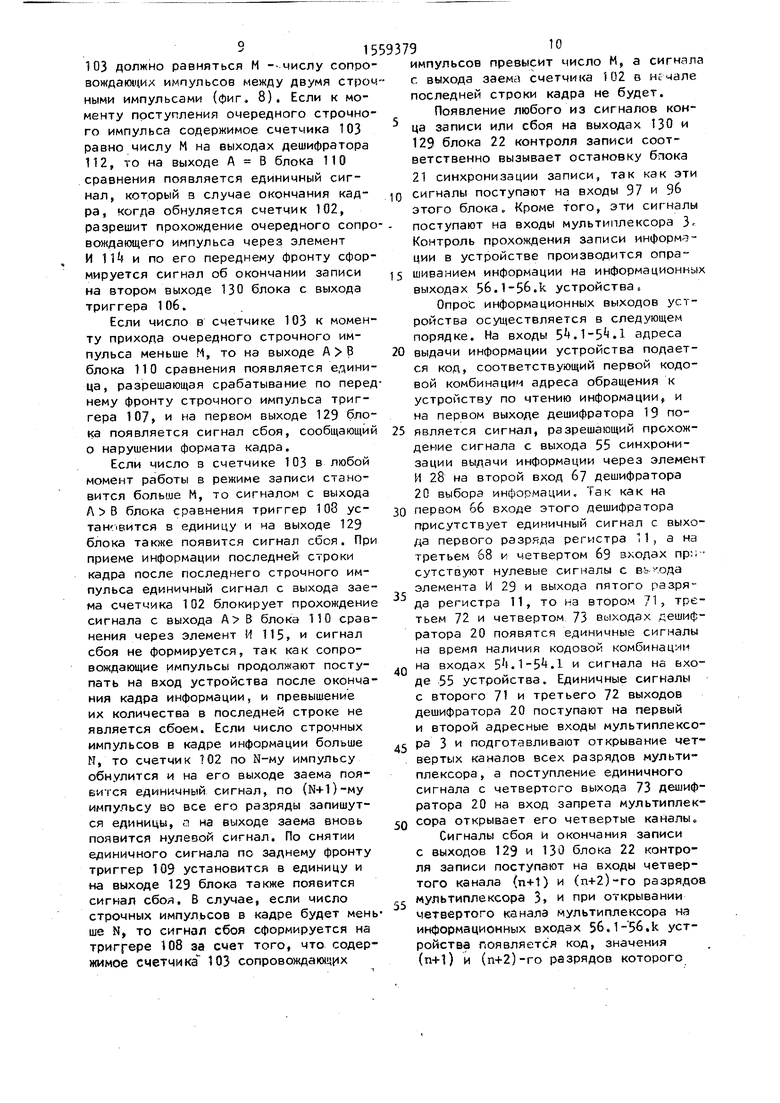

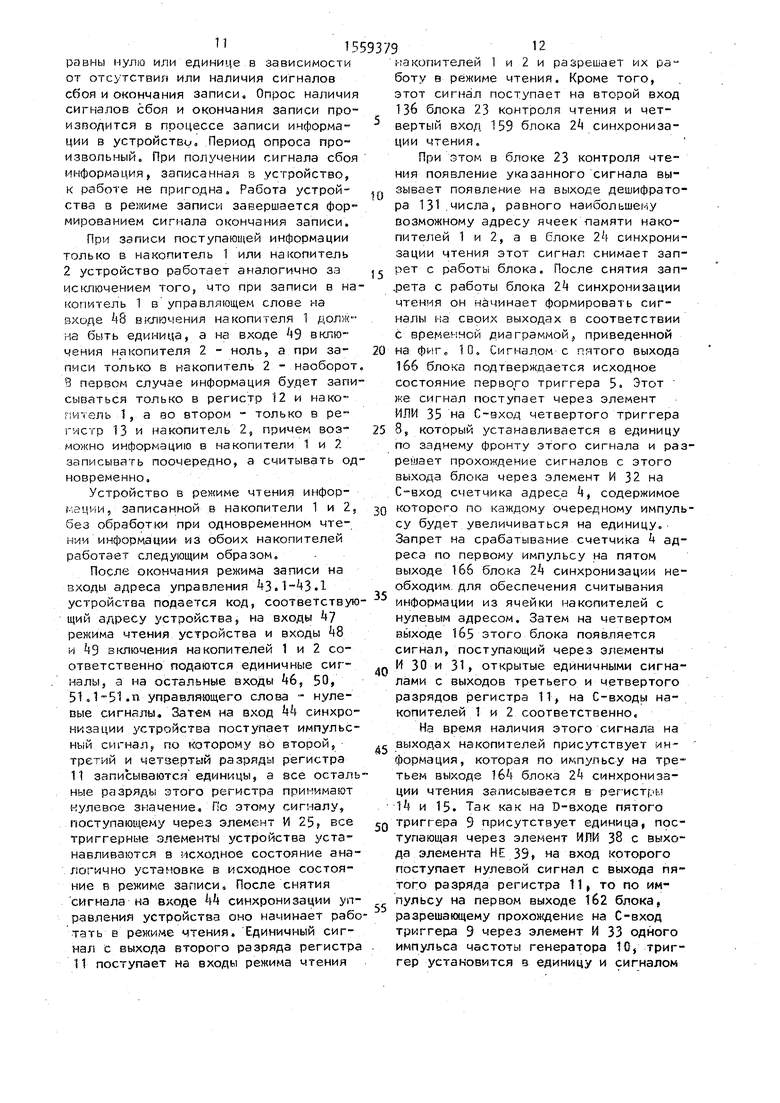

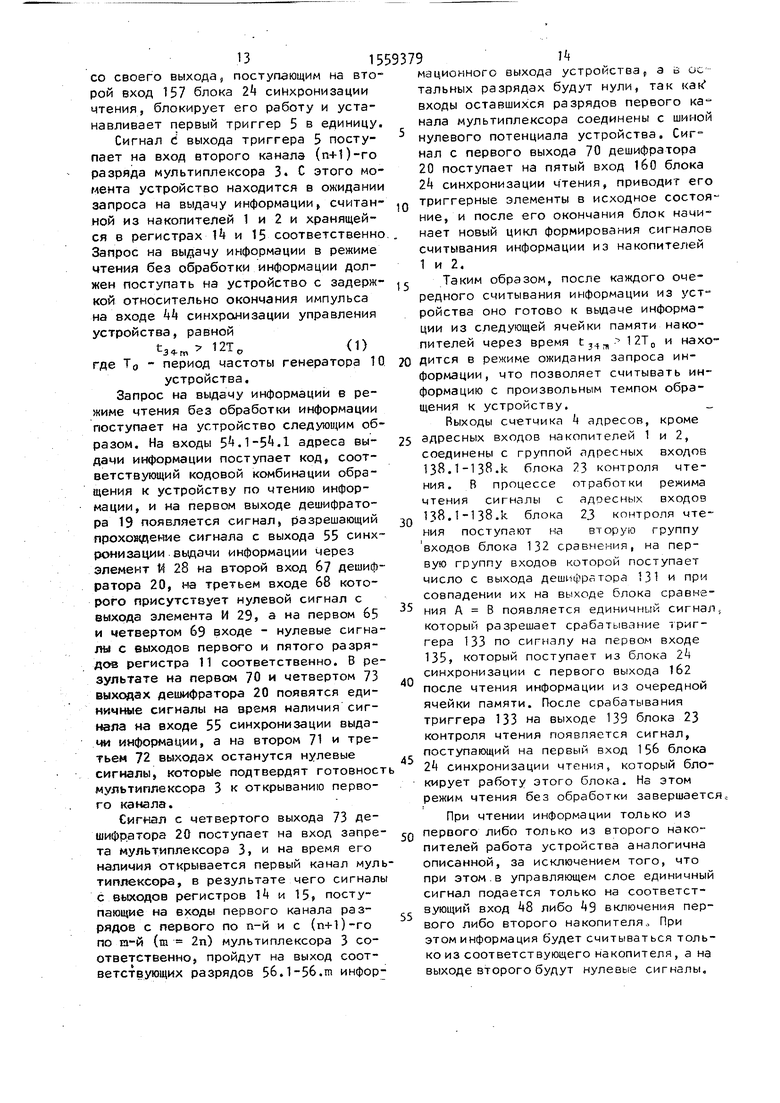

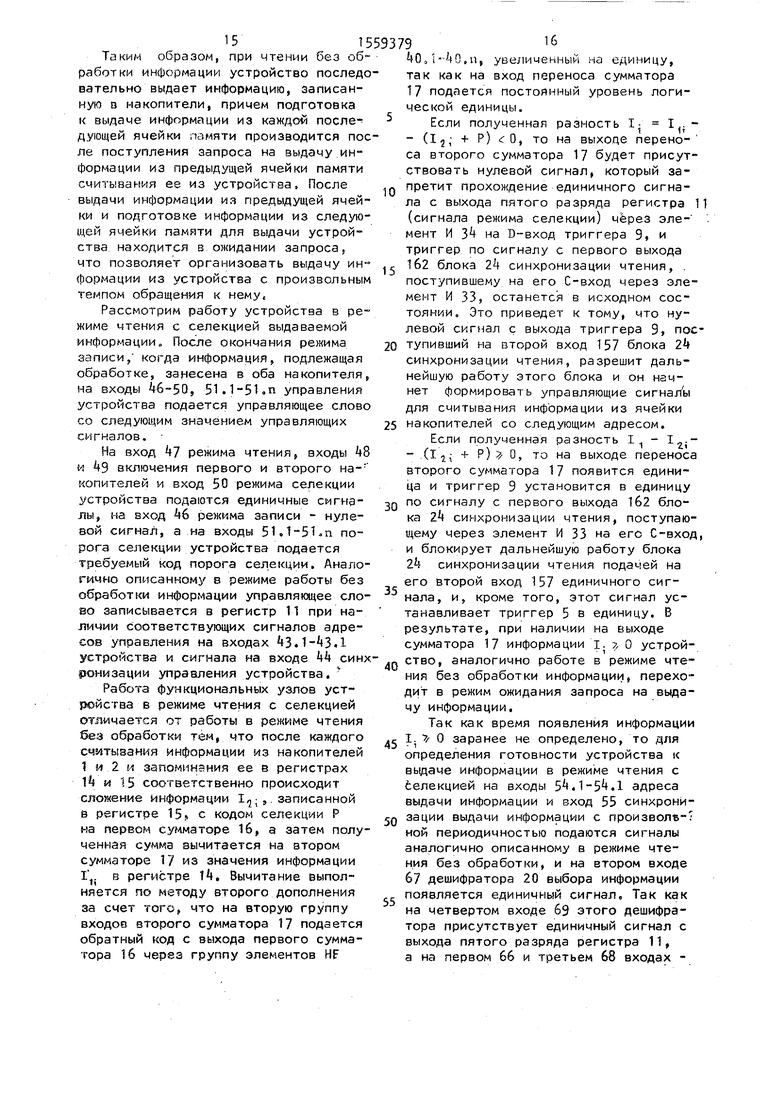

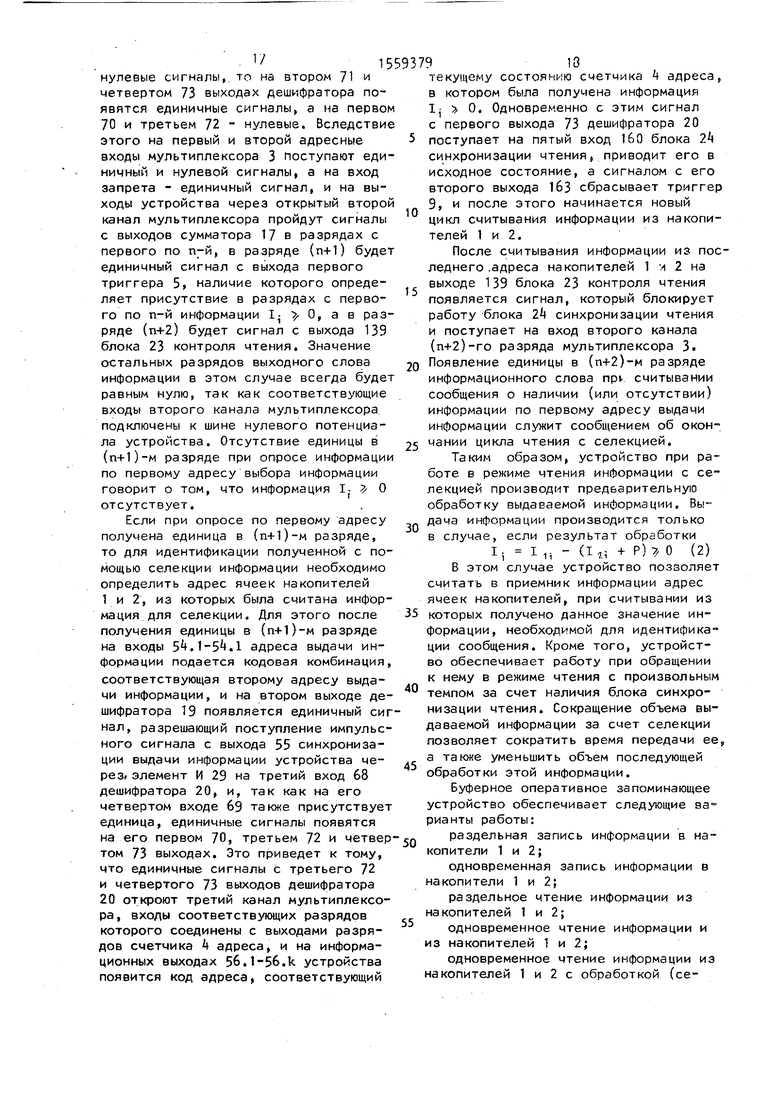

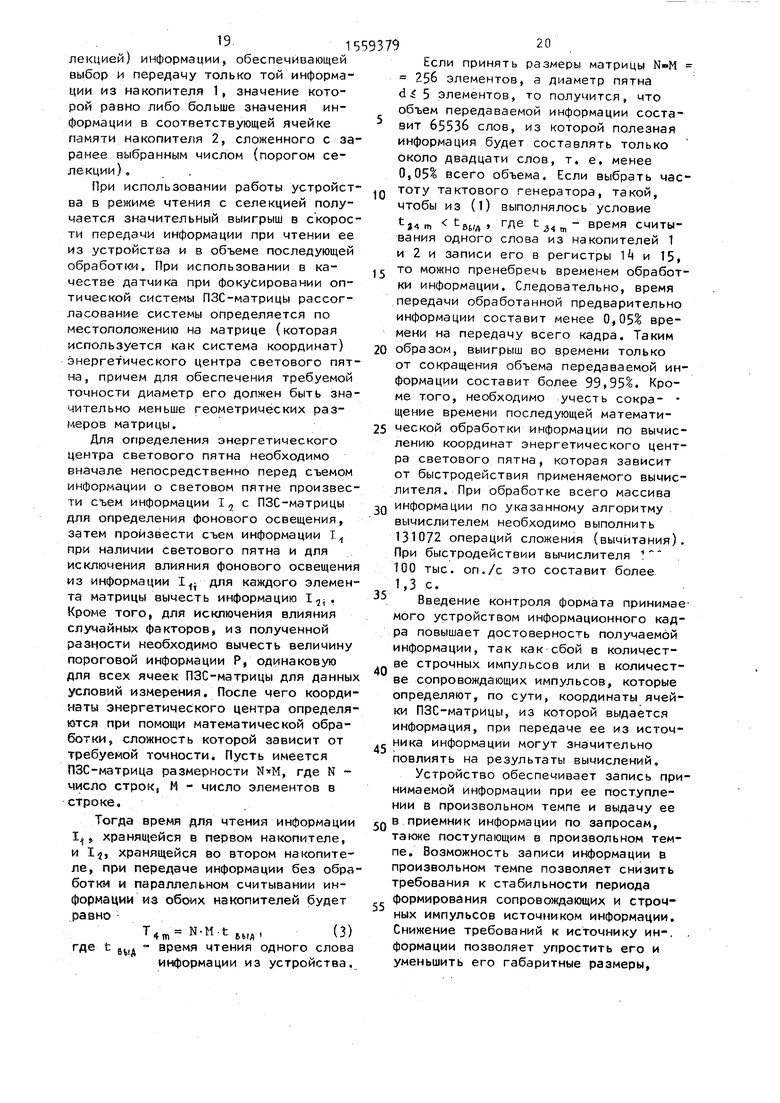

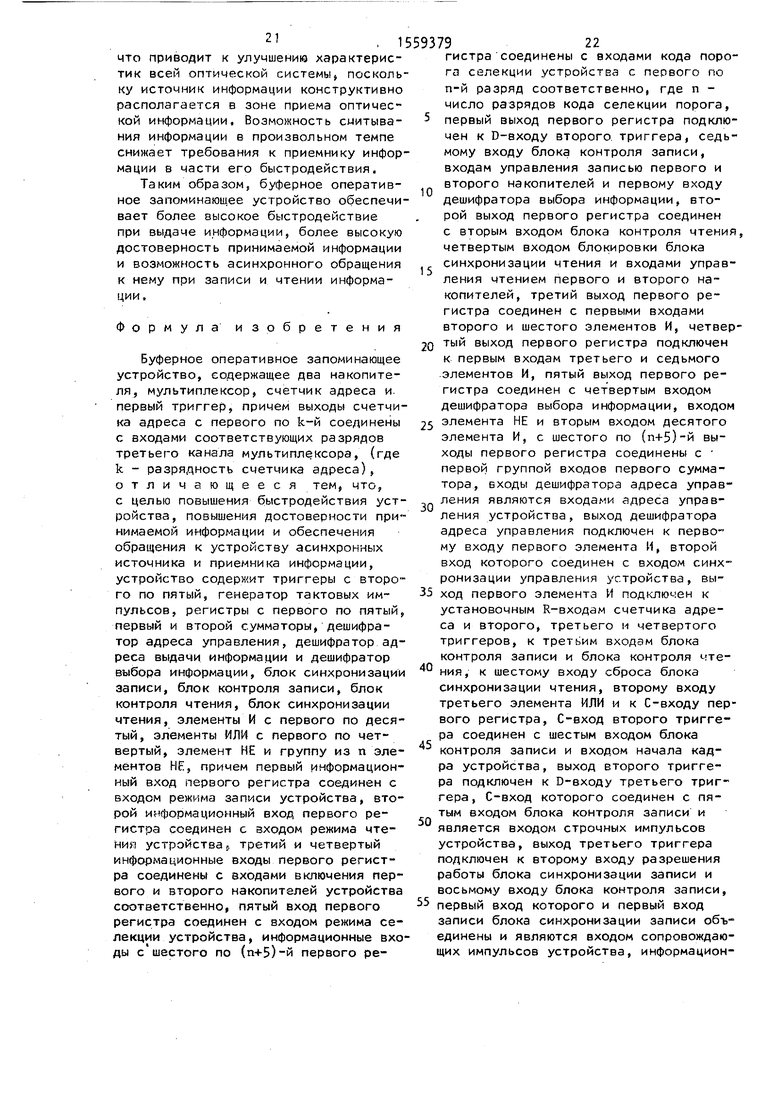

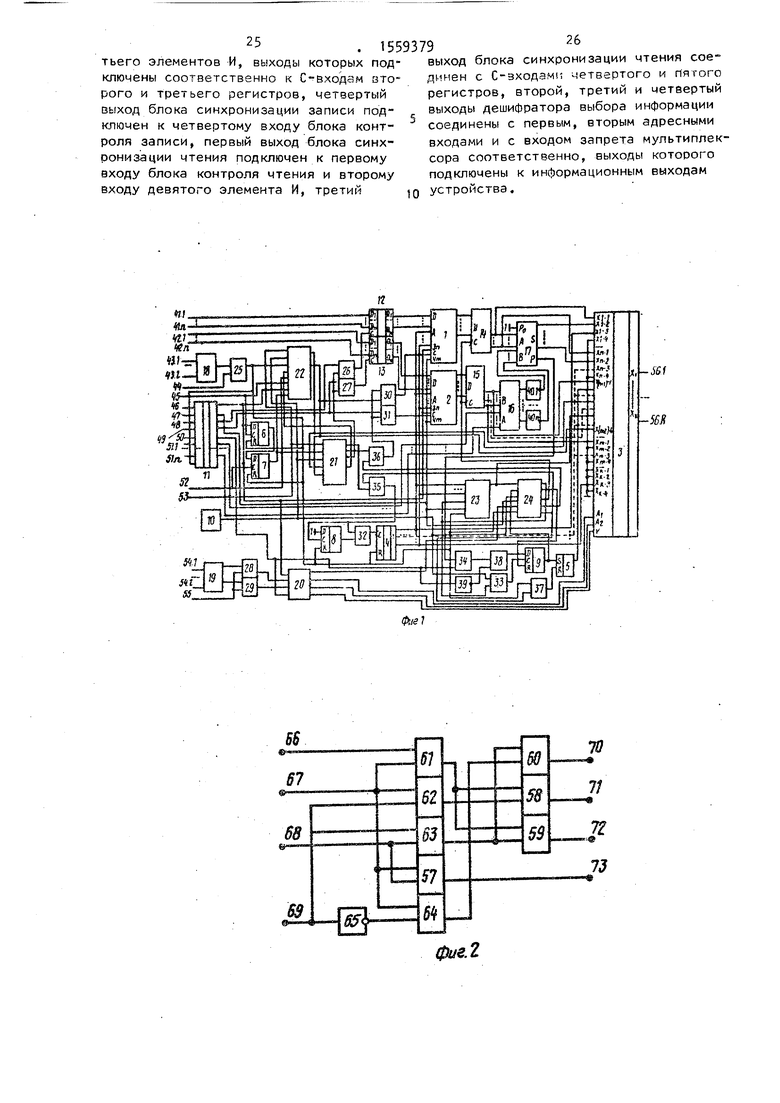

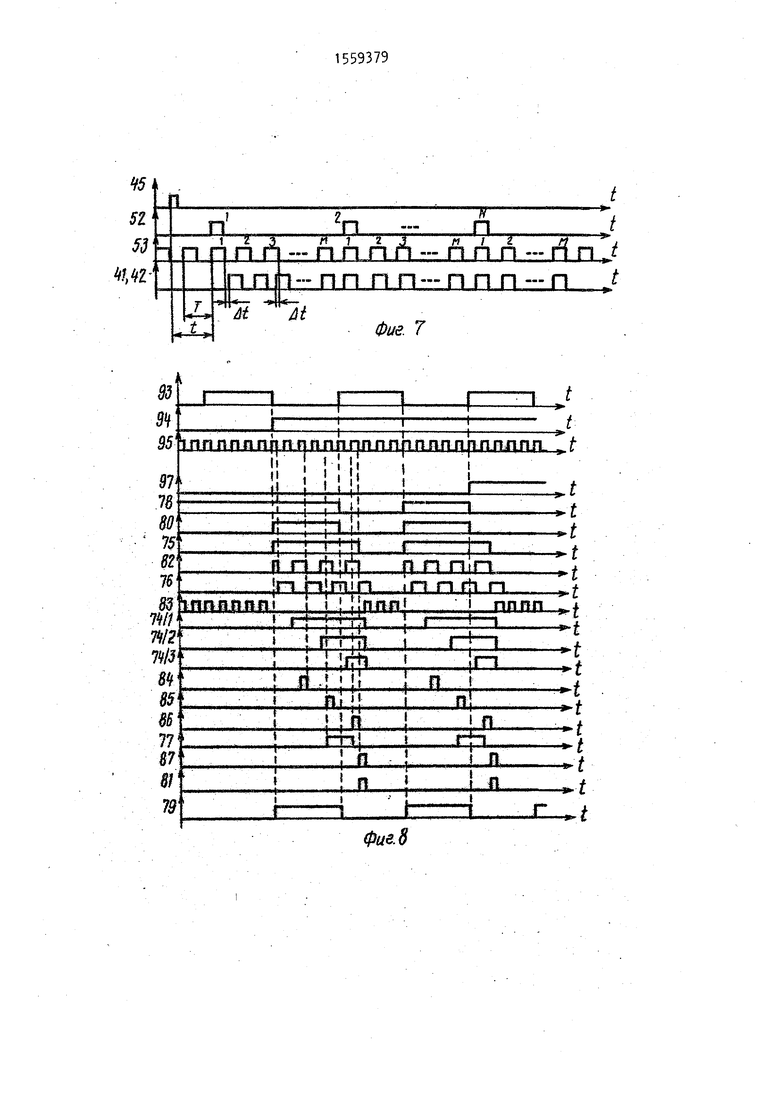

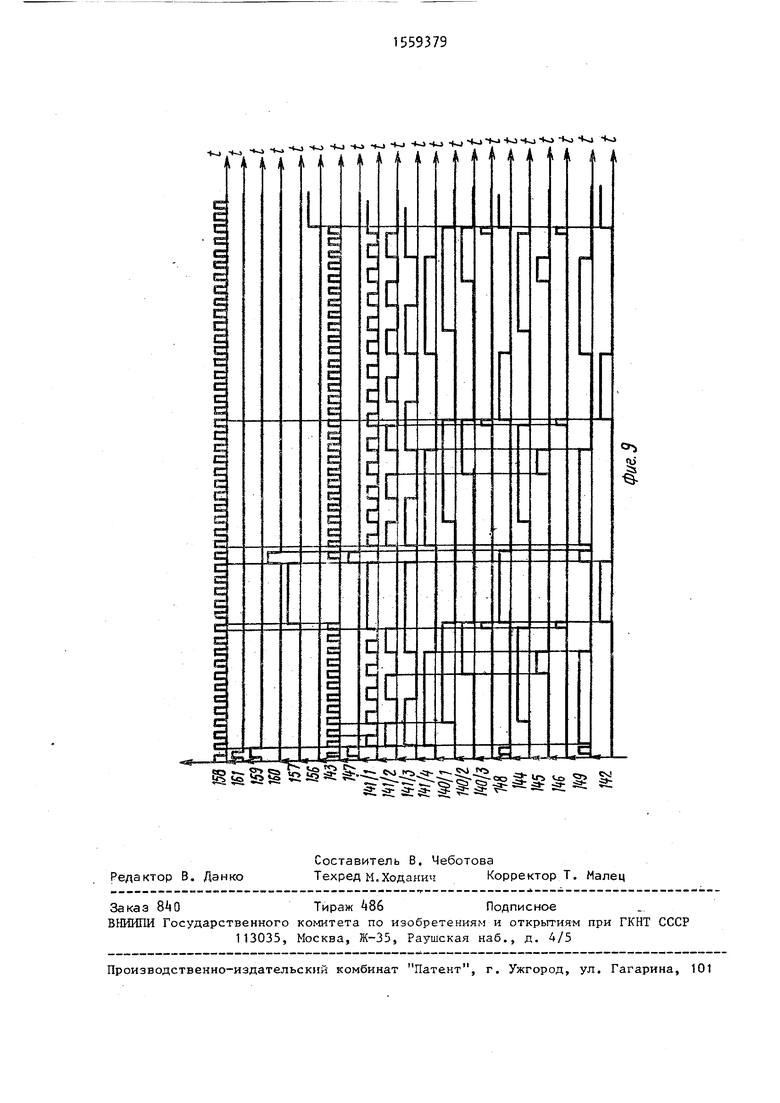

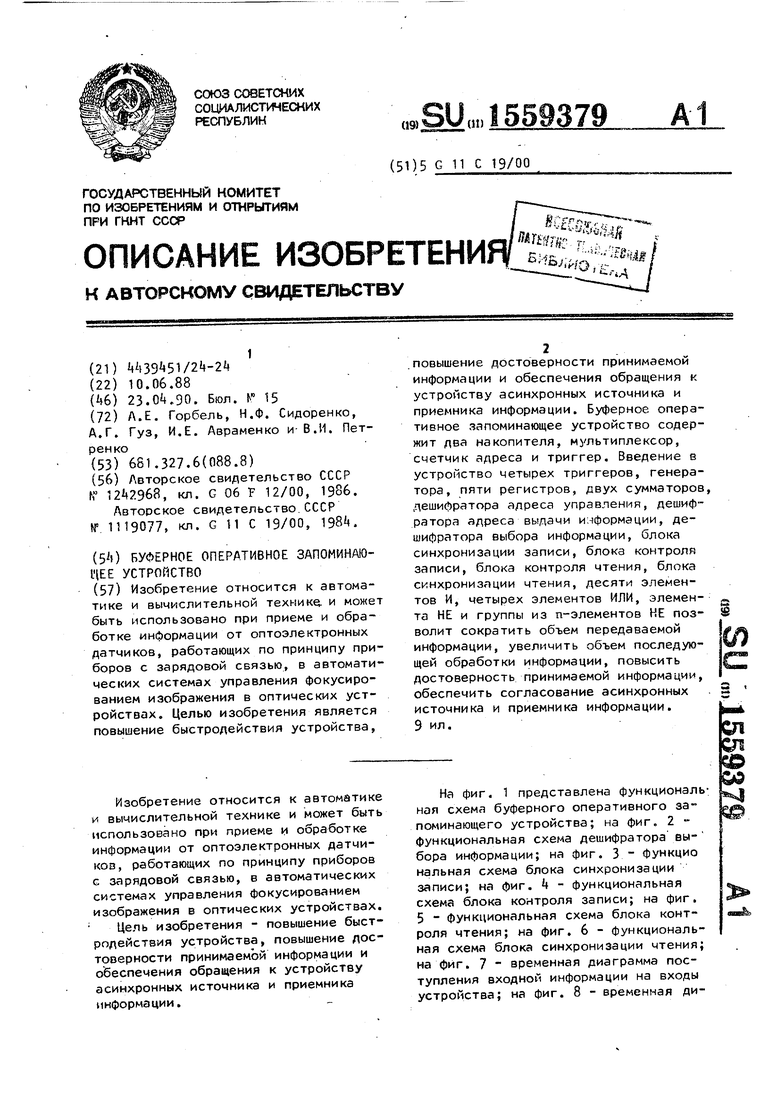

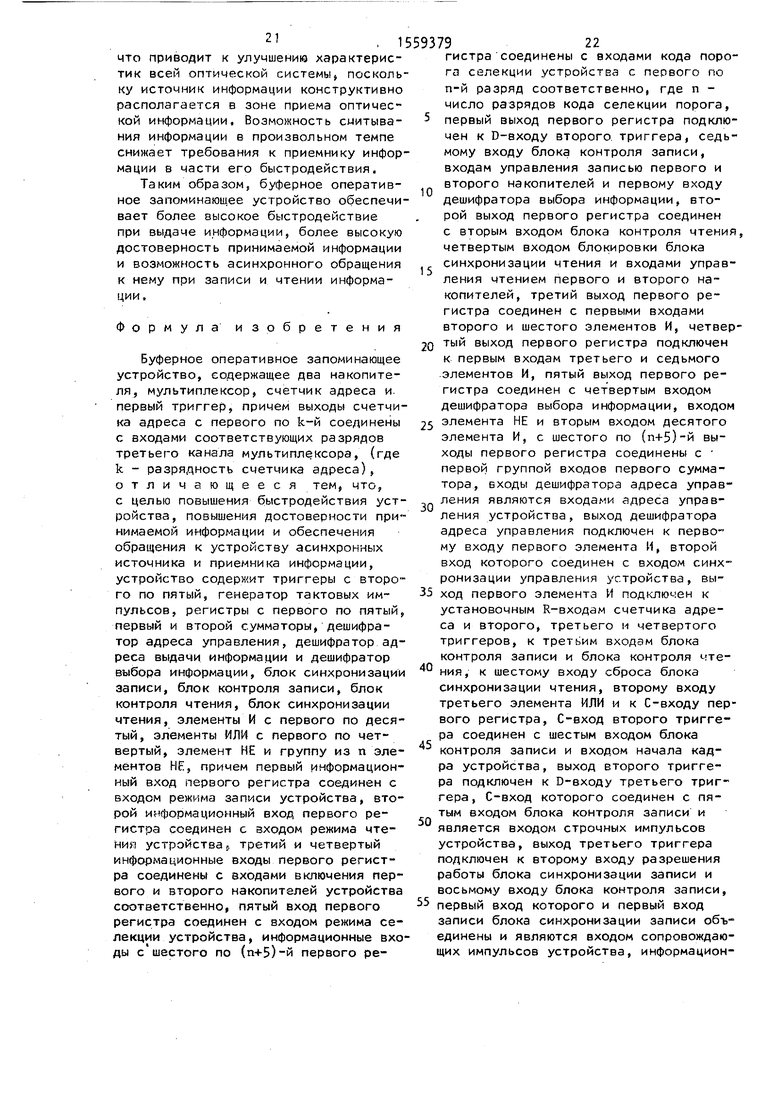

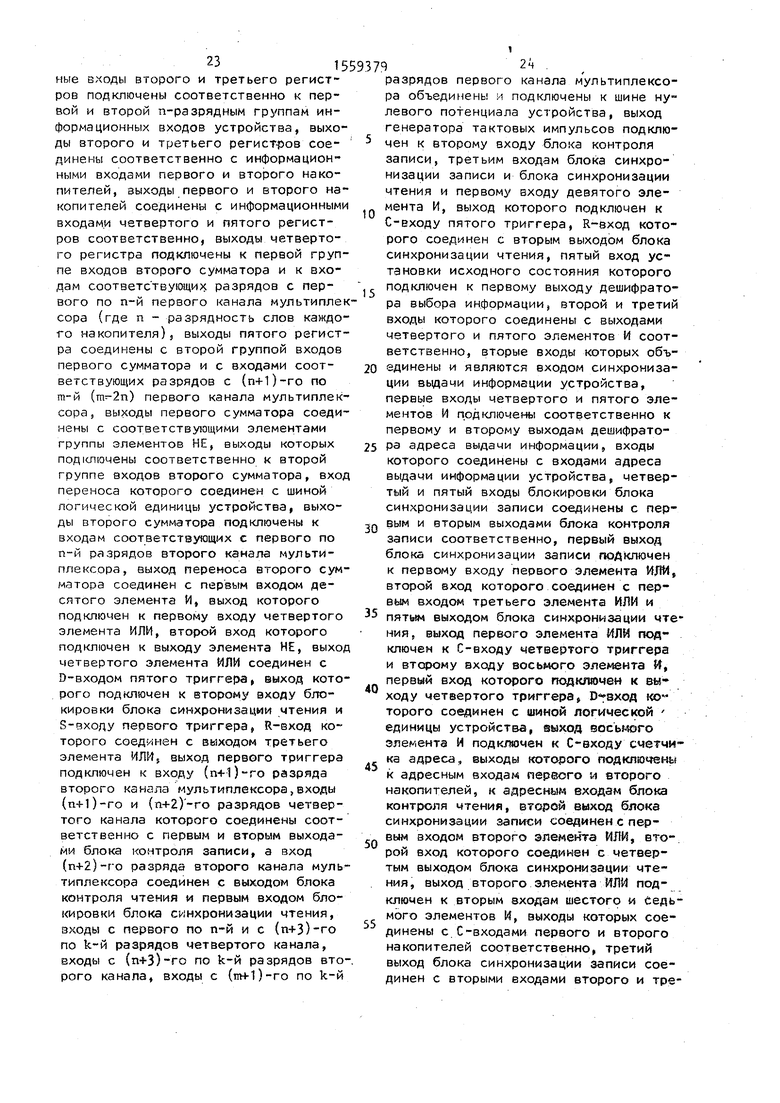

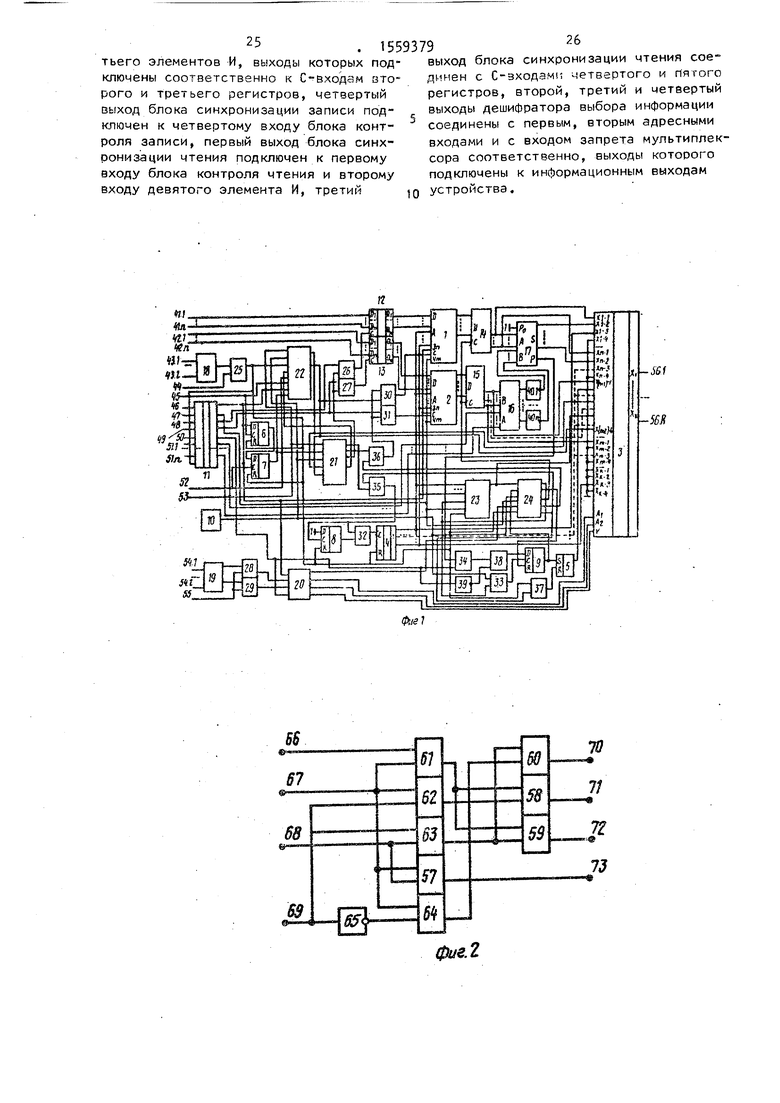

На фиг. 1 представлена функциональная схема буферного оперативного запоминающего устройства; на фиг. 2 - функциональная схема дешифратора выбора информации; на фиг. 3 функцио нальная схема блока синхронизации записи; на фиг. k - функциональная схема блока контроля записи; на фиг. 5 - функциональная схема блока контроля чтения; на фиг. 6 - функциональная схема блока синхронизации чтения; на фиг. 7 - временная диаграмма поступления входной информации на входы устройства; на фиг. 8 - временная диЈЈ

315

аграмма работы блока синхронизации записи; на фиг, 9 - временная диаграмма работы блока синхронизации чтения.

Буферное оперативное запоминающее устройство (фиг. 1) содержит первый 1 и второй 2 накопители, мультиплексор 3, счетчик 4 адреса, первый 5, второй 6, третий J, четвертый 8 и пятый 9 триггеры, генератор 10 тактовых импульсов, пять параллельных регистров 11-15 первый 16 и второй 17 сумматоры, дешифратор 18 адреса управления, дешифратор 19 адреса выда- ми информации, дешифратор 20 выбора информации, блок 21 синхронизации за

20

44 45 № 47 48 и 49

50 51

52 53

30

35

иси, блок 22 контроля записи,чблок 3 контроля чтения, блок 24 синхроизации, чтения, десять элементов И , первый 35, второй 36, третий 7 и четвертый 38 элементы ИЛИ, элеент НЕ 39 и группу п элементов НЕ 0,1-40.п.

На Лиг. 1 приняты следующие услов- 25 ые обозначения:

.n - первая группа информационных входов с пер- вого по n-й разряд соответственно;вторая группа информационных входов с первого по n-й разряд соответственно; входы адреса управления устройства с первого по 1-й разряд соответственно; вход синхронизации управления устройства; вход импульса начала кадра устройства; вход режима записи устройства ;

вход режима чтения устройства;

входы включения первого и второго накопителей соответственно;

-вход режима селекции устройства;

1-51,п - входы с первого по

n-й разряд соответственно кода порога селекции устройства;

-вход строчных импульсов устройства;

-вход сопровождающих импульсов устройства;

40

45

50

55

o

5

0

0

5

5

40

45

50

55

входы адреса выдачи информации устройства с первого по 1-й разряд соответственно;

55- вход синхронизации выдачи информации устройства;

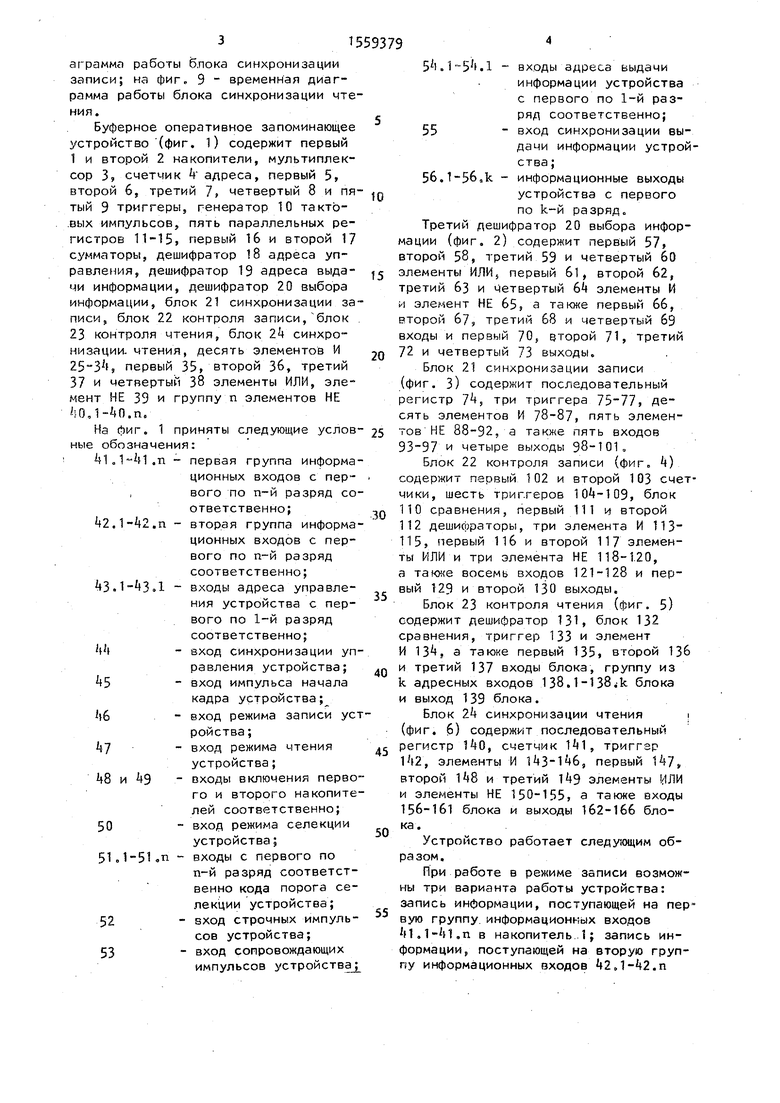

Третий дешифратор 20 выбора информации (фиг. 2) содержит первый 57 второй 58, третий 59 и четвертый 60 элементы ИЛИ, первый 61, второй 62, третий 63 и четвертый 6k элементы И и элемент НЕ 65, а также первый 66, второй 67, третий 68 и четвертый 69 входы и первый 70, второй 71, третий 72 и четвертый 73 выходы.

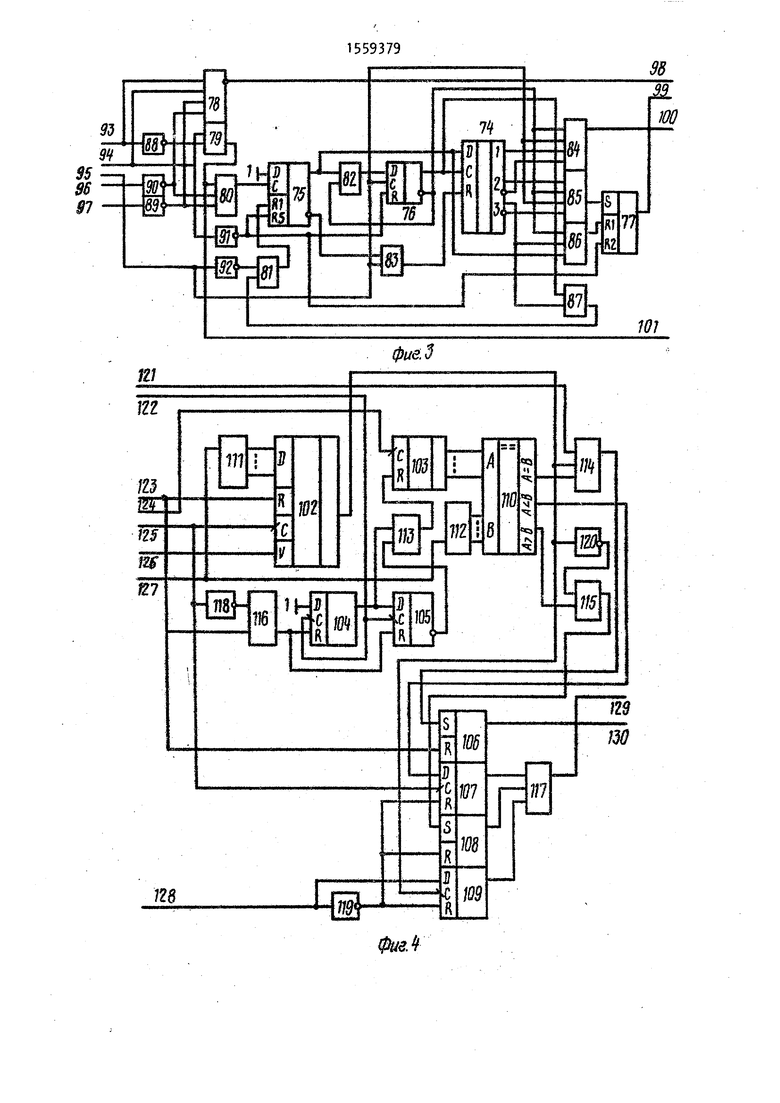

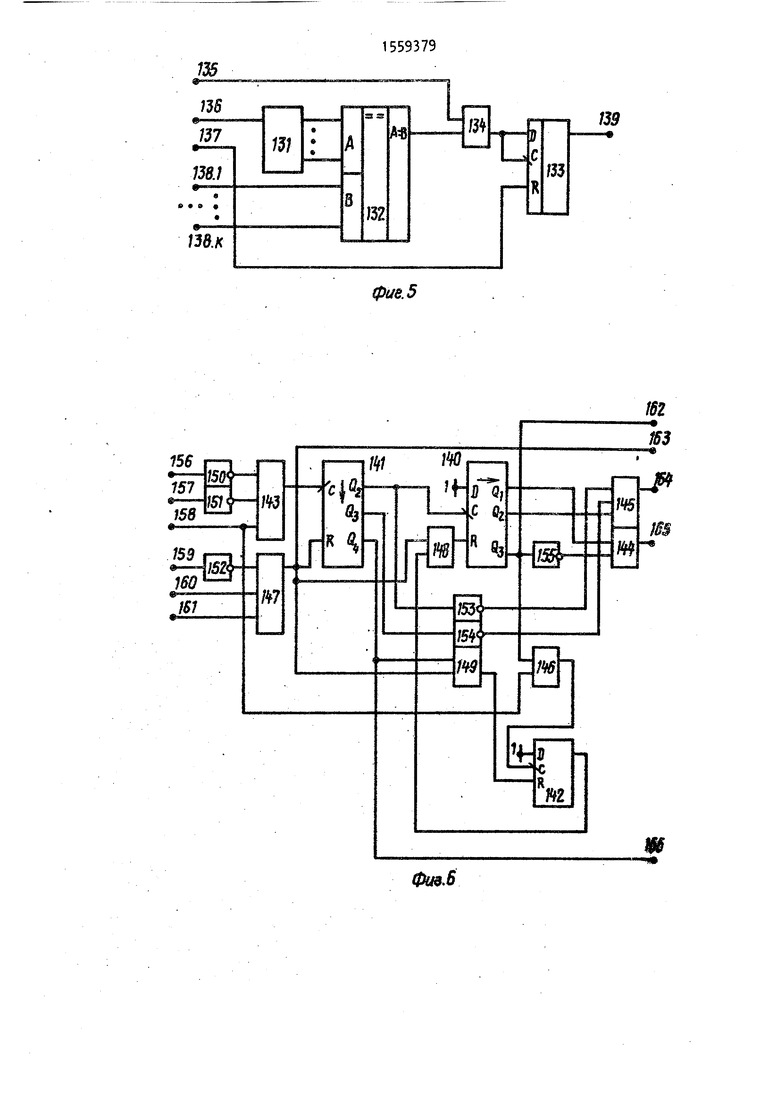

Блок 21 синхронизации записи (фиг. 3) содержит последовательный регистр 74, три триггера , десять элементов И 78-87, пять элементов НЕ 88-92, а также пять входов и четыре выходы 98-101,

Блок 22 контроля записи (фиг. Ц) содержит первый 102 и второй 103 счетчики, шесть триггеров 104-109, блок 110 сравнения, первый 111 и второй 112 дешифраторы, три элемента И 113 115, первый 116 и второй 117 элементы ИЛИ и три элемента НЕ 118-120, а также восемь входов 121-128 и первый 129 и второй 130 выходы.

Блок 23 контроля чтения (фиг. 5) содержит дешифратор 131, блок 132 сравнения, триггер 133 и элемент И 134, а также первый 135, второй 136 и третий 137 входы блока, группу из k адресных входов 138.1-138.-k блока и выход 139 блока.

Блок 2k синхронизации чтения i (фиг. 6) содержит последовательный регистр 140, счетчик 141, триггер 142, элементы И 143-146, первый 147 второй 148 и третий 149 элементы ИЛИ и элементы НЕ 150-155, а также входы 156-161 блока и выходы 162-166 блока .

Устройство работает следующим образом.

При работе в режиме записи возможны три варианта работы устройства: запись информации, поступающей на первую группу информационных входов 41.1-41.П в накопитель 1; запись информации, поступающей на вторую группу информационных входов 42.1-42.П

51

в накопитель 2; одновременная запись информации, поступающей на первую 41..п и вторую 2..п группы информационных входов в накопители 1 и 2 соответственно.

При работе в режиме чтения возмож ны два варианта работы устройства: одновременная либо раздельная выдача содержимого накопителей 1 и 2; выдача информации из накопителей 1 и 2 с предварительной обработкой (селекцией) информации.

Обработка информации заключается в том, что к содержимому каждой ячей ки накопителя 2 (ij,) прибавляется значение кода порога селекции Р, постоянного для данного цикла чтения, и затем указанная сумма вычитается из значения соответствующей ячейки накопителя 1 (1).

В случае, если значение результата обработки информации

ii

- (1Г, + Р) } О,

то указанный результат выдается на выход устройства с указанием адреса ячеек накопителей 1 и 2, для которых он получен.

Если же значение выражения

и

- (I г, + Р) 0,

то результат не выдается, и устройство проводит считывание информации из ячеек со следующим адресом.

Рассмотрим работу устройства в ое- жиме записи информации в накопители 1 и 2 с первой А1.1-А1.П и второй А2.1-А2.П групп информационных входов соответственно.

После подачи напряжения питания на устройство начинает работать генератор 10 тактовых импульсов, а на входы устройства поступают сигналы в следующем порядке.

На входы A3.1-A3 Л адреса управления поступает код, соответствующий адресу данного устройства. При совпадении данного кода с кодом адреса устройства на выходе первого дешифратора 18 появляется единичный си|- нал. Затем на входы А6-50, 51.1-51.п управления устройства одновременно поступают сигналы управляющего слова: на вход А6 режима записи устройства, входы A3 и 9 включения первого и второго накопителей поступают единичные сигналы; на вход А 7 режима чтения, вход 50 режима селекции устройства и входы 51.1-51.П кода порога селекции устройства поступают нулевые сигналы.

10

593796

После этого на вход АА синхрониза- ции управления устройства поступает импульсный сигнал, который через первый элемент И 25, открытый единичным сигналом с выхода дешифратора 18, поступает на С-вход первого параллельного регистра 11 и записывает управляющее слово, поступившее на входы А6-50, 51..п управления устройства в соответствующие разряды с пер- вого по n-й этого регистра. Этот же сигнал с выхода элемента И 25 поступает на установочные R-входы счетчика J5 Ц адреса, второго 6, третьего 7 и четвертого 8 триггеров и устанавливает их в исходное состояние, а через третий элемент И 37 поступает на R-вход первого триггера 5 и также ус- 20 танавливает его в исходное состояние. Кроме того, этот же сигнал поступает на третий вход 123 блока 22 контроля записи, третий вход 137 блока 23 контроля чтения и шестой вход 161 бло- 25 ка 2k синхронизации чтения и сбрасывает входящие в состав этих блоков триггерные устройства.

Блок 21 синхронизации записи приводится в исходное состояние нулевым 3Q сигналом с выхода третьего триггера 7, поступающим на второй вход 9А этого блока, а пятый триггер 9 сбрасыва- ется сигналом с второго выхода 1бЗ блока 2 синхронизации чтения Нулевым сигналом с выхода третьего тригге 35 ра 7, поступающим на восьмой вход 128 блока 22 контроля записи, сбрасываются четвертый 107, пятый 108 и шестой 109 триггеры этого блока.

Состояние второго 12, третьего 13, четвертого 1А и пятого 15 параллельных регистров в момент включения на работу устройства не влияет. Кроме того, одновременно с подачей питания на устройство на его вход 53 сопровождающих тактовых импульсов начинают поступать импульсы. После записи управляющего слова в регистр 11 единичный сигнал с выхода первого разряда регистра поступает на D-вход втооого триггера 6, седьмой вход 127 блока 22 контроля записи, первый 66 вход третьего дешифратора выбора информации и входы записи первого 1 и второго 2 накопителей и подготавливает их к работе в режиме записи.

Единичные сигналы с выходов третьего и четвертого разрядов первого регистра 11 поступают на один из вхо40

45

50

55

дов второго 26, шестого 30, и третьего 27 и седьмого 31 элементов И соответственно. Нулевой сигнал с выхода второго разряда первого регистра 11 поступает на второй 136 вход блока 23 контроля чтения и четвертый 159 f вход блока 21 синхронизации чтения. Этим сигналом блокируется работа указанных блоков. Нулевой сигнал с выхода пятого разряда первого регист- ра 11 поступает на четвертый вход 69 дешифратора выбора информации, а нулевые сигналы с остальных разрядов этого регистра поступают на первую группу входов первого сумматора 16. После записи командного слова в регистр 11 устройство готово к работе в режиме записи информации и нахо-ч дится в режиме ожидания поступления импульса начала кадра. По заднему фронту этого импульса поступающего на вход 5 начала кадра устройства, триггер 6 устанавливается в единицу и разрешает срабатывание триггера 7 по первому строчному импульсу, поступающему на вход 52 строчных импульсов устройства, который, в свою очередь, разрешает работу блока 21 синхронизации записи и блока 22 контроля записи единичным сигналом, поступающим на второй 9 и восьмой 128 входы блоков соответственно.

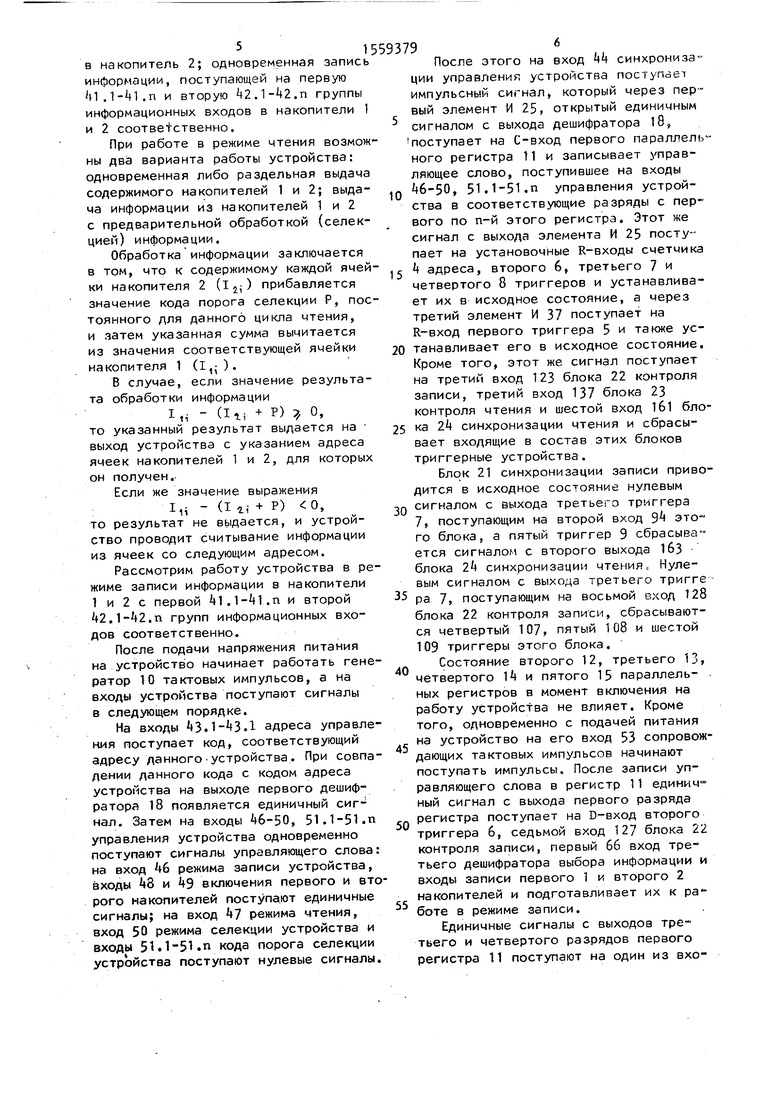

В блоке 22 контроля записи по импульсу начала кадра, поступающему на шестой вход 126 блока в счетчик 102 записывается число N, определяющее заданное количество строчных импульсов в кадре, а по каждому строчному импульсу содержимое этого счетчика уменьшается на единицу. Первый сопровождающий импульс, совпадающий с первым строчным импульсом (см, временную диаграмму на фиг, 8), поступает на первый вход 93 блока 21 синхронизации чтения, и по его окончанию появляется разрешение на работу блока с выхода триггера 7 по заднему фронту строчного импульса. В паузе между сопровождающими импульсами (фиг. 9) блок 21 синхронизации записи запускается и отрабатывает один цикл формирования выходных сигналов. По заднему фронту сигнала на первом выходе 98 блока 21 синхронизации записи триггер 8 установится в единицу и разрешит прохождение этих сигналов в последующих циклах записи через элемент И 32 на счетный С-вход счет

0

5

0

5

0

5

0

5

чика k адреса для перевода адреса записи. Это необходимо для исключения переключения счетчика k адреса до записи информации в ячейку с нулевым адресом, так как перевод счетчика осуществляется после записи информации в накопители 1 и 7.

Запись информации в накопители 1 и 2 осуществляется следующим образом.

Импульсом с третьего выхода 100 блока 21 синхронизации записи, поступающим через открытые элементы И 26 и 27 на С-входы регистров 12 и 13 соответственно, информация первой группы П..п информационных входов записывается в регистр 12, ас второй группы k2.-k2,n - в регистр 13 а затем импульсом с второго выхода 99 этого же блока, поступающим через открытые элементы И 30 и 31 на С-входы накопителей 1 и 2, информация из регистров 12 и 23 переписывается в накопители 1 и 2.

Промежуточное запоминание информации в регистрах 12 и 13 используется для того, чтобы иметь возможность записывать информацию в накопители после ее снятия с входов устройства до поступления следующей информации, так как запись в регистры осуществляется быстрее, чем а накопители, требующие для организации записи в них информации строгого соблюдения минимально- допустимых временных интервалов между подачей сигналов адреса, записи и стробирующего импульса. Наличие блока синхронизации записи позволяет записывать информацию, поступающую в произвольном темпе. В дальнейшем по каждому сопровождающему импульсу блок 21 синхронизации формирует указанную последовательность сигналов, и в накопители 1 и 2 производится запись .информации в ячейки памяти с адресами, формируемыми счетчиком k адреса.

При записи информации в накопители 1 и 2 блок 22 контроля записи производит контроль формата кадра информации. По каждому строчному импульсу, поступающему на пятый вход 125 блока, содержимое счетчика 102 уменьшается нэ единицу, а по каждому импульсу на четвертом входе 12, поступающему с четвертого выхода 10 блока 21 синхронизации записи, содержимое счетчика 103 увеличивается на единицу, и к моменту поступления очередного строчного импульса содержимое счетчика

103 должно равняться М - числу сопровождающих импульсов между двумя стройными импульсами (фиг. 8). Если к моменту поступления очередного строчного импульса содержимое счетчика 103 равно числу М на выходах дешифратора 112, то на выходе А В блока 110 сравнения появляется единичный сигнал, который в случае окончания кадра, когда обнуляется счетчик 102, разрешит прохождение очередного сопро вождащего импульса через элемент И 11 и по его переднему фронту сформируется сигнал об окончании записи на втором выходе 130 блока с выхода триггера 106.

Если число в счетчике 103 к моменту прихода очередного строчного импульса меньше М, то на выходе блока 110 сравнения появляется единица, разрешающая срабатывание по перед нему фронту строчного импульса триггера 107, и на первом выходе 129 блока появляется сигнал сбоя, сообщающий о нарушении формата кадра.

Если число в счетчике 103 в любой момент работы в режиме записи становится больше М, то сигналом с выхода блока сравнения триггер 108 ус- тан вится в единицу и на выходе 129 блока также появится сигнал сбоя. При приеме информации последней строки кадра после последнего строчного импульса единичный сигнал с выхода зае- ма счетчика 102 блокирует прохождение сигнала с выхода А В блока 110 сравнения через элемент И 115, и сигнал сбоя не формируется, так как сопровождающие импульсы продолжают поступать на вход устройства после окончания кадра информации, и превышение их количества в последней строке не является сбоем. Если число строчных импульсов в кадре информации больше N, то счетчик 02 по N-му импульсу обнулится и на его выходе заема поя- ьи(ся единичный сигнал, по (К+1)-му импупьсу во все его разряды запишутся единицы, л на выходе заема вновь появится нулевой сигнал. По снятии единичного сигнала по заднему фронту триггер 109 установится в единицу и «а выходе 129 блока также появится сигнал сбоя. В случае, если число строчных импульсов в кадре будет меньше N, то сигнал сбоя сформируется на тригрере 108 за счет того, что содержимое счетчика 103 сопровождающих

1559379

10

импульсов превысит число М, а сигнала г выхода заема счетчика 102 в н. чале последней строки кадра не будет.

Появление любого из сигналов конца записи или сбоя на выходах 130 и 129 блока 22 контроля записи соответственно вызывает остановку блока 21 синхронизации записи, так как эти сигналы поступают на входы 97 и 96 этого блока. Кроме того, эти сигналы поступают на входы мультиплексора 3 Контроль прохождения записи информации в устройстве производится опрашиванием информации на информационных выходах 56.1-56.k устройстваs

Опрос информационных выходов устройства осуществляется в следующем порядке. На входы 5. адреса

выдачи информации устройства подается код, соответствующий первой кодовой комбинации адреса обращения к устройству по чтению информации и на первом выходе дешифратора 19 появляется сигнал, разрешающий прохождение сигнала с выхода 55 синхронизации выдачи информации через элемент И 28 на второй вход 67 дешифратора 20 выбора информации. Так как на

первом об входе этого дешифратора

присутствует единичный сигнал с выхода первого разряда регистра 11, а на третьем 68 v четвертом 69 входах пр - сутствуют нулевые сигналы с в- -ода элемента И 29 и выхода пятого разряда регистра 11, то на втором 71 тре

0

тьем 72 и четвертом 73 выходах дешифратора 20 появятся единичные сигналы на время наличия кодовой комбинации на входах 5.1-5.1 и сигнала на входе 55 устройства. Единичные сигналы с второго 71 и третьего 72 выходов дешифратора 20 поступают на первый и второй адресные входы мультиплексо- 5 Ра 3 и подготавливают открывание четвертых каналов всех разрядов мультиплексора , а поступление единичного сигнала с четвертого выхода 73 дешифратора 20 на вход запрета мультиплексора открывает его четвертые каналы

Сигналы сбоя и окончания записи с выходов 129 и 130 блока 22 контроля записи поступают на входы четвертого канала (п+1) и (п+2)-го разрядов мультиплексора 3 и при открывании четвертого канала мультиплексора на информационных входах 5&.1-56.k устройства появляется код, значения (п+1) и (п+2)-го разрядов которого

0

5

равны нулю или единице в зависимости от отсутствия или наличия сигналов сбоя и окончания записи. Опрос наличия сигналов сбоя и окончания записи производится в процессе записи информации в устройство, Период опроса про- извопьный. При получении сигнала сбоя информация, записанная в устройство, к работе не пригодна Работа устройства в режиме записи завершается формированием сигнала окончания записи. При записи поступающей информации только в накопитель 1 или накопитель 2 устройство работает аналогично за исключением того, что при записи в накопитель 1 в управляющем слове на входе 48 включения накопителя 1 должна быть единица, а на входе 49 включения накопителя 2 - ноль, а при записи только в накопитель 2 - наоборот В первом случае информация будет записываться только в регистр 12 и накопитель 1, а ао втором - только в регистр 13 и накопитель 2, причем возможно информацию в накопители 1 и 2 записывать поочередно, а считывать одновременно.

Устройство в режиме чтения информации, записанной в накопители 1 и 2, без обработки при одновременном чтении информации- из обоих накопителей работает следующим образом.

После окончания режима записи на входы адреса управления 43.1-43.1 устройства подается код, соответствующий адресу устройства, на входы 47 режима чтения устройства и входы 48 и 49 включения накопителей 1 и 2 соответственно подаются единичные сигналы, а на остальные входы 46, 50, 51.1-51.П управляющего слова - нулевые сигналы. Затем на вход 44 синхронизации устройства поступает импульсный сигналу по которому во второй, третий и четвертый разряды регистра И записываются единицы, а все остальные разряды зтого регистра принимают кулевое значение. По этому сигналу, поступающему через элемент Я 25, все триггерные элементы устройства устанавливаются в исходное состояние аналогично установке в исходное состояние в режиме записи После снятия сигнала на входе 44 синхронизации управления устройства оно начинает работать в режиме чтения. Единичный сигнал с выхода второго разряда регистра 11 поступает на входы режима чтения

5

0

накопителей 1 и 2 и разрешает их ра боту в режиме чтения. Кроме того, этот сигнал поступает на второй вход 136 блока 23 контроля чтения и четвертый вход 159 блока 24 синхронизации чтения.

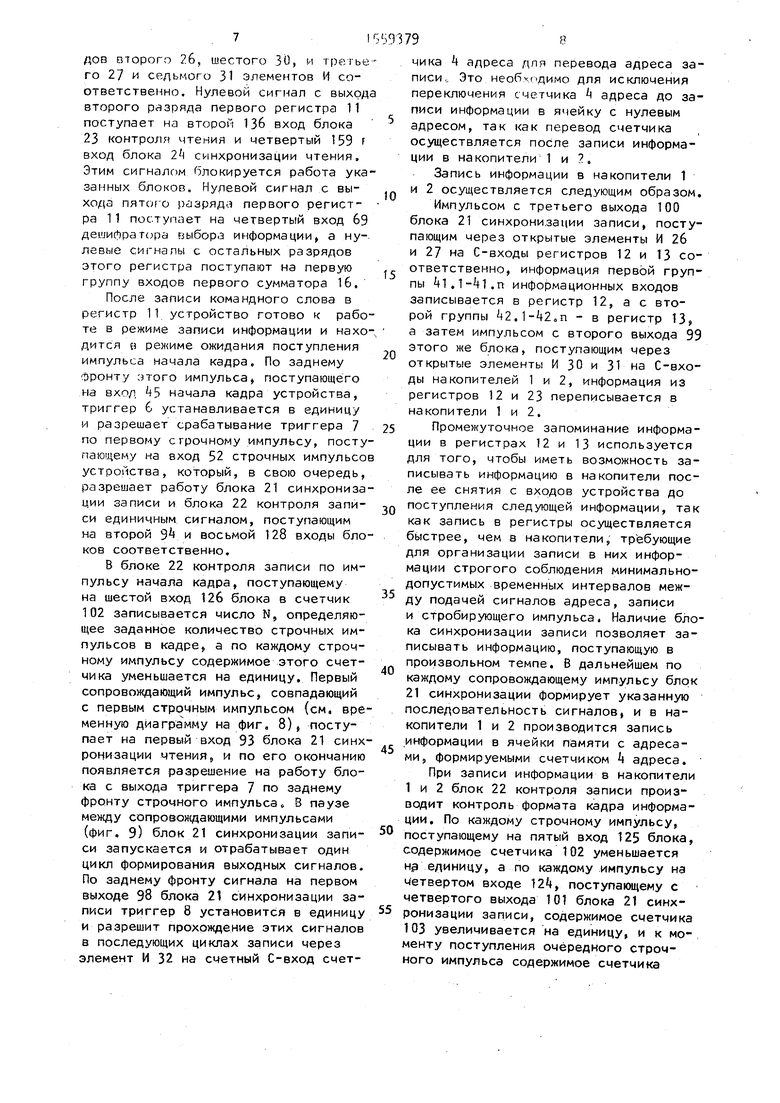

При этом в блоке 23 контроля чтения появление указанного сигнала вызывает появление на выходе дешифратора 131 числа, равного наибольшему возможному адресу ячеек ламяти накопителей 1 и 2, а в блоке 24 синхронизации чтения этот сигнал снимает запрет с работы блока. После снятия запрета с работы блока 24 синхронизации чтения он начинает формировать сигналы на своих выходах в соответствии с временной диаграммой, приведенной на фиг о 10. Сигналом с пятого выхода 166 блока подтверждается исходное состояние первого триггера 5. Этот же сигнал поступает через элемент ИЛИ 35 на С-вход четвертого триггера

5 8, который устанавливается в единицу по заднему фронту этого сигнала и разрешает прохождение сигналов с этого выхода блока через элемент И 32 на С-вход счетчика адреса 4, содержимое которого по каждому очередному импульсу будет увеличиваться на единицу. Запрет на срабатывание счетчика 4 адреса по первому импульсу на пятом выходе 166 блока 24 синхронизации необходим для обеспечения считывания информации из ячейки накопителей с нулевым адресом. Затем на четвертом выходе 165 зтого блока появляется сигнал, поступающий через элементы И 30 и 31, открытые единичными сигналами с выходов третьего и четвертого разрядов регистра 11, на С-входы накопителей 1 и 2 соответственно.

На время наличия этого сигнала на

с выходах накопителей присутствует ич- формация, которая по импульсу на третьем выходе 164 блока 24 синхронизации чтения записывается в регистры 14 и 15. Так как на D-входе пятого триггера 9 присутствует единица, поступающая через элемент ИЛИ 38 с выхода элемента НЕ 39, на вход которого поступает нулевой сигнал с выхода пятого разряда регистра 11, то по импульсу на первом выходе 1б2 блока, разрешающему прохождение на С-вход триггера 9 через элемент И 33 одного импульса частоты генератора 10, триггер установится в единицу и сигналом

0

5

0

0

5

со своего выхода, поступающим на второй вход 157 блока 2k синхронизации чтения, блокирует его работу и устанавливает первый триггер 5 в единицу. Сигнал 6 выхода триггера 5 поступает на вход второго канала (п+1)-го разряда мультиплексора 3. С этого момента устройство находится в ожидании запроса на выдачу информации считанной из накопителей 1 и 2 и хранящейся в регистрах И и 15 соответственно. Запрос на выдачу информации в режиме чтения без обработки информации должен поступать на устройство с задержкой относительно окончания импульса на входе kk синхронизации управления устройства, равной

t-i«-m

12Т,

(1)

10

где то период частоты генератора устройства.

Запрос на выдачу информации в режиме чтения без обработки информации поступает на устройство следующим образом. На входы 5.1-5.1 адреса выдачи информации поступает код, соответствующий кодовой комбинации обращения к устройству по чтению информации, и на первом выходе дешифратора 19 появляется сигнал, разрешающий прохождение сигнала с выхода 55 синхронизации выдачи информации через элемент М 28 на второй вход 67 дешифратора 20, на третьем входе 68 которого присутствует нулевой сигнал с выхода элемента И 29, а на первом 65 и четвертом 69 входе - нулевые сигнала с выходов первого и пятого разрядов регистра 11 соответственно. В результате на первом 70 и четвертом 73 выходах дешифратора 20 появятся единичные сигналы на время наличия сигнала на входе 55 синхронизации выдачи информации, а на втором 71 и третьем 72 выходах останутся нулевые сигналы, которые подтвердят готовност мультиплексора 3 к открыванию первого канала.

Сигнал с четвертого выхода 73 дешифратора 20 поступает на вход запрета мультиплексора 3, и на время его наличия открывается первый канал мультиплексора, в результате чего сигналы с выходов регистров k и 15 поступающие на входы первого канала разрядов с первого по n-й и с (п+1)-го по и-й (т 2п) мультиплексора 3 соответственно, пройдут на выход соответствующих разрядов 5б.1-5б.т инфор.

ь 10

мационного выхода устройства, а в ос тальных разрядах будут нули, так как входы оставшихся разрядов первого ка нала мультиплексора соединены с шиной нулевого потенциала устройства. Сигнал с первого выхода 70 дешифратора 20 поступает на пятый вход 160 блока 2k синхронизации чтения, приводит его триггерные элементы в исходное состоя ние, и после его окончания блок начинает новый цикл формирования сигналов считывания информации из накопителей 1 и 2.

Таким образом, после каждого очередного считывания информации из устройства оно готово к выдаче информации из следующей ячейки памяти накопителей через время 12T0 и нахо- 20 дится в режиме ожидания запроса информации, что позволяет считывать информацию с произвольным темпом обращения к устройству.

Выходы счетчика k адресов, кроме адресных входов накопителей 1 и 2, соединены с группой адресных входов 138.1-138.k блока 23 контроля чтения. В процессе

15

25

30

отработки режима чтения сигналы с адоесных входов 138.1-138.k блока 23 контроля чтения поступают на

вторую группу

5

0

5

0

5

входов блока 132 сравнения, на первую группу входов которой поступает число с выхода дешифратора 131 и при совпадении их на выкоде блока сравнения А В появляется единичный сигнал,; который разрешает срабатывание триггера 133 по сигналу на первом входе 135, который поступает из блока 2k синхронизации с первого выхода 162 после чтения информации из очередной ячейки памяти. После срабатывания триггера 133 на выходе 139 блока 23 контроля чтения появляется сигнал, поступающий на первый вход 156 блока 2k синхронизации чтения, который блокирует работу этого блока. На этом режим чтения без обработки завершается

При чтении информации только из первого либо только из второго накопителей работа устройства аналогична описанной, за исключением того, что при этом.в управляющем слое единичный сигнал подается только на соответствующий вход kB либо 9 включения первого либо второго накопителя„ При этом информация будет считываться только из соответствующего накопителя , а на выходе второго будут нулевые сигналы.

1515

Таким образом, при чтении без обработки информации устройство последовательно выдает информацию, записанную в накопители, причем подготовка к выдаче информации из каждой последующей ячейки ламяти производится после поступления запроса на выдачу информации из предыдущей ячейки памяти считывания ее из устройства, После выдачи информации из предыдущей ячейки и подготовке информации из следующей ячейки памяти для выдачи устройства находится в ожидании запроса, что позволяет организовать выдачу информации из устройства с произвольным темпом обращения к нему.

Рассмотрим работу устройства в режиме чтения с селекцией выдаваемой информации. После окончания режима записи, когда информация, подлежащая обработке, занесена в оба накопителя, на входы 46-50, 51..п управления устройства подается управляющее слово со следующим значением управляющих сигналов.

На вход 47 режима чтения, входы 48 и 49 включения первого и второго на-- копителей и вход 50 режима селекции устройства подаются единичные сигналы, на вход 46 режима записи - нулевой сигнал, а на входы 51.1-51-п. порога селекции устройства подается требуемый код порога селекции. Аналогично описанному в режиме работы без обработки информации управляющее слово записывается в регистр 11 при наличии соответствующих сигналов адресов управления на входах 4341-43.1 устройства и сигнала на входе 44 синхронизации управления устройства.

Работа функциональных узлов устройства в режиме чтения с селекцией отличается от работы в режиме чтения без обработки тем, что после каждого считывания информации из накопителей 1 и 2 и запоминания ее в регистрах 14 и 15 соответственно происходит

сложение информации , записанной в регистре 15 с кодом селекции Р на первом сумматоре 16, а затем полученная сумма вычитается на втором сумматоре 17 из значения информации Гг в регистре 14. Вычитание выполняется по методу второго дополнения за счет того, что на вторую группу входов второго сумматора 17 подается обратный код с выхода первого сумматора 16 через группу элементов HF

0

379

5

16

40,.n, увеличенный на единицу, так как на вход переноса сумматора 17 подается постоянный уровень логической единицы.

Если полученная разность

Т1«- (I2,- + Р) f. 0, то на выходе перено- са второго сумматора 17 будет присутствовать нулевой сигнал, который запретит прохождение единичного сигнала с выхода пятого разряда регистра 11 (сигнала режима селекции) через эле- мент И 34 на D-вход триггера 9 и триггер по сигналу с первого выхода r 162 блока 24 синхронизации чтения, поступившему на его С-вход через элемент И 33, останется в исходном состоянии. Это приведет к тому, что нулевой сигнал с выхода триггера 9, поступивший на второй вход 157 блока 2 синхронизации чтения, разрешит дальнейшую работу этого блока и он начнет формировать управляющие сигнал ы для считывания информации из ячейки накопителей со следующим адресом. Если полученная разность

- (I

г

Р)/ О,

Х1 ч,-то на выходе переноса

0

5

0

5

0

5

второго сумматора 17 появится единица и триггер 9 установится в единицу по сигналу с первого выхода 162 блока 24 синхронизации чтения, поступающему через элемент И 33 на его С-вход, и блокирует дальнейшую работу блока 24 синхронизации чтения подачей на его второй вход 157 единичного CHI- нала, и, кроме того, этот сигнал устанавливает триггер 5 в единицу. В результате, при наличии на выходе сумматора 17 информации т.. , О устройство, аналогично работе в режиме чтения без обработки информации, переходит в режим ожидания запроса на выдачу информации.

Так как время появления информации I. / 0 заранее не определено, то для определения готовности устройства к выдаче информации в режиме чтения с селекцией на входы 54.1-54.1 адреса выдачи информации и вход 55 синхронизации выдачи информации с произвола-; ной периодичностью подаются сигналы аналогично описанному в режиме чтения без обработки, и на втором входе 67 дешифратора 20 выбора информации появляется единичный сигнал. Так как на четвертом входе 69 этого дешифратора присутствует единичный сигнал с выхода пятого разряда регистра 11, а на первом 66 и третьем 68 входах

1/

нулевые сигналы, то на втором 71 и четвертом 73 выходах дешифратора появятся единичные сигналы, а на первом 70 и третьем 72 - нулевые. Вследствие этого на первый и второй адресные входы мультиплексора 3 Поступают единичный и нулевой сигналы, а на вход запрета - единичный сигнал, и на выходы устройства через открытый второй канал мультиплексора пройдут сигналы с выходов сумматора 17 в разрядах с первого по п-й, в разряде (п+1) будет единичный сигнал с выхода первого триггера 5, наличие которого определяет присутствие в разрядах с первого по n-й информации I- 0, а в разряде (тн-2) будет сигнал с выхода 139 блока 23 контроля чтения. Значение остальных разрядов выходного слова информации в этом случае всегда будет равным нулю, так как соответствующие входы второго канала мультиплексора подключены к шине нулевого потенциала устройства. Отсутствие единицы в (п-И)-м разряде при опросе информации по первому адресу выбора информации говорит о том, что информация I- 3- О отсутствует.

Если при опросе по первому адресу получена единица в (п+1)-м разряде, то для идентификации полученной с помощью селекции информации необходимо определить адрес ячеек накопителей 1 и 2, из которых была считана информация для селекции. Для этого после получения единицы в (п+1)-м разряде на входы 5.1-5.1 адреса выдачи информации подается кодовая комбинация,

соответствующая второму адресу выдачи информации, и на втором выходе дешифратора 1Э появляется единичный CHI- нал, разрешающий поступление импульсного сигнала с выхода 55 синхронизации выдачи информации устройства через элемент И 29 на третий вход 68 дешифратора 20, и, так как на его четвертом входе 69 также присутствует единица, единичные сигналы появятся на его первом 70, третьем 72 и четвер том 73 выходах. Это приведет к тому, что единичные сигналы с третьего 72 и четвертого 73 выходов дешифратора 20 откроют третий канал мультиплексора, входы соответствующих разрядов которого соединены с выходами разрядов счетчика 4 адреса, и на информационных выходах 56.1-56.k устройства появится код адреса, соответствующий

15

10

15

25

-5д 5937913

текущему состоянию счетчика b адреса, в котором была получена информация I, ъ 0, Одновременно с этим сигнал с первого выхода 73 дешифратора 20 5 поступает на пятый вход 160 блока 2 А синхронизации чтения, приводит его в исходное состояние, а сигналом с его второго выхода 163 сбрасывает триггер 9, и после этого начинается новый цикл считывания информации из накопителей 1 и 2,

После считывания информации из последнего .адреса накопителей 1 и 2 на выходе 139 блока 23 контроля чтения появляется сигнал, который блокирует работу блока 2h синхронизации чтения и поступает на вход второго канала (п+2)го разряда мультиплексора 3. 20 Появление единицы в (п+2)-м разряде информационного слова пp считывании сообщения о наличии (или отсутствии) информации по первому адресу выдачи информации служит сообщением об окончании цикла чтения с селекцией.

Таким образом, устройство при работе в режиме чтения информации с селекцией производит предварительную обработку выдаваемой информации, Вы дача информации производится только в случае, если результат обработки

I- 11( - (1г, + Р)7, 0 (2)

В этом случае устройство позволяет считать в приемник информации адрес ячеек накопителей, при считывании из которых получено данное значение информации, необходимой для идентификации сообщения. Кроме того, устройство обеспечивает работу при обращении к нему в режиме чтения с произвольным темпом за счет наличия блока синхронизации чтения. Сокращение объема выдаваемой информации за счет селекции позволяет сократить время передачи ее, а также уменьшить объем последующей обработки этой информации.

Буферное оперативное запоминающее устройство обеспечивает следующие варианты работы:

раздельная запись информации в накопители 1 и 2;

одновременная запись информации в накопители 1 и 2;

раздельное чтение информации из накопителей 1 и 2;

одновременное чтение информации и из накопителей 1 и 2;

одновременное чтение информации из накопителей 1 и 2 с обработкой (се30

35

40

45

55

1915

лекцией) информации, обеспечивающей выбор и передачу только той информации из накопителя 1, знамение которой равно либо больше значения информации в соответствующей ячейке памяти накопителя 2, сложенного с заранее выбранным числом (порогом селекции) .

При использовании работы устройства в режиме чтения с селекцией получается значительный выигрыш в скорости передачи информации при чтении ее из устройства и в объеме последующей обработки, При использовании в качестве датчика при фокусировании оптической системы ПЗС-матрицы paccoi- ласование системы определяется по местоположению на матрице (которая используется как система координат) энергетического центра светового пятна, причем для обеспечения требуемой точности диаметр его должен быть значительно меньше геометрических размеров матрицы.

Для определения энергетического центра светового пятна необходимо вначале непосредственно перед съемом информации о световом пятне произвес

ти съем информации I/, с ПЗС-матрицы для определения фонового освещения, затем произвести съем информации I,, при наличии светового пятна и для исключения влияния фонового освещения из информации для каждого элемента матрицы вычесть информацию I,,. Кроме того, для исключения влияния случайных факторов, из полученной разности необходимо вычесть величину пороговой информации Р, одинаковую для всех ячеек ПЗС-матрицы для данных условий измерения. После чего координаты энергетического центра определяются при помощи математической обработки, сложность которой зависит от требуемой точности. Пусть имеется ПЗС-матрица размерности , где N - число строк, М - число элементов в строке.

Тогда время для чтения информации 14, хранящейся в первом накопителе, и хранящейся во втором накопителе, при передаче информации без обработки и параллельном считывании информации из обоих накопителей будет равно

.«. (з)

T4m N-M t

где t

8 И А

время чтения одного слова информации из устройства.

20

Если принять размеры матрицы 25б элементов, а диаметр пятна d 5 элементов, то получится, что объем передаваемой информации составит 65536 слов, из которой полезная информация будет составлять только около двадцати слов, т. е. менее 0,05% всего объема. Если выбрать частоту тактового генератора, такой, чтобы из (1) выполнялось условие

Ч«т свщ гЛе Чч вРемя считывания одного слова из накопителей 1 и 2 и записи его в регистры и 15,

5 то можно пренебречь временем обработки информации. Следовательно, время передачи обработанной предварительно информации составит менее 0,05 времени на передачу всего кадра. Таким

0 образом, выигрыш во времени только от сокращения объема передаваемой информации составит более . Кроме того, необходимо учесть сокра- щение времени последующей математи5 ческой обработки информации по вычислению координат энергетического центра светового пятна, которая зависит от быстродействия применяемого вычислителя. При обработке всего массива

Q информации по указанному алгоритму вычислителем необходимо выполнить 1310/2 операций сложения (вычитания). При быстродействии вычислителя 1 100 тыс. оп./с это составит более 1,3 с.

Введение контроля формата принимав мого устройством информационного кадра повышает достоверность получаемой информации, так как сбой в количест. ве строчных импульсов или в количест- 0

ве сопровождающих импульсов, которые

определяют, по сути, координаты ячейки ПЗС-матрицы, из которой выдается информация, при передаче ее из источ.,. ника информации могут значительно повлиять на результаты вычислений.

Устройство обеспечивает запись принимаемой информации при ее поступлении в произвольном темпе и выдачу ее

п в приемник информации по запросам, также поступающим в произвольном темпе. Возможность записи информации в произвольном темпе позволяет снизить требования к стабильности периода формирования сопровождающих и строчных импульсов источником информации. Снижение требований к источнику информации позволяет упростить его и уменьшить его габаритные размеры,

5

что приводит к улучшению характеристик всей оптической системы, поскольку источник информации конструктивно располагается в зоне приема оптической информации, Возможность смитыва- ния информации в произвольном темпе снижает требования к приемнику информации в части его быстродействия.

Таким образом, буферное оперативное запоминающее устройство обеспечивает более высокое быстродействие при выдаче информации, более высокую достоверность принимаемой информации и возможность асинхронного обращения к нему при записи и чтении информации.

Формула изобретения

Буферное оперативное запоминающее устройство, содержащее два накопителя, мультиплексор, счетчик адреса и первый триггер, причем выходы счетчика адреса с первого по k-й соединены с входами соответствующих разрядов третьего канала мультиплексора, (где k - разрядность счетчика адреса), отличающееся тем, что, с целью повышения быстродействия устройства, повышения достоверности при нимаемой информации и обеспечения обращения к устройству асинхронных источника и приемника информации, устройство содержит триггеры с второго по пятый, генератор тактовых импульсов, регистры с первого по пятый, первый и второй сумматоры, дешифратор адреса управления, дешифратор адреса выдачи информации и дешифратор выбора информации, блок синхронизации записи, блок контроля записи, блок контроля чтения, блок синхронизации чтения, элементы И с первого по десятый , элементы ИЛИ с первого по четвертый, элемент НЕ и группу из п элементов НЕ, причем первый информационный вход первого регистра соединен с входом режима записи устройства, второй информационный вход первого регистра соединен с входом режима чтения устройства„ третий и четвертый информационные входы первого регистра соединены с входами включения первого и второго накопителей устройства соответственно, пятый вход первого регистра соединен с входом режима селекции устройства, информационные входы с шестого по (п+5)-й первого ре0

5

0

гистра соединены с входами кода порога селекции устройства с первого по n-й разряд соответственно, где п - число разрядов кода селекции порога, первый выход первого регистра подключен к D-входу второго триггера, седьмому входу блока контроля записи, входам управления записью первого и второго накопителей и первому входу дешифратора выбора информации, второй выход первого регистра соединен с вторым входом блока контроля чтения, четвертым входом блокировки блока синхронизации чтения и входами управления чтением первого и второго накопителей, третий выход первого регистра соединен с первыми входами второго и шестого элементов И, четвертый выход первого регистра подключен к первым входам третьего и седьмого элементов И, пятый выход первого регистра соединен с четвертым входом дешифратора выбора информации, входом элемента НЕ и вторым входом десятого элемента И, с шестого по (п+5)-й выходы первого регистра соединены с первой группой входов первого сумматора, входы дешифратора адреса управления являются входами адреса управления устройства, выход дешифратора адреса управления подключен к первому входу первого элемента И, второй вход которого соединен с входом синхронизации управления устройства, вы- 5 ход первого элемента И подключен к установочным R-входам счетчика адреса и второго, третьего и четвертого триггеров, к третьим входам блока контроля записи и блока контроля мте5

0

0

ния, к шестому входу сброса блока

5

синхронизации чтения, второму входу третьего элемента ИЛИ и к С-входу первого регистра, С-вход второго триггера соединен с шестым входом блока контроля записи и входом начала кадра устройства, выход второго триггера подключен к D-входу третьего гера, С-вход которого соединен с пятым входом блока контроля записи и является входом строчных импульсов устройства, выход третьего триггера подключен к второму входу разрешения работы блока синхронизации записи и восьмому входу блока контроля записи, 5 первый вход которого и первый вход записи блока синхронизации записи объединены и являются входом сопровождающих импульсов устройства, информацион0

ные входы второго и третьего регистров подключены соответственно к первой и второй n-разрядным группам информационных входов устройства, выходы второго и третьего регистров соединены соответственно с информационными входами первого и второго накопителей, выходы первого и второго накопителей соединены с информационными входами четвертого и пятого регистров соответственно, выходы четвертого регистра подключены к первой группе входов второго сумматора и к входам соответствующих разрядов с первого по n-й первого канала мультиплексора (где п - разрядность слов каждого накопителя), выходы пятого регистра соединены с второй группой входов первого сумматора и с входами соответствующих разрядов с (п+1)-го по m-й (га-2п) первого канала мультиплексора, выходы первого сумматора соединены с соответствующими элементами группы элементов НЕ, выходы которых подключены соответственно к второй группе входов второго сумматора, вход переноса которого соединен с шиной логической единицы устройства, выходы второго сумматора подключены к входам соответствующих с первого по n-й разрядов второго канала мультиплексора, выход переноса второго сумматора соединен с первым входом десятого элемента И, выход которого подключен к первому входу четвертого элемента ИЛИ, второй вход которого подключен к выходу элемента НЕ, выход четвертого элемента ИЛИ соединен с D-входом пятого триггера, выход которого подключен к второму входу блокировки блока синхронизации чтения и S-входу леового триггера, R-вход которого соединен с выходом третьего элемента ИЛИ, выход первого триггера подключен к входу (п+1)то разряда второго канала мультиплексора,входы (п-И)-го и (п+2) -го разрядов четвертого канала которого соединены соответственно с первым и вторым выходами блока контроля записи, а вход (п4-2)-го разряда второго канала мультиплексора соединен с выходом блока контроля чтения и первым входом блокировки блока синхронизации чтения, входы с первого по n-й и с (п+3)го по k-й разрядов четвертого канала, входы с (пФЗ)-го по k-й разрядов второго канала, входы с (ян-1)-го по k-й

5

0

разрядов первого канала мультиплексора объединены 1 подключены к шине нулевого потенциала устройства, выход генератора тактовых импульсов подключен к второму входу блока контроля записи, третьим входам блока синхронизации записи и блока синхронизации чтения и первому входу девятого элемента И, выход которого подключен к С-входу пятого триггера, R-вход которого соединен с вторым выходом блока синхронизации чтения, пятый вход установки исходного состояния которого подключен к первому выходу дешифратора выбора информации, второй и третий входы которого соединены с выходами четвертого и пятого элементов И соответственно, вторые входы которых объединены и являются входом синхронизации выдачи информации устройства, первые входы четвертого и пятого элементов И подключены соответственно к первому и второму выходам дешифрато5 pa адреса выдачи информации, входы которого соединены с входами адреса выдачи информации устройства, четвертый и пятый входы блокировки блока синхронизации записи соединены с перQ вым и вторым выходами блока контроля записи соответственно, первый выход блока синхронизации записи подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ и

5 пятым выходом блока синхронизации чтения, выход первого элемента ИЛИ подключен к С-входу четвертого триггера и второму входу восьмого элемента и, первый вход которого подключен к выходу четвертого триггера, кои торого соединен с шиной логической единицы устройства, выход восьмого элемента И подключен к С-входу счетчика адреса, выходы которого подключены к адресным входам первого и второго накопителей, к адресным входам блока контроля чтения, второй выход блока синхронизации записи соединен с первым входом второго элемента ИЛИ, вто0

5

0

5

рои вход которого соединен с четвертым выходом блока синхронизации чтения, выход второго элемента ИЛИ подключен к вторым входам шестого и седьмого элементов И, выходы которых соединены с С-входами первого и второго накопителей соответственно, третий выход блока синхронизации записи соединен с вторыми входами второго и тре25€ 15593792

тьего элементов И, выходы которых под- выход блока синхронизации чтения соеключены соответственно к С-входам второго и третьего регистров, четвертый выход блока синхронизации записи подключен к четвертому входу блока контроля записи, первый выход блока синх- оонизации чтения подключен к первому входу блока контроля чтения и второму входу девятого элемента И, третий

динен с С-зходзмп четвертого и пятого регистров, второй, третий и четвертый выходы дешифратора выбора информации соединены с первым, вторым адресными входами и с входом запрета мультиплексора соответственно, выходы которого подключены к информационным выходам устройства.

-S6t

1-56Я

фа&. 2

фие.З

фиа.4

П9

гг. J

/Ф7

Щ 63

Я

фие.5

т

в Qf f k

%

т

яавюот

т

UP

/53

W

I M

R

Ш

Физ.Б

К

SI

5Ь W

фае. в

Авторы

Даты

1990-04-23—Публикация

1988-06-10—Подача