(54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕ УСЧ РОЙСТВО НА МАГНИТНЫХ ДИСКАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для поиска и отображения информации | 1978 |

|

SU744674A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

Изобретение относится к области вычислительной техники, а именно к внешним запоминающим устройствам вычислительных машин. Известны динамические запоминаю. щие устройства на магнитных дисках, состоящие из блока управления и груп пы блоков памяти, количество которых выбирается в зависимости от объема решаемых .задач. Блок уп1)авления при этом определяетномер блока памяти, номер дорожки, вид операции, а блок памяти непосредственно выполняет опе рации под управлением блока управления 1 . Недостатком известных устройств я ляется невозможность обработки второ го запроса во время обработки первог запроса, что снижает производительность устройства, при этом введение блоков управления во все блоки памяти для параллельной обработки запроfcoB усложняет устройство и экономически невыгодно. .-,. , Наиболее близким к изобретению те ническим решением является динамичес кое запоминающее устройство на магнитных дисках, содержащее адресный регистр, дешифратор, 5уферный накопи т ель, переключаТёлй, меха нйзма врауен 1я дисков, механизмы установки магнитных головок, усилители записи и считывания, регистры адреса дорожки, регистры адреса магнит но й гЬл6вк и и узлы вычитания, причем выход буферного накопитёля соединен соответственно с входом устройства, входом дешифратора и с выходом второго переключат теля, выход буферного накопителя соединен соответственно с выходом устройства и с входом первого переключателя, выходы первого и входы второго пер екЛючаТёлей соединены соответственно с входом усилителей записи и с выходе усилителей считывания, выход и вход которых через третьи переключатели подключены к выводам магнитных головок, управляющие входы первого И второго переключателей соединены с выходом адресного регистра, а третьих переключателей - с выходом регистров адреса магнитной головки, вход механизмов установки магнйТных. голоЬок соединен с одним выходом регистров адреса дорожки, который через соответствующий узел вычитания подаслючен к входной шине управления, а выходы адресного регистра в блоке управления подключены к входам разрешения выборки соответствующих блоков памяти 12J.

Недостатком этого устройства является невозможность обработки нескольких одновременно поступивЬих запросов, а также оптимальное построение, очереди из поступивших запросов в зависимости от состояния магнитных го ловок в различных блоках памяти устройства.

- Цель изобретения - повышение бБЮТрдействия Динамического запоминающего устройства на магнитных дисках эа .Счет сокращения времени поиска информации в нескольких блоках памяти,

Поставленная цель достигается тем, что в динамическое запоминающее устройство введены узел оценки состояния устройства, ассоциативные накопители оперативный накопитель и узлы управления, первый вход первого ассоциативного накопителя соединен с входом уст ройства, второй вход - с выходом первого узла вычитания, входы которого соединены соответственно с первым входом первого ассоциативного накопителя и с входом и выходом регистра адреса дорожки. Второй выход первого ассоциативного накопителя соединен с выходом устройства и с входом второго ассоциативного накопителя, первый выход которого соединен с вхсадом регистра .адреса магнитной головки. Второй выход второго ассоциативного накопителя соединен с первым входом второго узла вы 1итания, второй вход и выход которого-Подключены соответственно к выходу усилителя считывания и к первому второго узла управления, выход которого соединен с вторым-входом BTopojro ассоциативного накопителя, третийвыход которого соединен с первым входом оперативного накопителя , первый выход которого соединен с входом дешифратора. Второй выход оперативного накопителя соединен с третьим входом первого ассоциативного накопителя, третий выход с входом, адресного регистра, четвертый выход - с первым входомпервого узла управления и пятый выход - с .входом узла оценки состояния устройства, выводы которого подключены к соответствующим вьзводам первого узла управления, выходы которого соединены соответственно с вторым входом оперативного накопителя и вторым входом второго узла управления 4 Третий выход первого, ассоциативного -накопитет ля соединен с первым входом третьего узла управления -, выходы которого соедйнены с вторым и четвертым йходами первого асеоциа-дивного накопителя.

В первом ассоциативном накопителе регистр адреса выполнен как счетчик со сбрюсом, элементы памяти-, соединенные с третьим входом, выполнены ассоциативными, а вход и выходдополнительной группы разрядов соединены соответственно с третьим выходом и вторым входом третьего узла управления.

Во втором ассоциативном накопителе регистр адреса выполнен как счетчик, а вход и выход дополнительной группы разрядов соединены соответственно с вторым выходом и третьим входом второго узла управления.

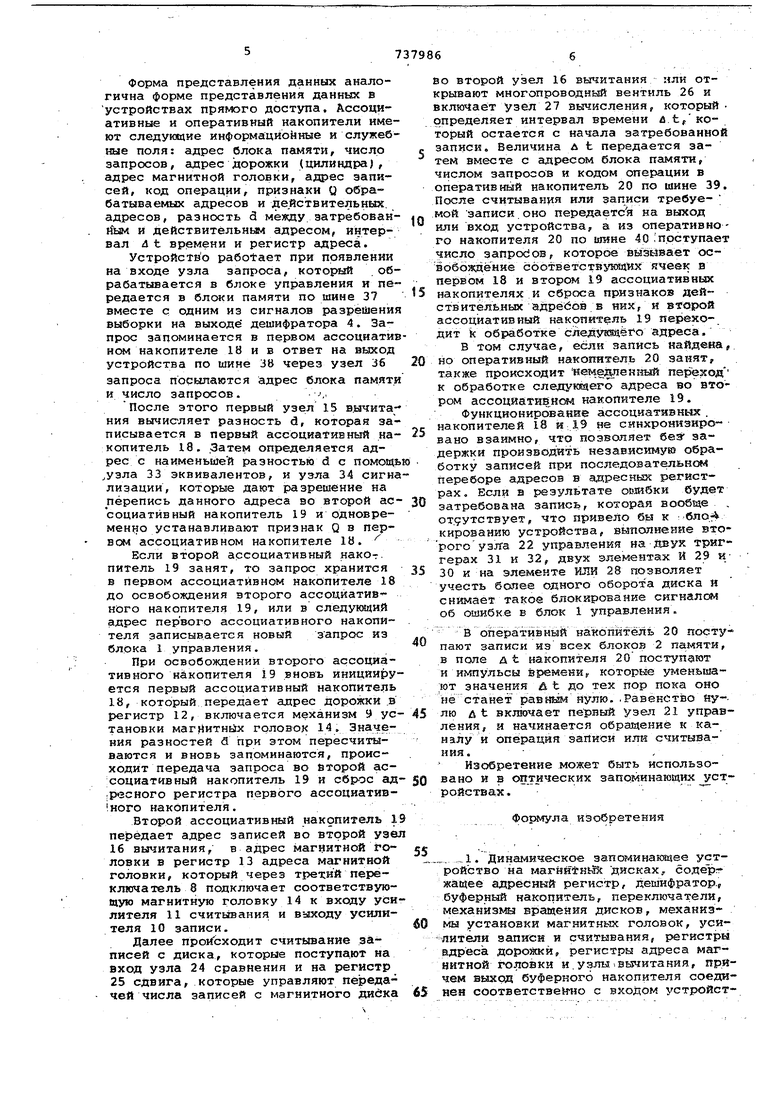

- Устройство содержит дополнительно четвертый узел сравнения, регистр сдвига, многопроводный вентиль и .узел вычисления, выход которого соединен с первым входом оперативного накопителя, а вход - с выходом многопроводного вентиля, входы которого подключены к выходу регистра сдвига и к первому выходу четвертого узла сравнения второй выход которого подключен к второму входу узла вычитания, а входы четвертого узла сравнения и регистр сдвига соединены с выходом усилителя считывания. Второй узел управления содержит два триггера, два злемента И и элемент ИЛИ, выход которого соединен с входами сброса триггеров, выход первого триггера соединен с первьм входом первого элемента И, выход которого соединен с входом установки второго триггера, выход которого соединен с первым входом второго злемен±а И, .вторые входы элементов И объединены.

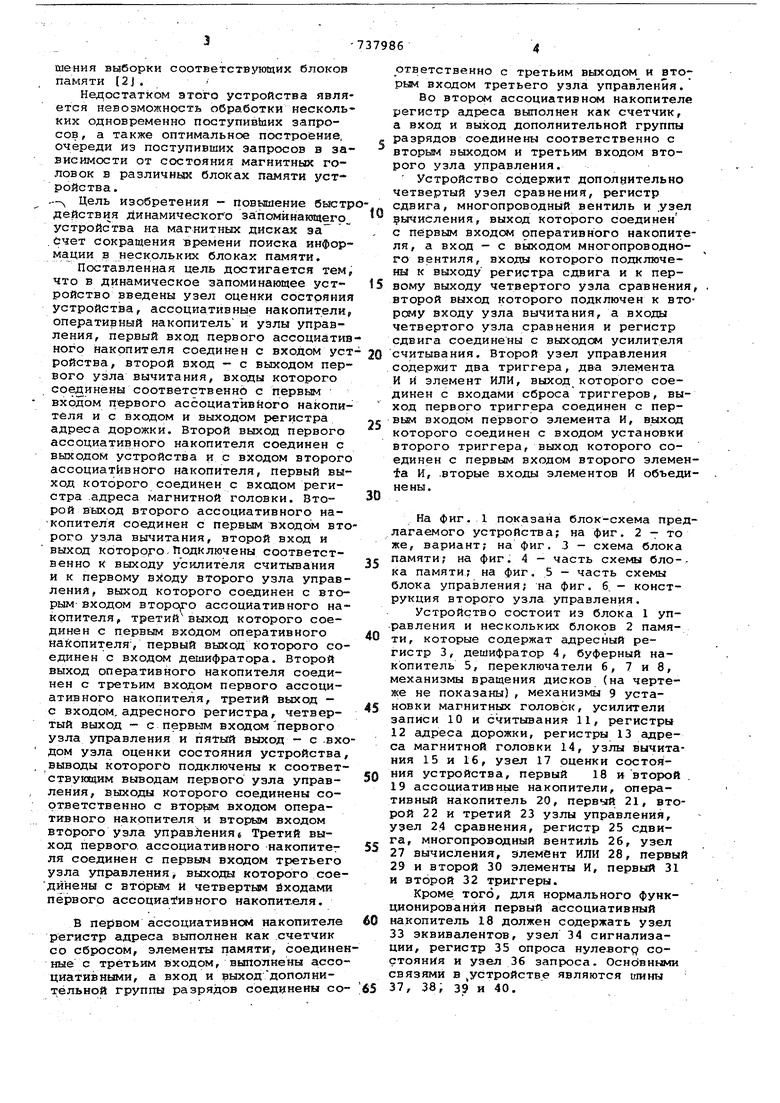

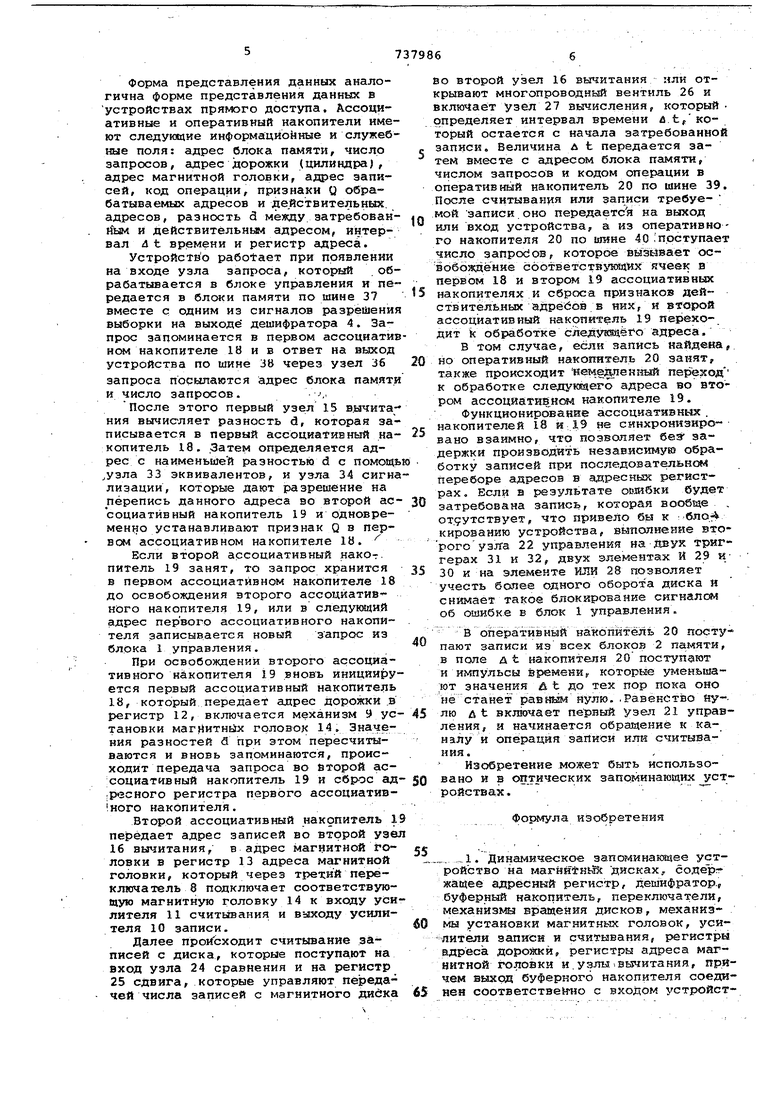

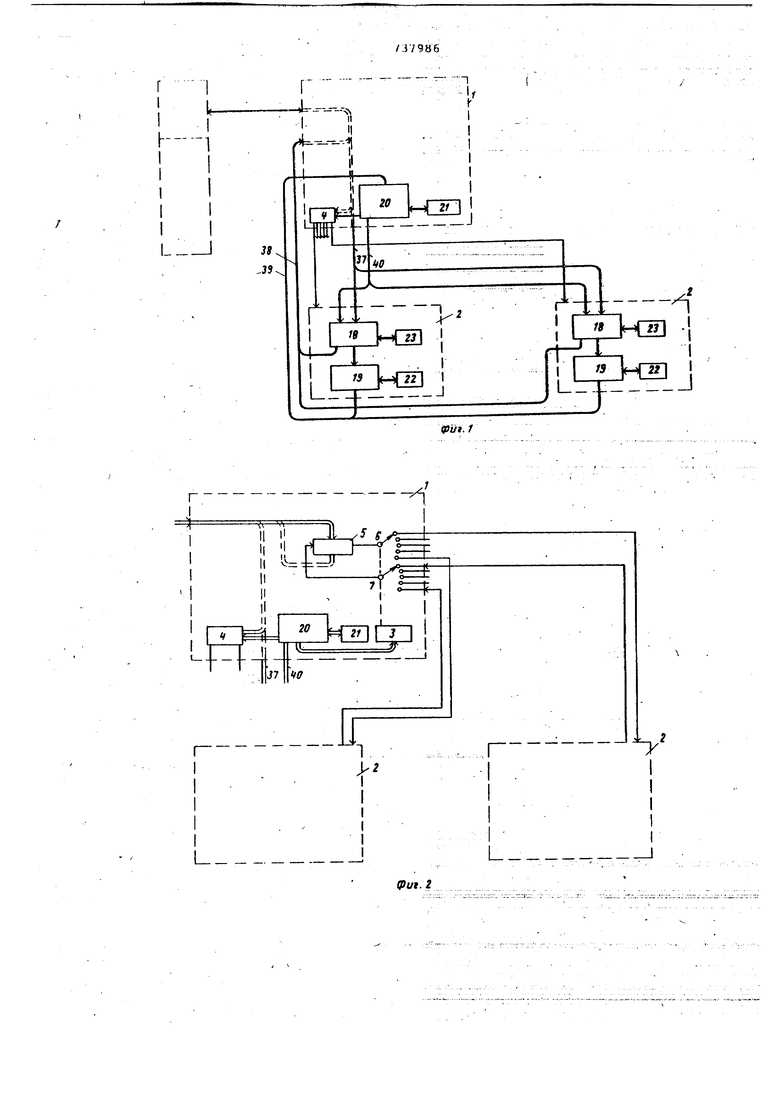

На фиг. 1 показана блок-схема предлагаемого устройства; на фиг. 2 - то же, вариант; на фиг. .3 - схема блока памяти на фиг. 4 - часть схемы блока памяти на фиг. 5 - часть схемы блока управления; на фиг. 6. - конструкция второго узла управления.

Устройство состоит из блока 1 уп.равления и нескольких блоксрв 2 памяти, которые содержат адресный регистр 3, дешифратор 4, буферный накопитель 5, переключатели 6, 7 и 8, механизмы вращения дисков (на чертеже не показаны), механизмы 9 установки магнитных головок, усилители записи 10 и считывания 11, регистры 12 адреса дорожки, регистры 13 адреса магнитной головки 14, узлы вычитания 15 и 16, узел 17 оценки состояния устройства, первый 18 и вторюй 19 ассоциативные накопители, оперативный накопитель 20, первчгй 21, второй 22 и третий 23 узлы управления, узел 24 сравнения, регистр 25 сдвига, многопроводный вентиль 26, узел 27 вычисления, элемент ИЛИ 28, первый 29 и второй 30 элементы И, первый 31 и второй 32 триггеры.

Кроме того, для нормального функционирования первый ассоциативный накопитель 18 должен содержать узел 33 эквивалентов, узел 34 сигнализации, регистр 35 опроса нуле.вогр состояния и узел 36 запроса. Основными связями в устройстве являются шины 37, 38, 39 и 40.

Форма представления данных аналогична форме представления данньвс в устройствах прямого доступа. Ассоциативные и оперативный накопители имеют следующие информациойные и служебные ПОЛЯ: адрес блока памяти, число запросов, адрес дорожки (цилиндра), адрес магнитной головки, адрес записей, код операции, признаки Q обрабатываемых адресов и действительных, адресов, разность d между аатребованйым и действительным адресом, интервал ut времени и регистр адреса.

Устройств pa6otaeT при появлении на входе узла запроса, которьй обрабатывается в блоке управления и передается в блоки памяти по шина 37 вместе с одним из сигналов разрешения выборки на выходе дешифратора 4. Запрос запоминается в первом ассоциативном накопителе 18 и в ответ на выход устройства по шине ЗВ через узел 36 запроса посылаются адрес блока памяти и число запросов. -,,

После этого первый узел 15 вычитания вычисляет разность d, которая записывается в первый ассоциа-еиЕНый накопитель 18. Затем определяется адрес с наименьшей разностью d с помощь узла 33 эквивалентов, и узла 34 сигнализации, которые дают разрешение на перепись данного адреса во второй ассоциатйвный накопитель 19 и одновремен о устанавливают признак Q в первом ассоциативном накопителе 18.

Если второй ассоциативный накот. питель 19 занят, то запрос хранится в первом ассоциативном накопителе 18 до освобождения второго ассоциативного накопителя 19, или в следуквдий адрес первого ассоциативного накопителя записывается новый запрос из блока 1 управления.

При освобождении второго ассоциэ тивного накопителя 19 вновь инициируется первый ассоциативный накопитель 18, который передает адрес дорожки з регистр 12, включается механизм У установки магИитнйх головок 14. Знач|5ния разностей а при этом пересчитываются и вновь за п. оминаются, происходит передача запроса во второй ассоциативный накопитель 19 и сброс ад р зсного регистра первого ассоциатив1иого накопителя.

Второй ассоциативный накопитель 19 передает адрес записей во второй узел 16 вычитания, в адрес магнитной головки в регистр 13 адреса магнитной головки, который через третий переключатель 8 подключает соответствующую магнитную головку 14 к входу усилителя 11 считывания и выходу усилителя 10 записи.

Далее происходит считывание записей с диска. Которые поступают на вход узла 24 сравнения и на регистр 25 сдвига, которые управляют пе редачей числа записей с магнитиого дибка

во второй узел 16 вычитания или открывают многопроводный вентиль 26 и включает узел 27 вычисления, который определяет интервал времени и t,который остается с начала затребованной записи. Величина д t передается затем вместе с адресом блока памяти, числом запросов и кодом операции в оперативный накопитель 20 по шине 39. После считывания или записи требуемой записи, оно передается на выход или вход устройства, а из оперативного накопителя 20 по шине 40 ;п.оступает число sanpodOB, которое вы зйвает освобождёние соответствующих ячеек в первом 18 и втором 19 ассоциативных накопителях и сброса признаков действительных адребоа в них, и второй ассоциативный накопитель 19 переходит k обработке следукшгёго адреса.

В том случае, если запись найдена, но оперативный накопитель 20 занят, также происходит иемедпенкый переход к обработке следукедего адреса во втором ассоцйатийном накопителе 19.

Функционирование ассоциативных . накопителей 18 и .19 не сикхроянзиро вано взаимно, что позволяет без задержки производить независимую обработку записей при последовательном переборе адресов в алресньк регистрах. Если а результате оезибки будет затребована запись, которая вообще от9утствует, что привело бы к : блоЛ кировамию устройства, выполнение второгоузяа 22 управления на ивух триггерах 31 к 32, двух элементах И 29 и 30 и на элементе ИЛИ 28 позволяет учесть более одного оборота диска и снимает такое блокирование сигнале об ошибке в блок 1 управления.

В оперативный накопитель 20 поступают записи из всех блоков 2 памяти, в поле д t накопителя 20 поступают и импульсы временир которые уменьшает значения и t до тех пор пока оно не станет равным нулю. .Равенство йу-. лю д t включает первый узел 21 управления, и начинается обращение к кана.)ту и операция записи или считывания. ,

Изобретение может быть использовано и в оптических запо 5инаювд11х устройства;Х.

ФоЕНигула изобретения

.... ,Л. Динамическое запог инающее устройство на магни к & дисках, солергжйщее адресный регистр, дешифратор., буферный накопитель, переключатели, механизмы вращения дисков, механизмы установки магнитных головок, уси

-лители записи и считывания, регистры вдреса дорожки, регистры адреса магнитной головки и.узлы Iвычитания, причем выход буферного накопителя соединен соответствей-но с входом устрсйства, входом дешифратора и с выходом второго переключателя, выход буферно.гр накопители соединен срответственfjQ- -sbixbnoMycTpofif первого переключателя, выходы первого и входы второго переключателей соединены соответствейнр с. входом усилителей записи и с выходом усилйТёлёйГ считывания, выход и вход которых через третьи переключатели подключены к выводам магнитных головок,у;правляющие входы первого и второго переключателей соединены с выходом алресного регистра, а третьих переключ ателей - с выходом регистров адреса магнитной головки, вход механизй6й з; 6Танрвки маг.нитных головок соединен с одним выходом регистров адреса дорожки, о т л и ч а ю щ е е с я тем, что, с целью повыиения быстродействия устррйства за счет сокращения времени поиска информации, в него введены узел оценки состояния устройства, ассоциативные накопители, оперативный накопитель и узлы управления, первый вход перврго ассоциативного накопителя соединен с входом устройства, второй вход - с выходом первого узла вычитания, входы которого с о еди не ны соответственно с первым выходом первого ассрциативного накопителя и с вхрдом и выходом регистра адреса дорожки, второй выход первого ассоциативнрго накопителя соединен с выходом устройства и с входом второго ассоциативного накопителя, первый выход которого соединен с входом регистра адреса магнитной головки, второй)выход второго ассоциативного накопителя соединен с первым входом второго узла вычитания, второй вход игвыхоД которрго подклю,чены соответственно к выходу усилителя считывания и к первому вхсшу второго уёла управления, выход которого соедмнен с вторым входом второго ассоциативного накопителя, третий выход которого соединен спервым входом оперативнргр накопителя, первый вНхОД которого соединен с входом детиифратора, второй выход оперативного накопителя соединен с третьим входом первого ассоциативного накопителя, третий выход - с вхОдом адресйОтб регистра, четвертый выход - с первым входом первого узла управления и пять1й выход - с входом узла оценки состояния устройства, выводы кОторюго подключены к соотвётствукяцим выводам первого узла управления, выходы уо торого соединены соответственно с вторым входом оперативного накопителя и BTopbw входом второго узла управления, третий выход . первого асоциативирго накопителя соединен с первым входом третьего узла управления, выходы которого соединены с вторым и четвертым входами первого ассоциатквного накопителя.

2,Устройство по п. 1, отличающееся тем, что в перврм ассоциативном накопителе регистр адреса выпрлнен как счетчик со сбросом, элементы памяти, соединенные с третьи входом, выполнены ассоциативными, а вход и выход дополнительной группы разрядов соединены соответственно с третьим выходом « вторым входом третьего узла управления.

3,Устройство по п. 1, отличающееся тем, что во втором ассрциативнсни накопителе регистр адреса выполнен как счетчик, а вход и выход дополнительной группы разрядов соединены соответственно с вторым выходом и третьим входЪм второго узла управления.

Источники информации, принятые во внимание при экспертизе

h-

I

f

ТС

If

.,-Г

Kt

L

27

(fi,

13

ттшг

Авторы

Даты

1980-05-30—Публикация

1973-08-03—Подача