1

Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в устройствах различного назначения, в частности управления и синхронизации.

Известны автоматические следящие делители периодов следования импульсных сигналов (умножители частоты), содержащие входной управляющий триггер, элемент ИЛИ и опорный импульсный генератор, подключенный ко входам двух каналов обработки информации. Каждый из каналов содержит последовательно соединенные схему совпадения, счетчик-делитель, счетчик-измеритель и схему сравнения, соединенную с элементом ИЛИ и входом соответствующего следящего счетчика-делителя, подключенного к другому входу схемы сравнения и выходу установленной в другом канале схемы совпадения

Недостаток этих устройств - двухканальность структуры - устраняется в од- ноканальных умножителях частоты перио-

дических импульсов, содержащих опорный генератор, подключенный к нему масштабный делитель частоты, схему заполнения, содержащую два счетчика, первый из которых (счетчик-из мерите ль) подключен к делителю, а второй (счетчик-делитель) - к опорному генератору, ЗУ, подключенное к выходам ячеек первого счетчика, и схему сравнения, подключенную к выходам ячеек ЗУ и вто10рого счетчика, выход которой соединен с выходом устройства sj ир4.

Недостатком этих устройств является наличие нескомпенсированного остатка деления периода.

15

Наиболее близким по технической сущности к изобретению является устройство для деления периодов следования импульсных сигналов LSJ. В нем компенсируется остаток деления периода за

20 счет введения блока коррекции остатка. Это устройство содержит блок делителя, включающий в себя входной управляющий триггер, элемент ИЛИ и опорный

импульсный генератор, подключенный ко входам двух каналов обработки информещии, каждый из которых содержит последовательно соединенные схему совпадения, счетчик-делитель (масштабный делитель частоты), счетчик-измеритель и схему сравнения, соединенную с элементом иЛи и входом соответствующего следящего счетчика-делителя, подключенного к другому входу схемы сравнения и выходу установленной в другом канале схемы совпадения, сбросовый вхрд которой соединен с одним из выходов входного управляющего триггера и сбросовыми входами соответствующего счетчикаделителя и счетчика-измерителя. Устройство содержит также блок коррекции остатка, входы которого соединены со вторыми выходами счетчиков-делителей, выходом элемента ИЛИ и выходами входного управляюш зго триггера. Блок коррекции остатка содержит четыре схемы совпадения, три сумматора, три дешифратора, два счетчика, матричный определитель задержки, управляющий триггер и элемент задержки.

Недостатками этого устройства является то, что ключевым элементом блока коррекции остатка, определяющим точность коррекции, является элемент задержки, номинал которого должен соответствовать строго определенной величине, равной

То

f о

L . -

Ь N

- Авеличина задержки;

где

Т - период следования импульсов о опорного генератора; N - коэффициент деления устройства.

Поскольку ряд номиналов линий задержки, выпускаемых промыщленностью, имеет ограниченную нормалью дискретность, во многих случаях равенство не может быть обеспечено и необходимая точность коррекции оказывается не реализуемой, что снижает точность делителя. Вместе с тем фиксированная для данного устройства величина элемента задержки ограничивает диапазон коэффициентов деления,

Кроме того, двухканальность структуры следящего делителя и большой объем блока коррекции остатка (блок содержит четыре схемы совпадения, три сумматора, три дешифратора, два счетчика, триггер, .элемент задержки и матричшлй определитель задержки) усложняет устройство и снижают надежность его работы.

Целью изобретения является повышение точности работы, расширение диапазона коэффициентов деления и упрощеьше устройства.

Поставленная цель достигается тем, что устройство для деления периодов следования импульсшз1х сигналов, содер-т.

0 Жащее опорный генератор, масштабный делитель частоты, счетчик-измеритель, счетчик-делитель, схему сравнения, триггер, счетчик остатка, элемент И, элемент ИЛИ и первый элемент задержки,

5 выход масштабного делителя частоты подключен ко входу счетчика-измерителя, а входы сброса их соединены между собой, выходы разрядов датчика делите-, ля подключены к первой группе входов

0 схемы сравнения, первый вход, элемента И подключен к единичному выходу триггера, дополнительно содержит регистр, умножитель частоты, делитель частоты, регистр остатка, схему сравнения остат-

ка и второй элемент задержки. Выход

опорного импульсного генератора подключен ко входу масштабного делителя частоты. Выходы счетчика-измерителя подключены ко входам регистра, выходы ко0 торого подключены ко второй группе входов схемы сравнения, выход которой подключен к выходу устройства. Вход умножителя частоты подключен к выходу опорного импульсного генератора, а

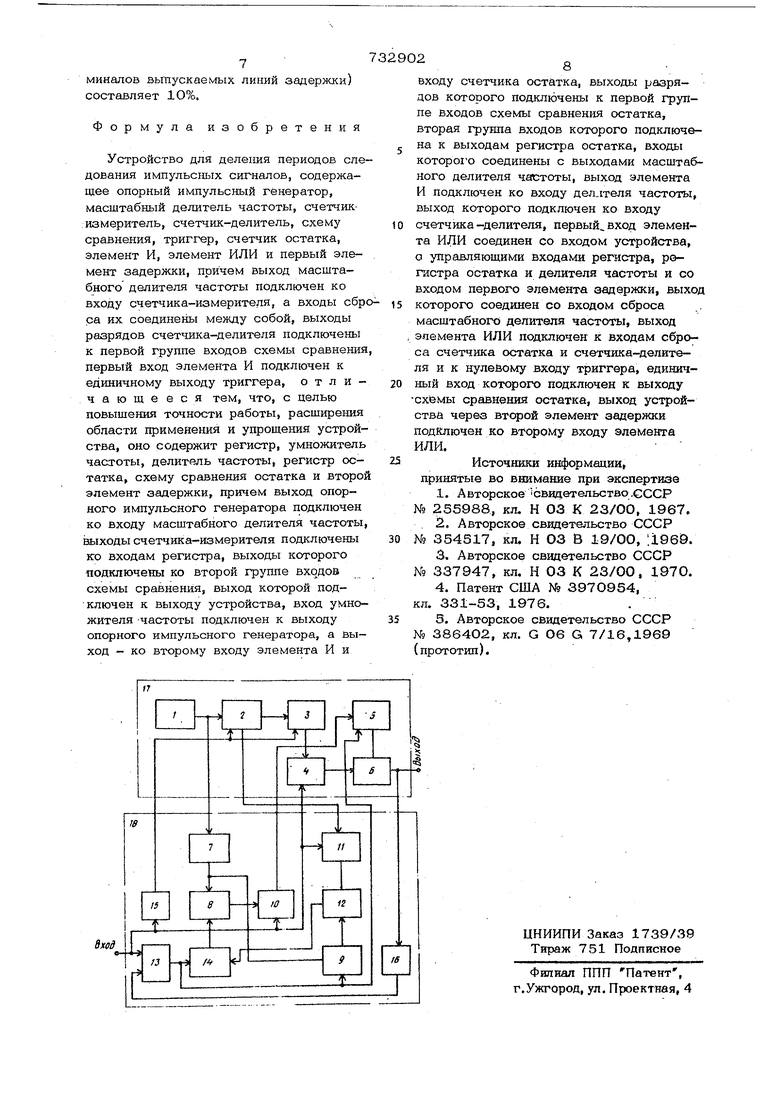

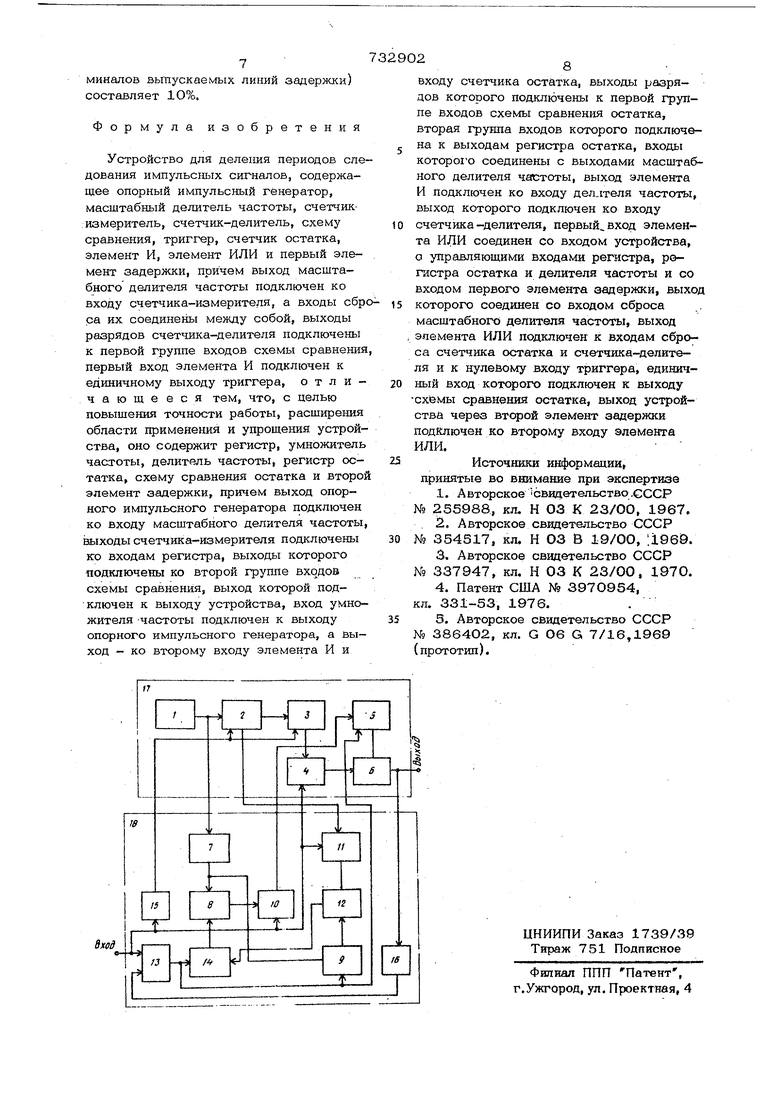

5 выход - ко второму входу элемента И и входу счетчика остатка, выходы разрядов которого подключены к первой группе входов схемы сравнения остатка, вторая группа входов которой подключена к выходам регистра остатка, входы которого соединены с выходами масштабного делителя частоты. Выход элемента И подключен ко входу делителя частоты, выход которого подключен ко входу счетчика-делителя. Первый вход элемента ИЛИ соединен со входом устройства, с управляющими входами регистра, регистра остатка и делителя частоты и со входом первого элемента задержки, выход которого соединен со входом сброса масштабного делителя частоты. Выход элемента ИЛИ подключен ко входам сброса счетчика остатка и счетчика-делителя и к нулевому входу триггера, единичный вход которого подключен к выходу схемы сравнения остатка. Выход устройства через второй элемент задержки подключен ко второму входу элемента ИЛИ. На чертеже представлена структурная схема устройства. Устройство содержит последовательно соединеннз 1е опорный импульсный генера тор 1, масштабный делитель частоты 2 и счетчик-измеритель 3, регистр 4, под ключенный к выходам счетчика-иамерите ля 3, счетчик-делитель 5, схему сравнения б, подключенную к выходам регис р 4 счетчика-делителя 5. Выход схемы сравнения 6 соединен с выходом устройства. Устройство также содержит умножитель частоты 7 с коэффициентом умноже ния N , элемент И 8 и счетчик остатка 9, подключенные к выходу умножителя частоты 7, делитель частоты 10 с коэффициентом деления N , входом соединенны с выходом элемента И 8, а выходом сВХОДОМ счетчика-делителя 5, регистр остатка 11, подключенный к выходам делителя частоты 2, схему сравнения остатка 12, подключенную к выходам регистра остатка 11 и счетчика остатка 9, элемент ИЛИ 13, триггер 14, элементы, задержки 15 и 16. Выход элемента ИЛИ 13 соединен с нулевым входом триггера 14 и входами сброса счетчиков 5 и 9. Единичный вход триггера 14 соединен с выходом схемы сравнения остатка 12. Вход устройства подключен ко входу элемента ИЛИ 13, входу сброса делител частоты 1О, управляющим входам регист ров 4, 11 и через элемент задержки 15 к входам сброса делителя частоты 2 и счетчика - измерителя 3. Выход устройства через элемент задержки 16 соедине с другим входом элемента ИЛИ 13. Генератор 1, делитель частоты 2, счетчик-измеритель 3, регистр 4, счетчик-делитель 5 и схема сравнения 6 образуют блок деления 17. Умножитель частоты 7, элемент И 8, счетчик остат ка 9, умножитель частоты 7, регистр остатка 11, схема сравнения остатка 12 элемент ИЛИ 13, триггер. 14, элементы задержки 15 и 16 образуют блок коррек ции остатка 18. Устройство работает следующим образом. Импульсы генератора 1 с периодом следования Т поступают на умножитель частоты 7 и делитель частоты 2, с выхода которого импульсы с периодом следования NT поступают на счетчикизмеритель 3, который за время Т (делимый период) отсчитывает в мас702 штабных единицах NT n T/t4T целых единиц. Принятое счетчикo Ki-Haмерителем 3 состояние t- переписывается входным импульсом в регистр 4, а состояние делителя частоты 2, соответствующее моменту прихода входного импульса (нескомпенсированный остаток) N IN переписывается в остатка 11. Одновременно, входным импульсом через элемент ИЛИ 13 устанавливается триггер 14 и счетчики 5 и 9 в нулевое состояние, в нульг-делитель частоты 1О и через элемент задержки 15 - делитель частоты 2 и счетчик-измеритель 3. С приходом входного импульса элемент И 8 закрывается для импульсов умножителя частоты 7 до тех пор, пока счетчик остатка 9 не заполнится до величины 14 и на схеме сравнения остатка 12 не выделится импульс сравнения, который переводит триггер 14 в состояние 1. Таким образом в следовании импульсов с выхода элемента И 8 наступает паузаСТр/К)м| что соответствует задержке по фазе счетных состояний делителя частоты 10, а значит и счетчика-делителя 5. Временное положение импульса сравнения на выходе схемы сравнения 6 (выходного импульса устройства) смесителя на указанную велич.ину. Выходным импульсом счетчик-делитель 5 и триггер 14 через элемент задериоси 16 и элемент ИЛИ 13 сбрасывается в нуль, элемент И 8 вновь оказывается закрытым для импульсов умножителя частоты 7 на времяСТо/М)Н , и коррекция фазы повторяется. Устройство обеспечивает высокую точность деления периодов следования импульсных сигналов за счет согласования коэффициента коррекции по остатку с частотой опорного генератора при заданном коэффициенте деления, утфощено почти в два раза и имеет неограниченный диапазон коэффициентов деления. В прототипе диапазон коэффициентов деления ограничивается по максимуму величиной, зависящей от Т- и минимума номинала реализуемой линии задержки о 1О МКС и г. кс, Nrriaif 100. В данном устройстве такого ограничения нет. За счет упрощения устройства среднее время наработки на отказ увеличивается по сравнению с прототипом в 1,3-1,6 раза. Увеличение точности при N 40,Тс,1О МКС, Т 79О мкс, дисир 0,1 МКС (шаг дискретизации номиналов выпускаемых линий задержки) составляет 10%. Формула изобретения Устройство для деления периодов сле дования импульсных сигналов, содержащее опорный импульсный генератор, масштабный делитель частоты, счетчикизмеритель, счетчик-делитель, схему сравнения, триггер, счетчик остатка, элемент И, элемент ИЛИ и первый элемент задержки, причем выход масштабного делителя частоты подключен ко входу счетчика-измерителя, а входы сбр са их соединены между собой, выходы разрядов счетчика-делителя подключены к первой группе входов схемы сравнения первый вход элемента И подключен к единичному выходу триггера, о т л и чающееся тем, что, с целью повышения точности работы, расширения области применения и упрощения устройства, оно содержит регистр, умножитель частоты, делитель частоты, регистр остатка, схему сравнения остатка и второ элемент задержки, причем выход опорного импульсного генератора подключен ко входу масштабного делителя частоты выходы счетчика-измерителя подключены ко входам регистра, выходы которого подключены ко второй группе входов схемы сравнения, выход которой подключен к выходу устройства, вход умножителя -частоты подключен к выходу опорного импульсного генератора, а выход - ко второму входу элемента И и 2 входу счетчика остатка, выходы разрядов которого подключены к первой группе входов схемы сравнения остатка, вторая группа входов которого подключена к выходам регистра остатка, входы KOTOpoio соединены с выходами масштабного делителя чеестоты, выход элемента И подключен ко входу делдтеля частоты, выход которого подключен ко входу счетчика-делителя, первый, вход элемента ИЛИ соединен со входом устройства, о управляющими входами регистра, регистра остатка и делителя частоты и со входом первого элемента задержки, выход которого соединен со входом сброса масштабного делителя частоты, выход элемента ИЛИ подключен к входам сброса счетчика остатка и счетчика-делителя и к нулевому входу триггера, единичный вход которого подключен к выходу схемы сравнения остатка, выход устройства через второй элемент задержки подключен ко второму входу элемента ИЛИ. Источники информации, принятые во Внимание при экспертизе 1.Авторское сввдетельство.СССР м, 255988, кл. Н 03 К 23/00, 1967. 2.Авторское свидетельство СССР 354517, кл. Н ОЗ В 19/00, ;i96D. № 3.Авторское свидетельство СССР 337947, кл. Н 03 К 23/00, 1970. № 4.Патент США N9 3970954, кл. 331-53, 1976. 5.Авторское свидетельство СССР № 3864О2, кл. G Об G 7/16,1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство для умножения частотыСлЕдОВАНия иМпульСОВ | 1979 |

|

SU817711A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ СЛЕДОВАНИЯ ИМПУЛЬСНЫХ СИГНАЛОВ | 1973 |

|

SU386402A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Автоматический следящий делитель периодов следования импульсов | 1981 |

|

SU970705A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1972 |

|

SU425315A1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-12—Подача