1

Изобретение относится к измерительной и вычислительной технике и может найти применение в устройствах различного назначения, в частности в устройствах контроля состояния механи- 5 ческих систем с вращающимися частями с помощью электронных методов анализа и измерения частотных составляющих вибраций.

Известно устройство для умножения 10 частоты следования периодических импульсов, содержащее делитель опорной частоты с коэффициентом деления, равным коэффициенту, умножения К, счетчик импульсов опорной частоты, счет- 5 чик импульсов, формирователи, запоминаихций регистр, два блока переноса и блок управления Ij

Однако это устройство характеризуется погрешностью дискретности,20 обусловленной некратностью числа N импульсов генератора опорной частоты f,,.., поступаюгху1Х в течение периода Т входной частоты fx и коэффициента К деления. В результате к кон-25 цу каждого периода TX в делителе может остаться число,, представлякадее дробную часть частного от деления N/K, что выражается в погрешности периода следования импульсов выходной ЗО

последовательности в пределе достигающем T(5tl

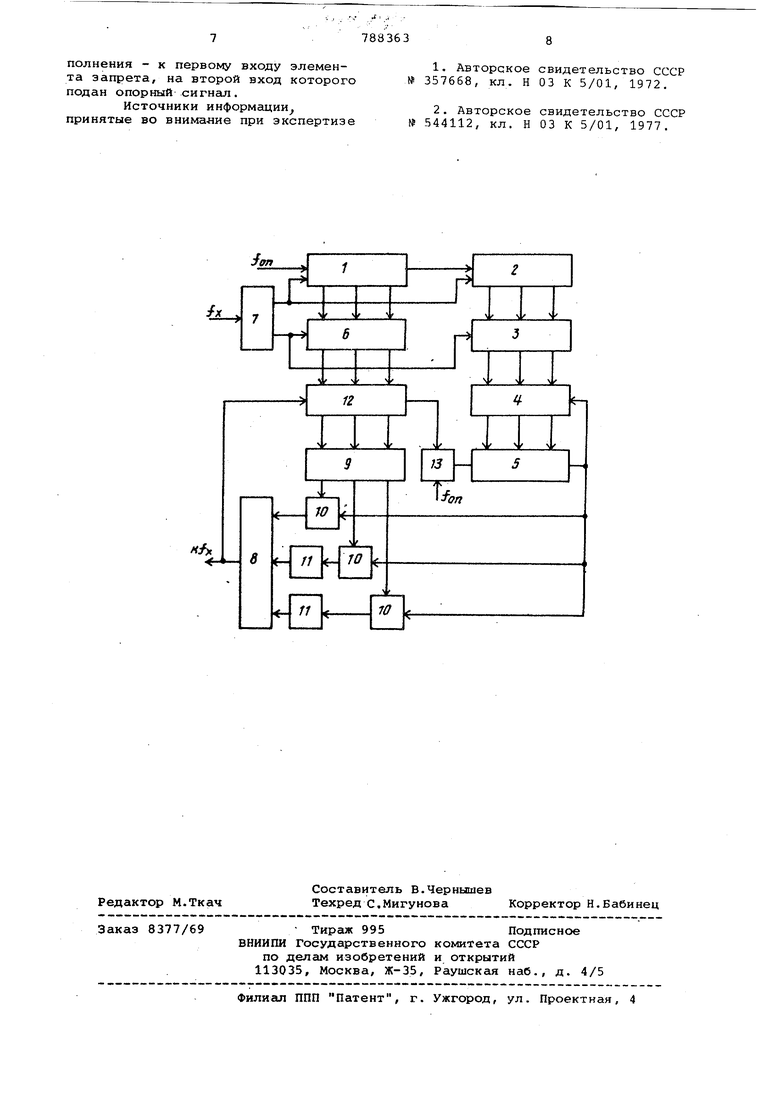

Известен также умножитель частоты следования периодических импульсов, содержа1ций делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов, счетчик импульсов опорной частоты, формирователи, запоминанз.чий регистр, два блока переноса и блок управления, в него введены дополнительный запоминактций регистр, дешифратор, элементы совпадения, линии задержки и элемент ИЛИ, причем выходы делителя опорной частоты подключены к дополнительному запоминакхдему регистру, выходы которого подключены к входам дешифратора. Выходы дешифратора соединены с первыми входами элементов совпадения, вторые входы которых объединены и подключены к выходу выходного формирователя, выход первого непосредственно, а выходы остальных через линии задержки подключены ко входам элемента ИЛИ. В устройстве для уменьшения погрешности последовательность импульсов с выхода выходного формирователя пропускается через линию с задержкой t, определяемой по состоянию дополнительного регистра дешифратором 2 . Цель изобретения - повышение точности умножения частоты. Цель достигается тем, что в умножитель частоты, содержащий делитель опорной частоты, последовательно вкл гневные счетчик импульсов, первый запоминающий регистр, блок переноса и счетчик импульсов опорной частоты, причем управляющий вход блока переноса подключен к выходу счетчика импульсов опорной частоты, а также вто рой запоминаю1дий регистр, входы кото рого подключены к выходам делителя опорной частоты, блок управления, на вход которого подан входной сигнал, первый выход соединен с установочными входагли делителя опорной частоты и счетчика импульсов, второй выход со входами записи регистров, элемент ИЛИ, линии задержки, элементы совпадения и дешифратор, выходы которого соединены с первыми входами элементо совпадения, вторые входы которых объ динены и подключены к выходу счетчик импульсов опорной частоты, выход пер вого элемента совпадения непосредственно,а выходы остальных через линии задержки подключены ко входам элемен та ИЛИ, введены элемент запрета, выход которого подключен к счетному входу счетчика импульсов опорной час тоты, и сумматор по модулю коэффициента умножения, входы которого подключены к выходам второго запоминающего регистра, тактовый вход - к вых ду элемента ИЛИ, выход - ко входам дешифратора, а выход переполнения - к первому.входу элемента зап рета, на второй вход которого подан опорный сигнал. На чертеже представлена структурная электрическая схема цифрового умножителя частоты. Устройство содержит делитель 1 опорной частоты с коэффициентом деления К, счетчик 2 импульсов, образу емых при делении, первый запоминающий регистр 3, блок 4 переноса, счет чик 5 импульсов опорной частоты, вто рой зaпo ИнaюIs ий регистр 6, блок 7 управления, элемент ИЛИ 8, дешифратор 9, элементы 10 совпадения, линии 11 задержки, сумматор 12 по моду лю коэффициента умножения -К и элемент 13 запрета. Первый выход блока 7 управления подключен к установочным входам делителя 1 опорной частоты и счетчика 2 импульсов, второй --К .входам заг.пси регистров 3 и 6. На вход блока 7 управления подан входной сигнал а на вход делителя 1 - опорный сигн Информационные выходы делителя 1 подключены (с входам регистра 6, выхо ды которого подключены к входам сумматора 12, тактовый вход которого подключен к выходу элемента ИЛИ 8, выход переполнения - к первому входу элемента 13 запрета, на второй вход которого подан опорный сигнал, выходы суммы - к входам дешифратора 9. Информационные выходы счетчика 2 импульсов подключены к входам регистра 3, выходы которого через -блок 4 переноса подключены к счетчику 5 импульсов опорной частоты. Тактовый вход счетчика 5 импульсов подключен к выходу элемента 13 запрета, к управляющему входу блока 4 переноса и к объединенным входам элемента 10 совпадения, первые входы которых подключены к выходам дешифратора 9. Выходы элементов 10 совпадения (первого непосредственно, а остальных через линии 11 задержки) подключены к входам элемента ИЛИ 8. Устройство работает следующим образом. Каждый импульс умножаемой частоты fx поступает на вход блока 7 управления, в котором формируется импульс записи информации в регистры 3 и 6 и импульс установки в нулевое состояние делителя 1 и счетчика 2. Импульсы с выхода делителя 1, частота следования которых равна fgn/K, подаются на вход счетчика 2. За один период Т)( умножаемой частоты f на вход счетчика 2 поступает число импульсов, равное При этом в делителе 1 к концу п риода TX образуется остаточное число т, обусловленное некратностью числа N импульсов опорной частоты, поступивших На вход делителя 1 за время Т j , коэффициенту деления К(). Число Ny после поступления очередного импульса умножаемой частоты f переписывается в регистр 3, одновременно (этим же сигналом) число m из делителя 1 переписывается в регистр 6 и поступает на вход накапливающего сумматора 12. Импульсы опорной частоты непрерывно поступают через элемент 13 запрета на вход счетчика 5 импульсов опорной частоты, который работает в режиме вычитания и уменьшает записанное в нем число. Как только состояние всех триггеров счетчика станет нулевым, на выходе его появляется импульс, который, поступая на управляющий вход блока 4 переноса, осуществляет перенос числа NK из регистра 3 в счетчик 5. В результате на выходе счетчика 5 образуется последовательность импульсов с периодом (в случае ni 0) . оп--Однако, если , период импульсов на выходе счетчика 5 оказывается меньше требуемого значения и величина ОадОк -: опрнде.пяйТСй ;-«с::-;-м т.Т - - Т -Т Т К к к

Отсюда

,т- о„Таким образом, если увеличить период следования импульсов на выходе счетчика 5 на величину - Т, , то погрешность дискретности будет уменьшена. Для этого необходимо задержать первый импульс с выхода счетчика 5 на время Топ , второй - третий - на т.д. В этом случае период следования импульсов на выходе устройства будет иметь значение

Г„

в ы X

Корректировка периода выходной импульсной последовательности осуществляется следующим образом.

Первый импульс с выхода счетчика 5 поступает на входы элементов 10 совпадения. Дешифратор 9 анализирует состояние сумматора 12, на выходах суммы которого будет число т, и выдает разрешающий потенциал на вход соответствующего элемента 10 совпадения. Число выходных шин дешифратора 9 определяется тем, во сколько п раз необ.ходимо уменьшить погрешность дискретности периода на выходе устройства, и может достигать значения К. При этом, если , то разрешающий потенциал появляется на первом входе того элемента 10 совпадения, который непосредственно связан со входом элемента ИЛИ 8. При К/п m .2К/п разрешающий потенциал появляется на шине дешифратора 9, связанный с элементом 10 совпадения, выход которого соединен с элементом ИЛИ 8 через линию 11 задержки с временем задержки Toii/fi при 2 соединение происходит через линию 11 задержки с временем задержки 2 и т.д. Таким образом, первый импульс на выходе устройства появится с задержкой, пропорциональной значению числа т. Поступая на тактовый вход накапливающего сумматора 12 этот импульс прибавляет число m к сумме и на выходах суммы сумматора 12 появляется число т. Состояние дешифратора 9 изменяется и второй импульс с выхода счетчика 5 получает задержку, пропорциональную 2т, третий - пропорциональную 3т, четвертый - 4т и т.д. Если на каком-либо этапе работы устройства число im, где i - номер очередного импульса, превысит число К, то на выходе переполнения сумматора появляется импульс переполнения, который означает, что следугадий импульс с выхода счетчика 5 необходимо задержать на величину, большую , чем Тол. Элемент 13 запрета по сигналу переполнения запрещает о:„:1Ш импульс последовательности .

что эквивалентно задержке очередного импульса с выхода счетчика 5 на величину Тд„ . С помощью дешифратора 9, элементов 10 совпадения и ли1чий 11 задержки осуществляется дополнительная задержка этого импульса.на величину, пропорциональную остатку числа в сумматоре КАналогичным образом осуществляется коррекция временного положения последующих импульсов и при

m + i,rri К

элемент. 13 запрета опять исключает один импульс из последовательности fc, на входе счетчика 5.

Таким образом, период повторения импульсов на выходе элемента ИЛИ 8 будет определяться, с учетом максимальной погрешности, выражением

Т Т

т °

8ЫХ 1

т.е. максимальная погрешность дискретности уменьшается.

Формула изобретения

Цифровой умножитель частоты, со0держащий делитель опорной частоты, последовательно включенные.счетчик импульсов, первый запоминающий регистр, блок переноса и счетчик импульсов опорной частоты, причем управля5ющий вход блока переноса подключен к выходу счетчика импульсов опорной частоты, а также второй запомин аюашй регистр, входы которого подключены к выходам делителя опорной частоты,

0 блок управления, на вход которого подан входной сигнал, первый выход соединен с установочными входами делителя опорной частоты и счетчика импульсов, второй выход - со входами записи первого и второго запоминающих

5 регистров, элемент ИЛИ, линии задержки, элементы совпадения и дешифратор, выходы которого соединены с первыми входами элементов совпадения, вторые входы которых объединены и подключеOны к выходу счетчика импульсов опорной частоты, выход первого элемента совпадения непосредственно, а выходы остальных через линии задержки подключены ко входам элемента ИЛИ, о т5личающийся тем, что, с целью повышения точности умножения, в него введены элемент запрета, выход которого подключен к счетному входу счетчика импульсов опорной частоты, и накапливающий сумматор по модулю

0 коэффициента умножения, входы которого подключены к выходам второго запоминающегося регистра, тактовый вход к выходу элемента ИЛИ, выход сумуы ко входам дешифратора, а вчход пера5

полнения - к первому входу элемента запрета, на второй вход которого подан опорный сигнал.

Источники инфopмaции принятые во внима-ние при экспертизе

1.Авторское свидетельство СССР № 357668, кл. Н 03 К 5/01, 1972.

2.Авторское свидетельство СССР № 544112, кл. Н 03 К 5/01, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU945964A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

/X

Авторы

Даты

1980-12-15—Публикация

1979-01-24—Подача