Изобретение относится к вычисли тельной технике, а более точно к цифровым умножителям сигналов, заданных .число-импульсной последовательностью, и может быть использова в устройствах измерительной техники как масштабное устройство, в устрой вах автоматики:и вычислительной тех ники как умножитель частоты на коэф фициент умножения, представленный десятичной дробью. Известно устройство умножения цифровых частот, содержащее три сдвиговых регистра, схему управления, счетчики, два компаратора, реверсивный счетчик, логические cxeNW II. Недостатком известного умножител является его сложность. Известно также устройство для умножения частоты импульсов, содержащее двоичный счетчик, схему и три гер управления, линии задержки, шиф ратор числа, представляющего числитель коэффициента, умножения, и шифратор числа, представляющего знаменатель коэффициента умножения 2}. Недостатком известного умножител частоты импульсов является его слож ность из-за необходимости двух шифраторов для числа числителя и знаменателя и большая неравномерность , выходной частоты, которая представлена в виде отдельных пачек импульсов, отстоящих друг от друга на расстоянии в сотни и тысячи периодов исходной частоты. Цель изобретения - повышение равнсмерности выходной частоты. Это достигается тем, что в умножителе частоты импульсов, содержащем элемент ИЛИ и п-разрядный двоичнодесятичной счетчик, каждыйразряд которого состоит из триггерной декады, вход которой подключен к входной шине, одновибратора, дешифратора и элементов И, в каждом разряде двоично-десятичного счетчика первые входы элементов И объединены и подключены через одновибратор к входной шине, второй вход каждого из элементов И подключен к прямому выходу соответствующего триггера декада, третьи входы второго, третьего и четвертого элементов И объединены и подключены к инверснсялу выходу первого триггера декады, четвертый выход третьего элемента И - к инверсному выходу второго триггера декады, а выходы эл ментов И - к входам дешифратора.

причем выходы дешифраторов всех разрядов двоично-десятичного счетчика соединены с входами элемента ИЛИ.

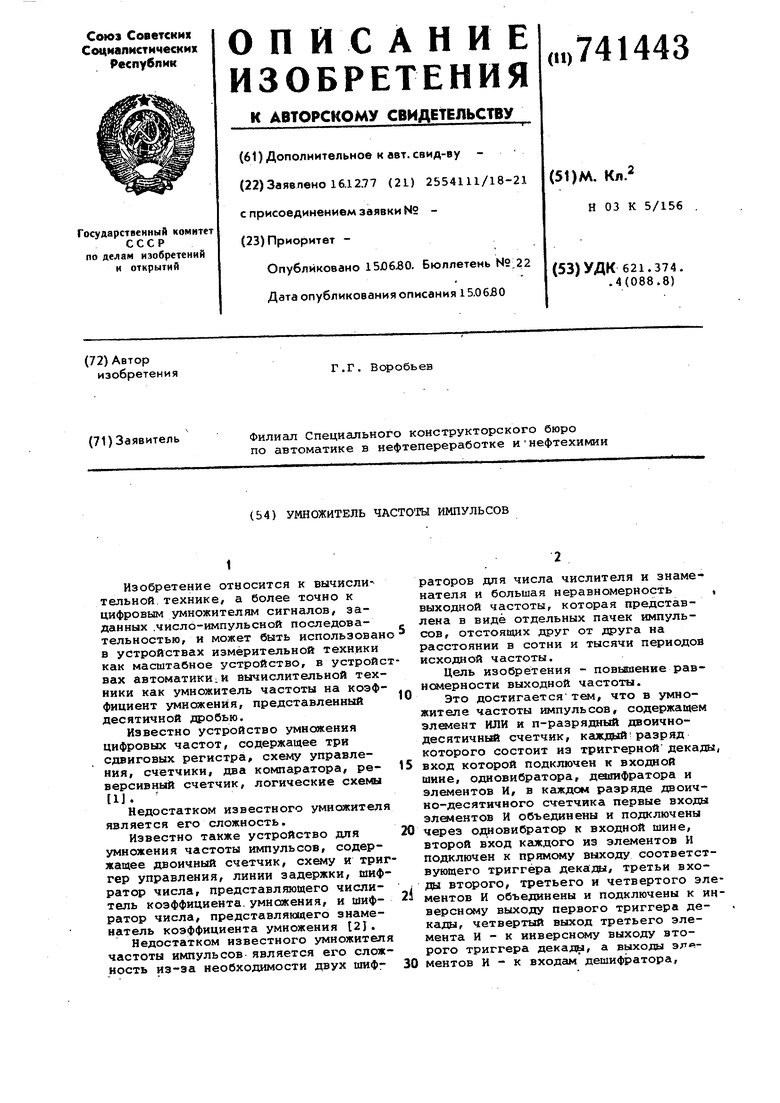

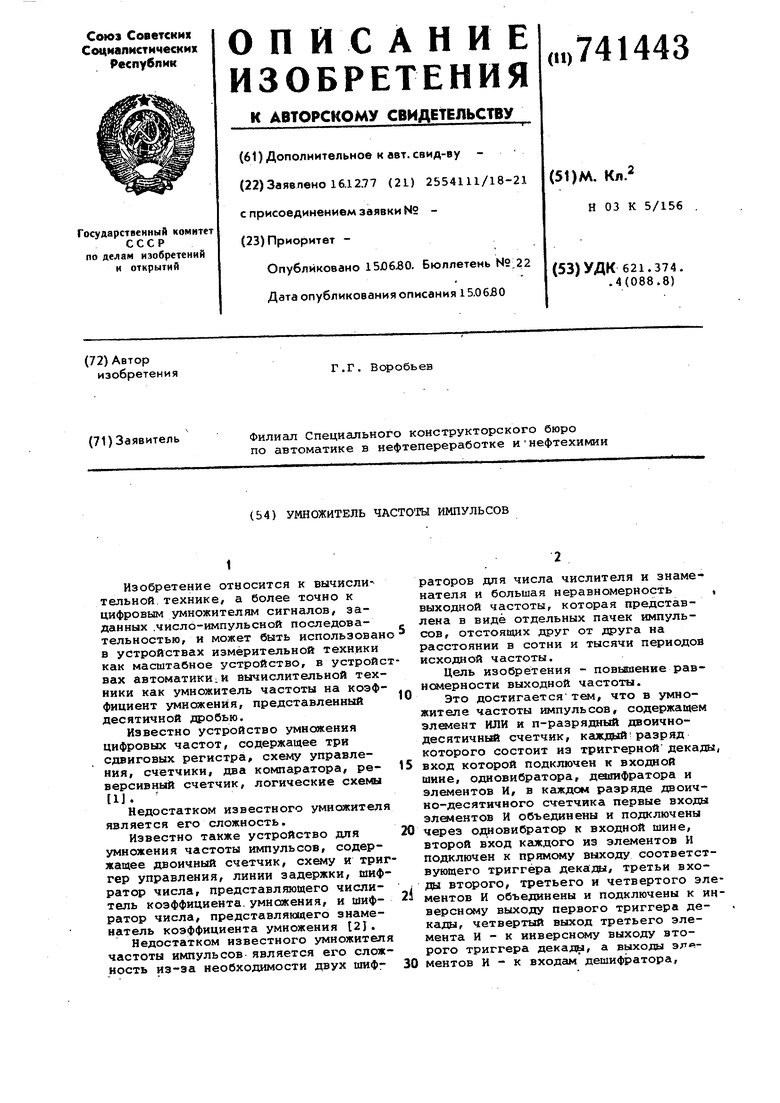

На фиг. I представлена структурная электрическая схема умножителя частоты импульсов; на фиг. 2 - один из вариантов выполнения даиифратора.

Устрсмйство содержит п-разряде1ый двоично-десятичный счетчик, каждый разряд -которого состоит из декады 1 на триггерах 2 - 5 в коде 1-2-4-8. Связи между триггерами не показаны. К входу каждой декады Г подключен о 1новибратор 6, выход которого подсодинен к первым входам элементов И 710. Втсфые входа элементов И 7 - 10 подключены соответственно к прямым выходам триггеров 2-5. Третьи входаа элементов И 8 - 10 подключены к инверсному выходу триггера 2. Четвертый вход элемента И 9 подсоединен к инверсному выходу триггера 3. Выходы элементов И 7-10 подключены к входу дешифратора 11.Выходы дешифраторов 11 всех разрядов объединены элементом ИЛИ 12.

дешифратор. 11 преобразует динамический код декады 5-2-1-1- в динамический десятичный код н состоит из элементов ИЛИ 13-18, переключателя - 19 с контактами 20-29. Лервый вход дешифратора 11 соединен с контактом 25 и с входами элементов ИЛИ 15-18, выходы которых подключены соответственно к контактам 26-29, второй еход димифратора 11 - с контактом 22 и входами элементов ИЛИ 13,14,16,17 (выходы элементов ИЛИ 13 - 14 подключены к контактам 23 и 24), третий вход дешифратора 11 - с контактом 21 и с входами элементов ИЛИ 15, 14, 18 четвёртый вход дешифратора 11 - с входами элементов ИЛИ 13, 14,17, 18. Работа умножителя происходит следующим образом.

С помощью переключателя 19 устанавливают коэффициент умножения входной частоты. П еключатель 19 первой декады устанавливает десятые доли второй декады - сотые доли и т.д. коэффициента умножения.

При подаче на вход устройства частоты i , которую необходимо умножить на коэффициент К,начнет работат двоично-десятичный счетчик.

Одновибратор 6 формирует импульсы {входной частоты на определенную длительность.

Следовательно, на выходе элемента И 7 присутствует пять импульсов из десяти: частоты f, поскольку совпадение единичных потенциалов сигналов i и Q (Чд -прямой выход триггера 2 возможно только для всех нечетных импульсов.

Подобным образом срабатывают и остальные элементы И 8 - 10, на выходных шинах которых присутствуют шлпульсы кода 5-2-1-1.

Например, для К в 0,5432 с переключателя 19 первого разряда на элемент ИЛИ 12 поступает пять импульсов из каждых десяти входных импульсов f. С переключателя 19 второго разряда на элемент ИЛИ 12 поступает четыре импульса из каждых ста входных импульсов. С переключателя 19 третьего разряда на элемент ИЛИ 12 поступает три импульса из каждой тысячи импульсов частоты f . С переключателя 19 четвертого разряда на элемент ИЛИ поступит два импульса из каждых десяти тысяч импульсов частоты .

Общее количество импульсов на выходе элемента ИЛИ 12 после прохождени через двоично-десятичный счетчик 10000 импульсов частоты

5-1000 + 4-100+3-10-1-2 5432,

т-е. ffeb,x Чходо, 0,5432.

Таким образом, предложенный умножитель частоты импульсов позволяет производить умножение входной частоты на коэффициент, выраженный десятичной дробью. В нем отсутствует дополнительный шифратор для знаменателя дроби, частота импульсов на его выходе практически равномерна. Все это расширяет возможности применения умножителя. Данное устройство возможно применять известное устройство применять нельзя, а именно, в устройствах автоматики для масштабирования входных сигналов, где появление пачек импульсов недопустимо. Формула изобретения

Умножитель частоты импульсов, содержащий элемент ИЛИ и п-разрядный двоично-десятичный счетчик, каждый разряд которого состоит из триггерной декады, вход которой подключен к входной шине, одновибратора, дешифратора и элементов И, Отличающийся тем, что, с целью повышения равномерности выходной частоты в каждом разряде двоично-десятичного счетчика первые входы элементов И объединены и подключены через одновибратор к входной шине, второй вход каждого из элементов И подключен к прямому выходу соответствующего триггера декады, третьи входы второго, третьего и четвертого элементов И объединены и подключены к инверсному выходу первого триггера декады, четвертый выход третьего элемента И к инверсному выходу второго триггера декады, а выходы элементов И - к входам дешифратора, причем выходы дешифраторов всех разрядов двоично-десятичного счетчика соединены с входами элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Патент Франции 2249500, кл. н 03 К 5/156, 1975.

2.Авторское свидетельство СССР

№ 417896, кл. Н 03 К 5/00, 1975 (прототип).

J раЗр/10

П- разрл1

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| ЧАСТОТОМЕР ДЛЯ ЭНЕРГОСИСТЕМ И ЭЛЕКТРОСТАНЦИЙ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362174C1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Цифровой частотомер | 1982 |

|

SU1190285A1 |

| Пересчетное устройство | 1982 |

|

SU1051698A1 |

Авторы

Даты

1980-06-15—Публикация

1977-12-16—Подача