Изобретение относится к импульсной технике.

Целью изобретения является повышение надежности работы и улучшение характеристик формируемой- псевдослучайной последовательности.

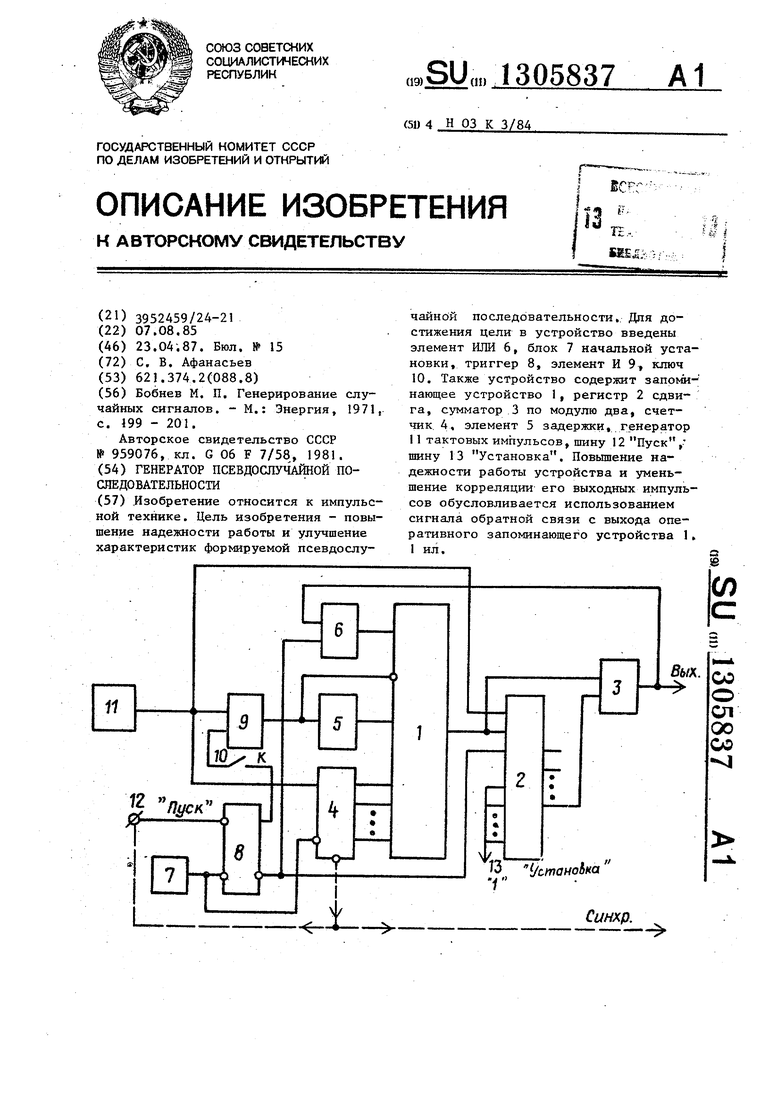

На чертеже представлена функциональная схема генератора псевдослучайной последовательности;

Генератор псевдослучайной последо-fo ИЛИ 6 и на третьем (информацион- вательности содержит, оперативное за- ном) входе оперативного запоминаю- поминающее устройство Ц выход которого соединен с входом последователь- : ного сдвига регистра 2 сдвига, выщего устройства 1 устанавливается уровень логической 1, Одновременно уровень с инверсного выхода триг- ход соответствующего разряда которо- 15 гера 8 переводит регистр 2 сдвига по го соединен с первым входом сумматора 3 по модулю два, счетчик 4, элемент 5 задержки, элемент ИЛИ 6, блок 7 начальной установки, триггер 8, элемент И 9, ключ 10, генератор 11 тактовых импульсов, шину Пуск 12, шину Установка 13. Выход генератора 11 тактовых импульсов соединен с входом Синхронизации регистра 2 сдвига и счетным входом счетчика 4, выхо- З держимое счетчика 4, а при разомк- ды которого соединены с адресными нутом ключе 10 тем же импульсом входами оперативного запоминающего через время, определяемое элементом устройства 1, входы чтения и записи задержки 5, логическая; с выхода которого соединены с выходом и вхо- элемента ИЛИ 6 записывается в ячей- дом соответственно элемента 5 задерж- 30 ку оперативного запоминающего уст- ки. Шина ПУСК 12 соединена с S- ройства 1, адрес которой определяется кодом счетчика 4. Для записи 1 по всему требуемому массиву оперативного запоминающего устройства 1, j временной интервал между сигналом, вырабатываемым блоком 7 начальной

его третьему входу в режим записи, Тактовые импульсы с выхода генератора 11 тактовых импульсов поступают на вход устройства и в регистр 2 20 сдвига заносится параллельный код, предварительно установленный на его входах параллельного занесения по шине Установка 13, Каждый тактовый импульс увеличивает на единицу совходом триггера 8 прямой выход которого соединен с входом ключа 10, выход которого соединен с первым входом элемента И 9, выход которого соединен с входом элемента 5. Информационный вход оперативного запоминающего устройства 1 соединен с выходом элемента ИЛИ 6, первый вход которого соединен с входом управления регистра 2 сдвига и инверсным выходом триггера 8, R-вход которого соединен с входом обнуления счетчика 4 и выходом блока 7 начальной установки. Выход оперативного запоминающего устройства 1 соединен с вторым входом сумматора 3 по модулю два выход которого соединен с вторым входом элемента ИЛИ 6i Выход генератора 11 тактовых импульсов соединен с вторым входом элемента И 9, Шина Установка 13 соединена с соответствующими входами регистра 2 сдвига,

.Содержимое счетчика 1 при перехоГенератор псевдослучайной последо- 55 ле. устройства в основной режим рабо- вательности работает следующим обра- ты может быть произвольным, так как зом,массив оперативного запоминающего

При включении питания сигнал с устройства 1 содержит однородную ин- выхода блока 7 начальной установки, формацию (Все 1).

установки, и сигналом пуска по пш- не Пуск 1 2, переводящим устройство в режим формирования псевдослучайной 40 последовательности, должен быть не

менее (N-M) --, где М - емкость

г

счетчика 4; 7- - период следования г

45 тактовых импульсов; N - общая разрядность устройства. В этом случае логическая 1 записана в массив оперативного запоминающего устройства 1 объемом (N-M), Таким образом, при

50 включении питания обеспечивается занесение исходной информации в оперативное запоминающее устройство 1,

поступающий на вторые (установочные) входы счетчика 4 и триггера 8, устанавливает последние в нулевое состояние, чем обеспечивается вспомогательный режим работы генератора псевдослучайной последовательности.

Единичный потенциал с второго (инверсного) выхода триггера 8 по - ступает на первый вход элемента

щего устройства 1 устанавливается уровень логической 1, Одновременно уровень с инверсного выхода триг- гера 8 переводит регистр 2 сдвига по держимое счетчика 4, а при разомк- нутом ключе 10 тем же импульсом через время, определяемое элементом задержки 5, логическая; с выхода элемента ИЛИ 6 записывается в ячей- ку оперативного запоминающего уст- ройства 1, адрес которой определяется кодом счетчика 4. Для записи 1 по всему требуемому массиву оперативного запоминающего устройства 1, временной интервал между сигналом, вырабатываемым блоком 7 начальной

его третьему входу в режим записи, Тактовые импульсы с выхода генератора 11 тактовых импульсов поступают на вход устройства и в регистр 2 сдвига заносится параллельный код, предварительно установленный на его входах параллельного занесения по шине Установка 13, Каждый тактовый импульс увеличивает на единицу соустановки, и сигналом пуска по пш- е Пуск 1 2, переводящим устройство в режим формирования псевдослучайной последовательности, должен быть не

менее (N-M) --, где М - емкость

г

четчика 4; 7- - период следования г

тактовых импульсов; N - общая разрядность устройства. В этом случае логическая 1 записана в массив оперативного запоминающего устройства 1 объемом (N-M), Таким образом, при

включении питания обеспечивается занесение исходной информации в оперативное запоминающее устройство 1,

При замкнутом ключе 10 при включении питания в регистр 2 сдвига также заносится заведомо не нулевой код с входов параллельного занесения по шине Установка 13, Однако нулевым потенциалом с первого (прямого) выхода триггера 8 тактовые импульсы блокируются на элементе И 9, оперативное запоминающее устройство 1 по второму входу находится постоянно в режиме чтения, а на счетчике 4 происходит последовательный перебор кодов. Таким образом, при замкнутом ключе 10 при включении питания в оперативном запоминающем устройстве 1 сохраняется произвольная информация, но в целом при включении питания в устройстве иключается появление информации типа Все нули.

На чертеже пунктирными линиями показаны возможные связи, позволяю- щие осуществить самоорганизацию работы генератора псевдослучайной последовательности. При зтом выход переполнения счетчика 4 надо сое- дйнить с первым S-входом триггера 8, вместо шины Пуск 12, и с выходом синхронизации устройства. В этом случае, при включении питания, блок 7 начальной установки выдает импульс обнуляюпшй триггер 8 и счетчик 4. Последний последовательно проходит (N-M) состояний и по сигналу его переполнения триггер 8 устанавливается в единичное состояние, переводя уст- ройство в основной режим работы. Импульс переполнения счетчика 4 по цепи синхронизации поступает во внешнюю цепь и может служить сигналом запуска устройства, использующего ге нератор псевдослучайной последовательности.

По приходу сигнала по шине Пуск 12 триггер 8 устанавливается в ничное состояние и ооеспечивает основной режим работы устройства. Нулевой потенциал с инверсного выхода триггера 8 переводит регистр 2 сдвига в режим сдвига, а нулевой и еди- ничный потенциалы с соответствующих выходов триггера 8 открывают элемент ИЛИ 6 и элемент И 9 (при замкнутом ключе 10). Тактовые импульсы поступают на выход элемента И 9. Каждый тактовый импульс увеличивает на единицу содержимое счетчика 4, тем самым изменяя адрес опрашиваемой ячейки оперативного запоминающего устройства 1,.Тем же импульсом осуществляется считывание выбранной ячейки на первый вход (вход последовательного сигнала) регистра 2 сдвига и сдвиг числа, -записанного в регистре 2 сдвига. На выходе сумматора 3 по модулю два формируется уровень, определяемый состоянием выхода оперативного запоминающего устройства и соответствующего (последнего) разряда регистра 2 сдвига,, подключенных к его выходам.

Через время,, определяемое элементом 5 задержки, происходит запись сигнала с выхода сумматора 3 по модулю два в опрошенную ячейку оперативного запоминающего устройства 1. Во время работы счетчик 4 проходит / (N-M) состояний и на вход последовательного сдвига регистра 2 сдвига поступает последовательность двоичных чисел, записанных в оперативном запоминающем устройстве 1 на N так- тов ранее, так как разрядность регистра 2 сдвига выбирается равной М, В результате работа, выполняемая оперативным запоминающим устройством 1 при данной организации процессов записи и считывания, аналогична работе (N-M) разрядного регистра . сдвига, а всю схему устройства можно рассматривать как общий N-разрядный регистр сдвига, в цепь обратной связи которого включен сумматор по модулю два

Использование в устройстве одного из сигналов обратной связи с выхода оперативного запоминающего устройства 1 позволяет повысить надежность работы генератора псевдослучайной последовательности и уменьшить корреляцию его выходных импульсов.

Формула изобретения

Генератор псевдослучайной последовательности, содержащий оперативное запоминающее устройство, выход которого соединен с входом последовательного сдвига регистра сдвига, выход соответствующего разряда которого соединен с первым входом сумматора по модулю два, генератор тактовых импульсов, выход которого соединен с входом синхронизации регистра и счетным входом счетчика, выходы которого соединены с адресными входами оперативного запоминающего

устройства, входы чтения и записи которого соединены с выходом и входом соответствующего элемента задержки, о тлич ающи й ся тем, что, с целью повышения надежности работы генератор и улучшения характеристик формируемой им псевдослучайной последовательности, в него введены элемент ИЛИ, блок начальной установки, триггер, элемент И, ключ причем, шина Пуск соединена с S- входом триггера, прямой выход которого соединен через ключ с первым входом элемента И, выход которого соединен с входом элемента задержки информационный вход оперативного

Редактор Г, Гербер

Составитель Ю. Бурмистров

Техред М.Ходанич Корректор А. Обручар

Заказ 1464/54 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

запоминающего устройства соединен с выходом элемента ИЛИ, первый вход которого соединен с входом управления регистра сдвига и инверсным выходом триггера, R-вход которого соединен с входом обнуления счетчика и выходом блока начальной .установки,. выход оперативного запоминающего устройства соединен с вторым входом сумматора по два, выход которого соединен с вторым входом элемента ИЛИ, выход генератора тактовых импульсов соединен с вторым входом элемента И, шина Установка соединена с соответствующими входами разрядов регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| Устройство для контроля блоков памяти | 1987 |

|

SU1437925A1 |

| Генератор случайной последовательности | 1989 |

|

SU1640687A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Устройство для передачи информации псевдослучайными сигналами | 1986 |

|

SU1392625A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

.Изобретение относится к импульсной технике. Цель изобретения - повышение надежности работы и улучшение характеристик формируемой псевдослучайнбй последовательности.. Для достижения цели в устройство введены элемент ИЛИ 6, блок 7 начальной установки, триггер 8, элемент И 9, ключ 10. Также устройство содержит запоьш-; нающее устройство 1, регистр 2 сдвига, сумматор 3 по модулю два, счетчик. 4. элемент 5 задержки, генератор 11 тактовых импульсов, шину 12 Пуск, шину 13 Установка. Повышение надежности работы устройства и уменьшение корреляции его выходных импульсов обусловливается использованием сигнала обратной связи с выхода оперативного запоминающего устройства 1, 1 ил. 2 je 11 bxJ (Л с бб/Л. со о ел оо со -vl g 6 LJ rv -е х/. 3 t/ctnOHO KO 1 Синхр. -

| Бобнев М | |||

| П | |||

| Генерирование случайных сигналов | |||

| - М.: Энергия, 1971, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

| Генератор псевдослучайной последовательности | 1981 |

|

SU959076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-08-07—Подача