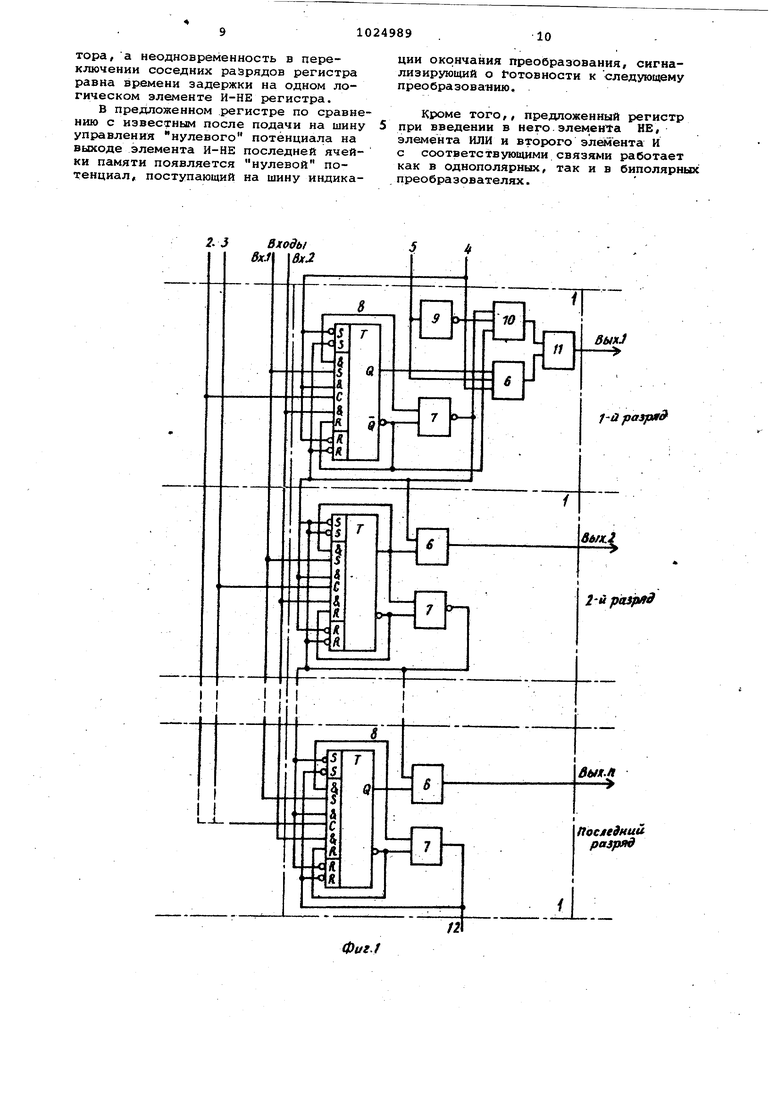

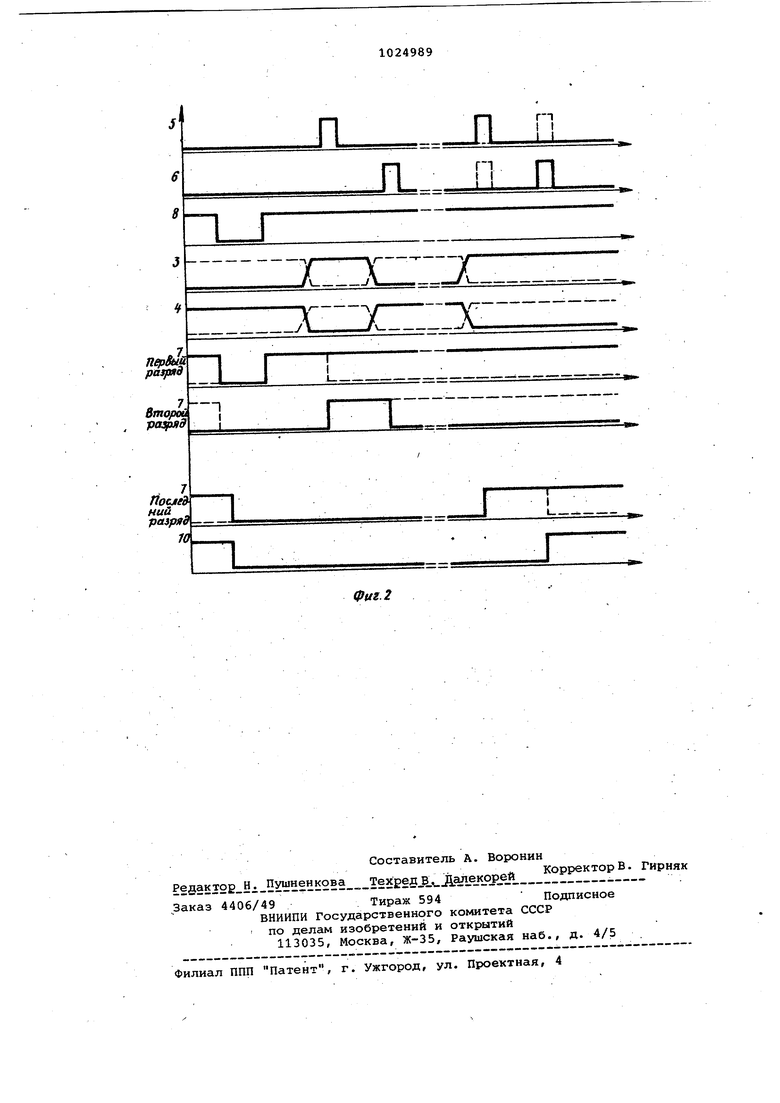

Изобретение относится к вычислительной технике и автоматике и пред назначено для использования в анало цифровых преобразователях поразрядн го уравновешивания. Известно ycTpoiftcTBo управления преобразователем аналог-код с пораз pядньпvt уравновешиванием, каждый раз ряд которого содержит управляющий эле мент И-НЕ и два триггера, состоящие из одного элемента И-ИЛИ-НЕ с входам триггерной связи и установки, элеме та И-НЕ для первого триггера и элемента НЕ для второго триггера, прич выход управляющего элемента И-НЕ в каждом разряде регистра соединен со входом триггерной связи элемента . элемента И-ИЛИ-НЕ первого триггера и с первым входом -установки элемент И-ИЛИ-НЕ второго триггера, первый вход - с выходом элемента НЕ второг триггера предыдущего разряда, второ вход - с первым входом установки эл мента И-ИЛИ-НЕ первого триггера пре дыдущего разряда и с выходом элемен та И-ИЛИ-НЕ второго триггера данног .разряда, второй вход установки эле мента И-ИЛИ-НЕ которого соединен с выходом элемента И-ИЛИ-НЕ первого триггера, второй вход установки эле мента И-ИЛИ-НЕ которого соединен с выходом схегуи стробирования тактовы сигналом сигнала с элемента сравнения l . Недостатком данного устройства является ТО , что для уменьшения времени приема сигнала со схемы сравнения и, соответственно, неодновременности при переключении соседних разрядов необходимо по тактовой шине подавать на устройство короткие сигналы длительностью 3t - 4t, где t время задержки одного логического элемента. При более коротких сигнала появляется сбой в работе устройства а при более длинных - увеличивается неодновременность в переключении соседних разрядов, что в,свою очередь , вызывает появление выбросов в переходном процессе преобразователя .и увеличивает время установления переходного процесса в нем, кроме того, при использовании широкого сигнала снижается надежность работы регистра из-за возможного воздействия на его входы импульсных помех и шумов с выхода компаратора в течение этого времени. Кроме того, данный регистр предназначен для работы только в однополярных АЦП. Известно уравновешивающее устройство для аналого-цифрового преобразователя, содержащее в каждом разряде три RS-триггера и трехвходовую схему И-НЕ, причем в каждом разряде нулевой выход первого триггера соединен с входомустановки в нуль второго триггера, вход установки в единицу - с единичным выходом второго триггера, выход схемы И-НЕ соединен со вторыми входами установки в единиг цу всех трех триггеров, первый вход с единичным выходом третьего триггера предыдущего разряда, второй вход - с нулевым выходом третьего триггера последующего разряда, третий вход с тактовой шиной в нечетных разрядах и через инвертор - с тактовой шиной в четных ргзрядах, первый вход установки в нуль основного триггера всех разрядов соединен с выходом схемы сравнения, а второй вход установки в единицу второготриггера, второй вход установки в нуль первого и третьего триггеров всех разрядов соеди- нены с шиной установки в исходном состоянии С23 Недостатком данного устройства является то, чтъ для ее построения необходимо 7 логических элементов на один разряд, кроме того схема предназначена для работы только в однополярных аналого-цифровых преобразователях (АЦП). Наиболее близким к изобретению по технической сущности является регистр который содержит .в каждом разряде выполненный на двух элементах И-ИЛИНЕ RS-триггер с асинхронными инвёрсами и синхронизируемыми прямыми входами, элемент И и элемент ИЛИ, причем в каждом разряде прямые S-вход и R-вход RS-триггера соединены соответственно с первой и второй входными шинами регистра, прямой С-вход с -тактовой шиной, прямой выход - с nepBbBvi входом элемента И, инверсные S-вход и R-вход - с вторым входом элемента И, выход которого соединен с выходной шиной данного разряда, а та:кже в каждом разряде прямой и инверсный выходал RS-триггера соединены со входами элемента ИЛИ, выход которого соединен с вторым С-вкодом RS-триггера этого же разряда и с инверсными S и R -входами RS-триггера последующего разряда, з . Недостатками известного регистра являются низкие быстродействие и надежность, а также ограниченность применения, так как он предназначен . только для работы в АЦП, у которых время срабатывания цифро-аналогового преобразователя и компаратора значительно меньше времени рассасывания неосновных носителей транзисторов развертывающего регистра. Кроме того, известный регистр предназначен для работы только в однополярных АЦП. Целью изобретения является повыше ние быстродействия регистра. Поставленная цель достигается тем, что в регистр, содержащий ячейки памяти, каждая из которых состоит из RS-триггера и элемента И, первый вход которого соединен с первым выходом и с первым S-входом RS-триггера,. вторые и третьи S-входы RS-тригт геров ячеек пг1мяти являются входами регистра, С-входы RS-триггеров нечетных ячеек памяти соединены с первой тактовой шиной, С-входы RS- триг JrepoB четных ячеек памяти соединены со второй тактовой шиной, выход каждого элемента И ячеек памяти, кроме /выхода элемента И первой ячейки памяти, является выходом регистра, шину сброса, соединенную со вторым входом элемента И первой ячейки памяти, и шину управления, в нем в каждую ячейк памяти введен элемент И-НЕ, а в пер-у вую ячейку Пс1мяти дополнительно введены элементы НЕ, элемент ИЛИ и допол нительный элемент И, причем выходы ос новного и дополнительного элементов И первой ячейки памяти соединены со входами ее элемента ИЛИ, выход элемен та И перэой ячейки является первым выходом регистра, третий вход основного элемента И и вход элемента НЕ первой ячейки памяти соединены с шино управления, выход элемента НЕ соеди иен с первым входом дополнительного элемента И первой ячейки памяти, вто рой и третий входы дополнительного элемента И первой,ячейки памяти сое динены соответственно со вторым -выходом RS-триггера и с выходом элемен та И-НЕ, входы элемента И-НЕ каждой ячейки памяти соединены соответствен но с выходами RS-триггеров данной ячейки памяти, выход элемента И-НЕ каждо ячейки памяти соединен со вторым входом элемента И, счетвертьм и с п тьм S-входами, с первым,R-входом RS-триггера последующей ячейки памят с шестым S-входом и со вторым R-SXO- дом RS-триггера данной.ячейки памяти На фиг. 1 - изображена функционал ная схема предложенного регистра; на фиг. 2 - временная диаграмма, поясни ющая работу регистра. Регистр (фиг. 1) содержит ячейки 1 памяти, тактовые шины 2-3, шину 4 сброса и шину 5 управления. Каждая ячейка 1 памяти состоит из элемента И 6, элемента И-НЕ 7, KSтриггера 8. Первая ячейка 1 памяти дополнительно содержит элемент И 10 элемент ИЛИ 11, шину 12 индикации окончания преобразования. Предложенный регистр функцйонируе следующим образом. Он имеет два режи ма работы: однополярный и биполярный в соответствии с использований в од нополярных и биополярных АЦП. в однополярном преобразователе регистр работает следующим образом. шину 5 управления подается ед ничный -потенциал, который поступает на вход элемента НЕ 9 и на вход lepBoro элемента И 6 первого разряда Нулевой потенциал с выхода элемента НЕ 9 поступает на вход элемента И 10,. с выхода которого нулевой потенциал поступает на один из входов элемента ИЛИ 11. Перед /началом работы на шину 4 по.дается потенциал нулевого уровня, который поступает на четвертый Sй;сод и второй R-вход RS-триггера 8 первой ячейки 1 памяти и на первый вход первого элемента И 6 этой ячейки памяти, с выхода которого нуле- ; вой потенциал поступает через элемент ИЛИ 11 на первый выход регистра и далее цифро-аналогового преобразователя .(не показан). Нулевой потенциал, поступающий на четвертый S-вход и второй R-вход RS-триггера 8 первой чейки 1 памяти,, устанавливают на его прямом и инверс ном выходах единичные потенциалы, которые поступают на входы элемента И-НЕ 7 Данной ячейки памяти, устанавливая на его выходе нулевой потенциал, поступающий на шестой В-вхрд и первый R-вход RS-триггера 8 первой ячейки 1 памяти. Нулевой потенциал с выхода элемента И-НЕ 7 первой ячейки памяти по,дается также на четвертый S-вход и на второй R-вход RS-триггера 8 второй ячейки 1 памяти и на второй вход элемента И 6 второй ячейки 1 памяти, с выхода элемента И ё нулевой потенциал поступает на второй выход регистра. Так же, как и в первой ячейке 1 памяти, на выходе элемента И-НЕ 7 второй ячейки памяти появляется нулевой потенциал, который поступает на шестой S-вход и на первый Н-вход RSтригГера 8 второй ячейки 1 памяти и на входы третьей ячейки 1 памяти, устанавливая на выходе ее элемента И-НЕ 7 нулевой потенциал. С выхода элемента И-НЕ 7 третьей ячейки 1 памяти нулевой потенциал поступает на входы четвертой ячейки 1 памяти и т.д. Нулевой потенциал с выхода элемента И-НЕ 7 последней ячейки 1 памяти поступает на шину индикации обнуления регистра и окончания преобразования и сигнализирует об обнулении регистра. Такш образом, после поступления нулевого .уровня на шину 4 в каждой ячейке 1 памяти трехстабильиый триггер, собранный на элементе И-НЕ 7 RS-триггере 8, установится в первое устойчивое положение, при котором иа в,ыходах RS-триггера 8 - единичные потенциалы, а на выходе элемента И-НЕ 7 - нулевой потенциал. При этом на выходах регистра устанавливаются нулевые потенциалы. Преобразование начинается с момента подачи на шину 4 единичного потенциала, который поступает на четвертый S-вход и первый R-вход и на пятый S-вход RS-триггера 8 пер вой ячейки 1 памяти и на второй вход первого элемента И 6 первой ячейки памяти, на выходе которого появляется единичный потенциал, который через элемент ИЛИ 11 поступает на пе вый выход регистра. Затем через время, равное периоду тактовых сигналов, на тактовую шину 2 подается сигнал единичного уровня, который поступает на С-входы RS-триггера 8 нечетных ячеек 1 памя ги. При этом, если измеряемая величина больше, чем уравновешивающая с выхода цифро-аналогового преобразователя, то на первом входе регистра, подключенного к прямому выходу компаратора (не показан), и на второй вход регист ра, подключенного к инверсному выходу компаратора, соответственно действуют единичный и нулевой потенциал,и если меньше, то нулевой -и единичный потенциал. Если на первом входе регистра Вх.1 единичный потенциал, а на Вх2 нулевой потенциал, то после прихода тактового импульса на С-вход НЗ-триг гера 8 первой ячейки 1 памяти на его прямом выходе сохраняется единичный потенциал, а на инверсном выходе появ ляется нулевой потенциал, поступающий на вход элемента И-НЕ 7 первой ячейки 1 памяти, на выходе которого появляется единичный потенциал, пос тупающий на шестой S-вход и на первый R-вход RS -триггера 8 первой ячейки 1 , на четвертый 8-вход и на первый R-вход и на пятый 3-вход RSтриггера а .второй ячейки 1 памяти, : а также на второй вход элемента И б второй ячейки 1 памяти, на выходе которого появляется единичный потенциал, поступающий на Вых. 2 и далее на вход цифро-аналогового преобразователя.. Нулевой потенциал с инверсного выхода RS-триггера 8 первой ячейки 1 памяти поступает также на третий S-вход, поэтому 8 дальнейшем любые изменения сигналов от компаратора на Входах регистра не смогут изменять состояние RS-триггера 8 первой ячейки 1 памяти. Так как на прямом выходе RS-триггёра 8 первой ячейки i памяти и на входах и выходах его элементов И 6 и ИЛИ 11 потенциалы не меняются, то на Вых. 1 также сохранится единичный потенциал, поступающий на вход цифро-аналогового преобразователя. Если же на Вх. 1 нулевой потен циал, а на Вх 2 единичный потенциал, то после, прихода тактового импуль da на С-вход RS-триггера 8 первой ячейки 1 памяти на его инверсном выходе сохраняется единичный потенциал, а на прямом выходе появляется нулевой потенциал, поступающий на вход элемента И-НЕ 7 первой ячейки 1 памяти, на выходе которого так же, как ив предыдущем случае, появляется единичный потенциал, поступающий на шестой З-вход и на первый R-вход RS-триггера 8 первой ячейки 1 памяти и на четвертый S-вход и на второй R-вход и С-вход RS-триггера 8 второй ячейки 1 памяти, на выходе которого появляется единичный потенциал, поступающий на Вых. 2 и далее на вХод цифро-аналогового преобразователя. Нулевой потенциал р прямого выхода RS-триггера 8 перйой ячейки 1 памяти поступает также на- его первый З-вход, поэтому в далы нейшем любые -изменения сигналов от компаратора на входах регистра не смогут вызвать изменения состояния R3-тpиггepa 8 первой ячейки 1 памяти. Этот же нулевой потенциал с прямого выхода RS-триггера 8 первой ячейки 1 памяти поступает на вход элемента И б первой ячейки 1 памяти, на выходе которого появляется нулевой потенциал, поступающий через элемент ИЛИ 11 на Вых. 1 и далее на вход цифроаналогового преобразов;ателя. Этот же тактовый сигнал, действующий на С-входах HS-Триггеров нечетных ячеек 1 памяти, кроме первой, не вызовет изменения их состояния, так как на их пятых 3-входах действует нулевой потенциал с выходов элемент тов И-НЕ 7 предыдущих четных ячеек памяти. В следующем такте тактовый сигнал подается на тактовую шину 3 и поступает на С-входы RS-триггеров четных ячеек памяти Так как только на пятом S-входе RS-триггера 8 второй ячейки 1 присутствует единичны потенциал, то свое состояние изменит толы ко он. При этом на прямом внходе RS-тригг гера 8 второй ячейки 1 памяти остается единичный потенциал, а на инверсном выходе появляется нулевой потенциал, если с выходов компаратора на ВХ. 1 поступает единичный сигнал, а на Вх. 2 - нулевой, и останется единичный потенциал на инверсном выходе и появится нулевой потенциал на прямом выходе, если с выходов компаратора на Вх. 1 поступает нулевой сигнал, а на Вх. 2 - единичный. При этом в первом случае на Вых. 2 останется единичный потен- , циал, а во втором - появится нуле- вой. В обоих случаях на выходе элемента -НЕ 7 второй ячейки 1 памяти появляттся единичный потенциал, поступаюий на входы третьей ячейки 1 памяти. Дальнейшая работа регистра по определению значения третьей и последующих ячеек 1 памяти происходит аналогично, как для перврй и второй ячеек 1 памяти. В биполярном преобразовании ре- гистр работает следующим образом. На шину 5 подается нулевой пот циал, который постуггает на вход, элемента НЕ 9 и на второй вход элемента И б первой ячейки 1 памяти, с выхода которого нулевой потенциал поступает на второй вход элемента ИЛИ 11, а единичный потенциал с выхода элемента НЕ 9 nocTvnaeT на вход элемента И 10. Так же,как,и при работе в однополярном преобразователе, перед началом работы производится обнуление регистра подачей на ишну 4 нулевого потенциала, при этом трехстабильНый триггер первой ячейки памяти, собранный на RS-триггере 8 и элементе И-НЕ 7i установится в перво устойчивое состояние, при котором на выходе RS-триггера 8 первой ячейки 1 памяти единичные потенциалы, а на ее элемента И-НЕ 7 нулевой потенциал. Нулевой потенциал е выхода элемента И-НЕ 7 этой ячейки поступает на вход элемента И 10 и да лее с его выхода на вход элемента ИЛИ 11. Так как на другом входе элемента ИЛИ 11 нулевой потенциал, то на его выходе также нулевой потенциал, который поступает на Вых.1 и далее .на вход цифро-аналогов го преобразователя,. Так же, как и при работе в однополярном преобразователе, нулевой Ьотенциал с выхода элемента И-НЕ 7 :первой ячейки 1 памяти проводит обнуление триггера второй ячейки 1 памяти, нулевой потенциал с выхода элемента И-НЕ 7 второй ячейки памяти проводит Обнуление триггера третьей ячейки памяти и т. д. Нулевой потенциал с выхода эле мента .И-НЕ 7 йрс ледней ячейки 1 памяти поступает на шину 12 индикаци окончания преобразования, сигнализи руя об обнулении регистра. Преобразование начинается с моме та Подачи на шину 8 единичного .потенциала, который поступает на второй R-вход, четвертый S-вход RS-триггера 8 первой ячейки 1 памят При этом состояние триггера 8 первой ячейки 1 памяти не меняется на Вых. 1 сохраняется нулевой потенциал. Затем через время, равное период тактовых сигналов на тактовую шину подается тактовый сигнал единичног уровня, поступающий на С-входа RS-триггера 8 нечетных ячеек 1 памя При этом, если измеряется величи больше, чем уравновешивающая .с выхо цифро-аналогового преобразователя, :на Вх. 1, подключенного к прямому выходу компаратора, и на Вх. 2, подключенного к инверсному выходу компаратора, соответственно действуют единичный и нулевой потенциал, а если меньше, то нулевой и единичный потенциал. Так же, как и при работе в однопо.лярном преобразователе, если на Вх. 1 единичный потенциал, а на Вх. 2 нулевой потенциал, то после прихода тактового шлпульса на С-вход RS-триггера 8 первой ячейки 1 памяти, на его прямом выходе сохраняется единичный потенциал, на инверсном выходе появляется нулевой потенциал, а на выходе элемента И-НЕ 7 первой ячейки 1 появляется единич«ый потенциал. Нулевой потенциал с инверсного выхода RS-тригге-pk 8 первой ячейки 1 памяти поступает на вход элемента И 10, на выходе которого Сохраняется нулеврй потенциал. Нулевой потенциал сохраняется на входах и выходе элемента ИЛИ 11 и соответственно на Вых. 1. Если же на Вх. 1 нулевой потенциал, а на Вх. 2 единичный потенциал, то после прихода тактового импульса на С-вход RS-триггера 8 первой ячейки 1 памяти, на его инверсном выходе сохраняется единичный потенциал, на прямом выходе появляется нулевой потенциал, а на выходе его элемента И-НЕ 7 по является единичный потенциал, поступающий на вход элемента И 10, на выходе которого появляется единичный потенциал, поступающий на вход элемента ИЛИ 11. и с его выхода на Вых. 1 ,и далее на вход цифро-аналогового преобразователя. Единичный потенциал с выхода элемента И-НЕ 7 поступает на входы второй ячейки 1 памяти, при на Вых. 2 появляется .единичный .потенциал. i - , Дальнейшее определение и уст.ановка значений второго и последующих разрядов проводится как и при работе в однополярисм преобразователе. Предложенный регистр по сравнению с известным обладает более высоким быстродействием, надежностью за счет выполнения З-триггера каждого разряда с двумя S R и С-входами и вве- дения в каждый разряд регистра элемента И-НЕ с соответствующими связями, так как при этом время приема сигнала от компаратора равно времени задержки одного логического элемента И-ИЛИ-НЕ RS-триггера регистра, потому что через это время относительно тактового сигнала нулевой потенциал с прямого или инверсного выхода RSтриггера поступает на его прямые S-вход и .R-вход соответственно и запрещает прием сигнала от компаратора, а неодновременность в переключении соседних разрядов регистра равна времени задержки на одном логическом элементе И-НЕ регистра.

В предложенном регистре по сравнению с известным после подачи на шину управления нулевого потенциала на выходе элемента И-НЕ последней ячейки памяти появляется нулевой потенциал, поступающий на шину индикации окончания преобразования, сигнализирующий о Готовности к следующему преобразованию.

Кроме того,, предложенный регистр при введении в него. элеменТа НЕ, элемента ИЛИ и второго элемента И с соответствующими связями работает как в однополярных, так и в биполярных преобразователях.

И

1

.-П.

m

I t I 1

n

л

гТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр | 1979 |

|

SU860137A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Устройство для цифровой регистрации электрических сигналов | 1987 |

|

SU1472920A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

РЕГИСТР, содержащий.ячейки памяти, каждая из которых состоит из RS-триггера-и элемента И, первый вход которого соединен с первым выходом и с первым S-входом RS- триггера, вторые и третьи S Входы КЗ-триггеров ячеек памяти являются входами регистра, С-входы RS-триггеров нечетных ячеек памяти соединены с первой тактовой шиной, С-входы RS-триггеров четных ячеек памяти соединены со второй тактовой шиной, выход каждого элемента И ячеек пг1мяти, кроме выхода элемента И первой ячейки памяти,. является выходом регистра, шину сброса, соединенную со вторым входом элемента И первой .ячейки памяти, и шину управления, отличающийся тем, что, с целью повышения быстродействия регистра, в нем в каждую ячейку памяти введен элемент И-НЕ, а в первую ячейку памяти введены элемент НЕ, элемент ИЛИ и дополнительный элемент И, причем выходы элементов И первой ячейки памяти соединены со входами элемента 1ШН данной ячейки памяти, выход элемента И первой ячейки памяти является первым выходом регистра, третий вход элемента И и вход элемента НЕ первой ячейки пгьмяти соединены с ной .управления, выход .элемента НЕ соединен с первым входом дополнительного элемента И первой .ячейки памяти, второй и третий входы дополнительного элемента И первой i ячейки соединены соответственно со вторым выходом RS-трмггера и с выхо Л элемента И-НЕ, входы элемента Й-НЁ каждой ячейки памяти соединены С соответственно с выходами RS-триггеров данной ячейки памяти, выход элемента И-НЕ каждой ячейки памяти сое- р динен со вторым входом элемента И, с четвертым и с пятым З- входаМи, с первьм R-входом RS-триггера последушцей ячейки памяти, с шестьМ го S-входом и со вторым К-входс 1 RS-триг 1 со ера данной ячейки памяти. 00 со

п

ПерВый разряд

, 7 omopoi рафяд

7

nocje ний разряд

10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР , кл, Н 03-К 13/17, 1975 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Уравновешивающая схема для аналогоцифрового преобразователя поразрядного уравновешивания | 1972 |

|

SU444319A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-06-23—Публикация

1981-04-29—Подача