(54) УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ПЙКООВРАЭШх

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при автоматизиро-. ванной обработке информации с установок физико-химического анализа, когда исследуемые сигналы имеют вид пиков заранее известной формы, например функции Гаусса, Коши и т.д.

Известно устройство для интегрирования пикообразных сигналов, содержащее следящий аналого-цифровой преобразователь с изменяемым ,коэффициентом масштабирования, блок фиксации экстремума, преобразователь код-частота, элемент И и счётчик результата 1 .

Недостатком устройства является пониженная помехоустойчивость. Уровень помех в этом устройстве не должен превышаггь двух уровней квантования, в противном случае указанное устройство становится помехонеустойчивым.

Наиболее близко к предлагаемому устройство для интегрирования пикообразных сигналов, содержащее интегратор, соединенный информационным входом с выходом управляемого ключа, Н НЖ№ный вход которого подключен СИГНАЛОВ

2

к входу устройства, первому входу блс5ка определения времени иятегрирования, первому входу блока оп1рёделёния помехи, йнформационнс у входу блока памяти, входу блока фиксации экстремума и первому входу компаратора, соединенного вторым входом с выходом, источника опорного напряжения и подключенйого вгжходом к

10 управляющим входам группы ключей, сигнальные входы первого и второго ключей группы соединены с соответствующими вь1ходами блока фиксации экстремума, причем выход блока па15мяти подключен к второму входу блока определения помехи, соединенного входом с первым входом элемента ИЛИ, подключенного выходом к первому управлянядему входу управляемого

20 ключа, второй управляющий вход которого соединен с выходом первого ключа группы ключей, выход второго ключа которой подключен к входу управления записью блока памяти,

25 соединёйного входом обнуления с выходом блока определения помехи 2.

Недостатком такого устройства является пониженная помехоустойчи30 вЬстьийтегрИрбвания последователь ности пиков, обусловленная тем, что блок определения помехи учитывает помехи только на левой сторбне интегрируемых пиков.

Цепь изобретения -увеличение помехоустойчивости при интегрировании последховательности пиков.

Для достижения указанной цели в устройство для интегрирования пикообразных сигналов, солержащее интегратор, соединенный информационным входом с выходом управляемого ключа, .сигнальный вход которого- подключен к/входу устройства, первому входу блока определения времени интегрирования, первому входу блока опрейеления помехи, информационному входу блока памяти, входу.блока фиксации экстрегиум и первому входу компаратора, соединенного вторым входом с выходом источника опорного напряжения и подключенного вьрсодом к управляющим входам группы ключей, сигнальные входы первого и второго ключей группы соединены с соответствующими выходами блока фиксации экстремума, причем выход блока памяти подключен ко второму входу блоRa ойределения помехи, соединенного выходом с Первым входом элемента ИЛИ и входом .обнуления интегратора, и КО второму, входу блока Определения времени интегрирования, выход Kdfoporo соединен со вторым входом элемента ИЛИ, подключенного выходом К первому упдавляющеМу входу управляемого ключа, дополнительно введейы источник опорного напряжения, компараторы, элементы ИЛИ, управляемой ключ и группа ключей, подключёйных первыми управляющими входами ;1,с.игяё1Лб:ноМу ВгХоду третьего, ключа осйОйной группы ключей и соединенных ЙФорййяй упрайлянзщйми входами с вы:йгодом первого дополнительного компаратора, первый вход которого соедийеи с выходом основного источника напряжения, а -второй вход йЬдаййчён к первому выходу второго дополнительного компаратора, соединенного BTopfcnvi выходом с управляющим входом дополнительного управляе-. МЬГо ключа, пёрвШ входом - tfвыходом дополнительного блока памяти, а вторым входом - с выходом первого ключа дополнительной группы ключЪй, подключенного сигналЬййМ входом к входу устройства, причем выход второго ключа дополнительной группы ключей, соединенного сигнальным входом с выходом первого ключа ос-, вовной группы ключей, подключен к второму управляющему входу основйого управляемого ключа, входу управлгения записью .основного блока памяти обнуления дополнительного блока паМяти, соединенного и.нформационйым входом с входом устройства подключенного входом управления

4

Записью к выходу первого дополнительного элемента ИЛИ, первый вход которого соединен с вых.одом дополнительного управляемого ключа, подключенного- сигнальным входом к выходу третьего ключа дополнительной группы ключей, соединенного сигнальным входом с выходом второго ключа основной группы ключей, выход третьего ключа которой соединен с Сигнальными входами четвертого и п.чтого ключей дополнительной группы ключей, причем выход четвертого ключа этой группы соединен с выходо дополнительного источника опорного напряжения,- а выход пятого ключа подключён к выходу блока определени времени интегрирования, второму вхо первого дополнительного элемента ИЛ и первому входу второго дополнительного элемента.ИЛИ, соединенного BTOpfeiM входом с выходом блока определения помехи и подключенного выходом к входу обнуления основного блока памяти.

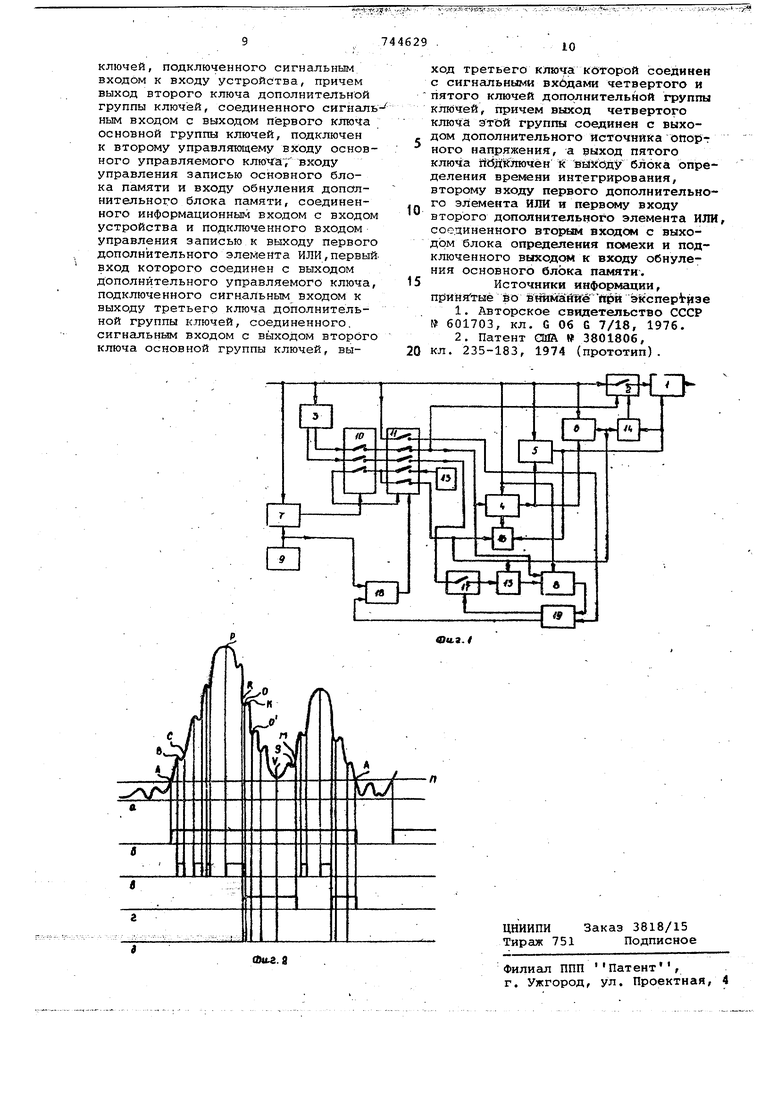

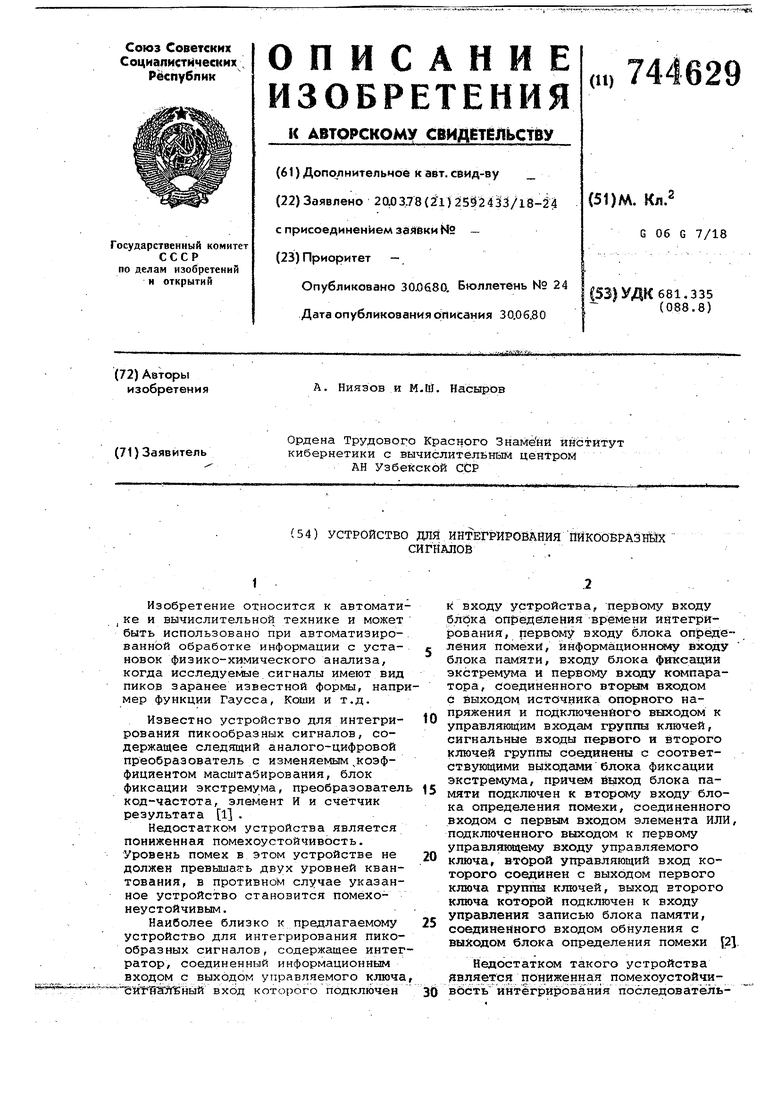

На. фиг.1 изображена блок-схема устройства на фиг. 2 - временные диаграммы работы устройства (а -. сигнал на входе устройства, б - сигнал на выходе основного компаратора; в - время работы интегратора; г - время работы дополнительной группы ключей) д - моменты записи информации в дополнительный блокпамяти) .

Устройство для интегрирования пикообразных сигналов содержит интегратор 1, основной управляемый ключ 2, блок 3 формирования экстремума, основной блок 4 памяти, блок 5 определения помехи, блок б определения времени интегрирования, основной компаратор 7, дополнительный блок 8 паЖти, основной источник 9 опорного напряжения, основную группу 10 норМальноразомкнутых ключей, дополнительную группу 1 ключей, включающую в себя первый, третий, четвертый нормальноразомкнутые ключи и второй и пятый нОрмальнозамкнутые ключи, дополнительный источник 13 опорного напрятельный источник 13 опорного напряжения, основной элемент 14 ИЛИ, первый допол.нительный элемент 15 ИЛИ, второй дополнительный элемент 16 ИЛИ, дополнительный управляемый ключ 17, первый дополнительный компаратор 18 и второй дополнительный компаратор 19.

Устройство работает следующим образом. . - .

: В исходном состоянии интегратор 1, блоки 4 и 8 памяти обнулены.

Управляемые ключи 2,17 разомкнуты. На выходе основного источника 9 опорного напряжения,--который является регулируемым, установлено напряжения порога Uf, , равное максиальному уровню помех, поступающих овместно с истинным сигналом на вход устройства. Ключи основной и ополнительной групп 10 и 11 ключей находятся в исходном состоянии. ,

На сигнальный вход основного правляемого ключа 2 поступает входной сигнал U)( , являющийся суммой истинной пикообразной функции и помехи (фиг.2,а), при превышении входным сигналом уровня порога в момент времени А (фиг.2,б) срабатывает основной компаратор 7, сигнал с его выхода замыкает ключи основной группы 10 ключей. При первом максимуме напряжения (фиг.2,а, точка в) блок 3 фиксации на своем первом выходе вырабатывает сигнал, который, пройдя через первый ключ основной группы 10 ключей и второй группы 11 ключей, замыкает основной управляемый ключ 2, записывает максимальное значение 11, в основной блок 4 памяти и обнуляет дополнительный блок 8 памяти.

Интегратор 1 с момента достижения максимума (фиг.2,в) начинает интегрировать входной сигнал, с этого же момента времени блок 5 определения помехи начинает проверку выполнения неравенства

Jrn.- Ux о ,

где и - последнее запомненное значение максимума U в блоке 4 памяти, а блок 6 определения времени интегрирования проверяет выполнение неравенства

. и, -о ,

где п - коэффициент, зависящий от вида функции,

которым описывается пикообраэный сигнал емкости интегратора 1, частотных свойств и и т.д., причем .

Если проверяемый максимум явля- тся результатом действия помехи (фиг.2,а, точка С), то блок 5 в моент времени С вырабатывает сигнал, который обнуляет интегратор 1,через элемент 14 ИЛИ размыкает основной правляемый ключ 2 и через элемент 16 ИЛИ обнуляет основной блок 4 па-, яти. Блок 5 таким образом реагирует на все максимумы входного сигнала, являющиеся результатом действия помех на левой стороне пика.

Поступление истинного пика (фиг.2,а, точка Р) устройство определяет тем, ЧТ9 в блоке 5 не выполняется условие и , поэтому интегрирование и в интеграторе 1

продолжается до того момента (фиг.2,.

а, точка R, фиг. 2в), пока блок б Опреэзеле ййгя времени интегрирования не; вь1работает сигнал окончания интегрирования, который через элемент 16 ИЛИ обнуляет блок 4 памяти.

через элемейт 15ИЛИ подает сигнал записи значения (1 (фиг. 2,а, точка R)B блок 8 памяти и через элемент 14 ИЛИ размыкает;ключ 2,Сигнал с блока б поступает также на после-:

дующие устройства обработки информации (на чертежах не изображены), которые считывают значение интеграла из интегратора 1 и затем обнуляют его.

Этот же сигнал с блока б через пятый нормальнозамкнутый ключ дополнительной группы 11 ключей и через третий ключ основной группыЮ ключей, который в данчый момент замкнут,

поступает на первый управляющий вход

дополнительной группы 11 ключей. С этого момента первый, третий, четвертый ключи этой группы замыкаются, а второй и пятый ключи размыкаются, так как подачей напряжения с выхода источника 13 через четвертый ключ дополнителБной группы и третийключ основной группы на первый управляющий вход группы 11 ключей эта группа становится в режим

самоблокировки.

Таким образом, с этого момента времени за счет переключения ключей 11 группы отключаются блок 4 Пс1мяти, блок 5 определения помехи, блок б

определения времени интегрирования и управляемый ключ 2, а в работу включаются блок 8 памяти, компараторы 18, 19, управляемый ключ 17 и элемент 15 ИЛИ, которые образуют

блок определения помехи на правой стороне пика.

Блок определения помехи на правой стороне пика работает следующим образом,

Запомненное в блоке 8 памяти

значение -входного сигнала Uj сравнивается на компараторе 19 с текущим входнь1м сигналом U . Второй выход компаратора 19 вырабатывает скачок

напряжения при U -Uj О, который замыкает управляемый ключ 17, а первый выход компаратора 19 выдает разность между напряжениями U и Uj только при положительном значении разности .

Разностное напряжение с первого выхода компаратора 19 сравнивается на компараторе 18 с напряжением порога Up, источника 9, т.е. с максимальньм уровнем помех. При выполнеНИИ условия

() о

компаратор 18 вырабатывает сигнал, который через второй управляющий

60 вход группы вход группы 11 ключей снимает блокировку с этой группы.

После записи сигналом с блока б в блок памяти 8 напряжения и, (фиг.2,а,д, точка R) идет сравнение этого напряжения на компараторе 19 и, так как О, то ключ 17 замкнут. Поэтому при-достижении минимума (фиг.2,а, точка 0) сигнал со второго выхода блока 3 фиксации экстремума, по второму-выходу которого фиксируется минимумы напряжения, через второй ключ группы 10 и третий ключ группы 11, управляемый ключ 17 и элемент 15 ИЛИ подаёт в блок 8 памяти сигнал записи, по которому в этот блок записывается значение минимума 0 , Наступивщий после минимума (после точки О/ фиг.2,а) прирост сигнала U,, сранивается с максимальным уровнем помех Up, на. Компараторе 18. Если ()-Un О, то никаких переключений не происходит и поэтому вира ботанный на первом выходе блока 3 сигнал максимума в момент времени К (фиг.2,а) не проходит через группу 11 ключей.

. При поступлении следующего минимума (момент О , фиг.2,а,д) точно так же записывается значение в момент 0 на блок 8 памяти. Устройство таким образом реагирует и на все другие минимумы, т.е. когда запомненное значение U больше текущего (следующего) минимума. Если уровень запомненного.минимума меньше уровня текущего минимума (фиг.2,а, тбчки V и S), то управляемый ключ 18 разомкнут, так как Uj(, но (Ux-U3)-Up о, то сигн ал СОBTdporo выхода блока 3. не проходит -через ключ 17 и новое текущее значение минимума не записывается в блок 8 памяти.

При дальнейшем увеличении U компаратор 18, при выполнении условия

()-( о

(фиг.2,а,г, момент м) вырабатывйет сигнал,.который снимает блокировку группы 11 клю-уей. Это означает, что начал поступать следующий пик Ключи 11 возвращаются в исходное положение. Интегратор 1, блок 4 памяти, блоки 5 и б работают в режиме определения истинного пика и интегрирования его площади, как описано выше.. , .

Ейлй входной сигнал U, после его интетЕ йрования убывает ниже уровня порога (фиг.2,а, момент А}, то .компаратор 7 из-за выполнения условия U(-Ur, О снимает свой сигна с управляющего входа группы 10 ключей. С группы 11 ключей блокировку снимает третий ключ 10 группы ВОзвращением в исходное, т.е. йормалвнораэомкнутое состояние.

Таким образом, устройство для интегрирования пикообразных кривых возвращается в исходное состояние, за исключением блока 8 памяти и ключа 17. На блоке 8 памяти остается последнее запомненное значение

минимума входного сигнала, а так как и( -Uj О, то и управляемый ключ 17 замкнут, но это не мешает нормальной работеустройства. Первый же сигнал максимума с выхода блока 3, установив в ,нуль блок 8 памяти,. 5 размыкает управляемый ключ 17.

Таким образом, предложенноеустройство является более помехоустойчивым чем известное, так как позQ воляет учитывать помехи как на левой стороне интегрируемых пиков, так и на правой их стороне.

Формула изобретения

Устройство для интегрирования пикообразных сигналов, содержащее интегратор, соединенный информационным входом с выходом управляемого

ключа, сигнальный вход которого подключен к входу устройства, первому входу блока определения времени интегрирования, первому входу блока определения помехи, информационному

входу блока памяти, входу блока фиксации экстремума и первому входу компаратора, соединенного вторым входом с выходом источника опорного напряжения и подключенного выходом к

управляющим входам группы ключей, сигнальные входы первого и второго кличей группы соединены ссоответствующими выходами блока фиксации экстремума, причем выход блока памяти подключен ко второму входу блока определения помехи, соединенного выходом с первым входом элемента ИЛИ и входом обнуления интегратора, и ко второму входу блока определения времени интегрирования, выход которого соединен свторым входом элемента ИЛИ, подключенного выходом к первому управляемому входу управляемого ключа, отличающееся тем, что, с целью увеличения помехоустойчивости при интегрировании последовательности пиков,в устройство дополнительно введены источник опорного напряжения, компараторы, элементы ИЛИ, управляемый ключ и группа ключей, подключенных первыми уп1равляющими входами к сигнальному входу третьего ключа основной группы ключей и соединенных вторыми управляющими входами с- выходами первого дополнительного компаратора, первый вход которого соединен с выходом основного источника опорного напряжения, авторой вход подключен к первому выходу второго дополнительного компаратора , соедищенного вторым выходом с управляющим входом дополнительного управляемого ключа, первым входом - с выходом дополнительного блока памяти, а вторымвходом - с выходом первого ключа дополнительной группы

ключей, подключенного сигнальным входом к входу устройства, причем выход второго ключа дополнительной группы ключей, соединенного сигнальным входом с выходом первого ключа основной группы ключей, подключен к второму управляющему входу основного управляемого , входу управления записью основного блока памяти и входу обнуления допалнительного блока памяти, соединенного информационным входом с входом устройства и подключенного входом управления записью к выходу первого дополнительного элемента ИЛИ,первыйвход которого соединен с выходом дополнительного управляемого ключа, подключенного сигнальным входом к выходу третьего ключа дополнительной группы ключей, соединенного, сигнальным входом с выходом второго ключа основной группы ключей, выход третьего ключа кдторой соединен с сигнальными вхбдами четвертого и пятого ключей дополнительной группы ключей, причем четвертого ключа эгоЛ группы соединен с выходом дополнительного Источника спорт ного напряжения, а выход пятого ключа ййдйлючён к бйХЪду блока определения времени интегрирования, второму входу первого дополнительного элемента ИЛИ и первому входу

0 второго дополнительного элемента ИЛИ, соединенного вторым входом с выходом блока определения помехи и подключенного выходом к входу обнуления основного блока пгилятн.

5

Источники информации, ПЕ йняГтыё ёо йнйканйё Лрй экспертизе

1.Авторское свидетельство СССР № 601703, кл. G Об G 7/18, 1976.

2.Патент США 3801806, 0 кл. 235-183, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрированияпиКООбРАзНыХ фуНКций | 1978 |

|

SU813453A1 |

| Система экстремального регулирования | 1981 |

|

SU1056132A1 |

| Интегратор | 1982 |

|

SU1339590A1 |

| Устройство для интегрированияпиКООбРАзНыХ СигНАлОВ | 1978 |

|

SU822205A1 |

| Измеритель шумов | 1990 |

|

SU1723535A1 |

| Частотный дискриминатор | 1988 |

|

SU1676078A2 |

| Устройство дя определения граничных точек хроматографического пика | 1988 |

|

SU1587547A2 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| Устройство для определения моментов появления экстремумов | 1989 |

|

SU1661980A2 |

Авторы

Даты

1980-06-30—Публикация

1978-03-20—Подача