(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1977 |

|

SU785897A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU646374A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU280547A1 |

| ИНФОРМАЦИОННО-ПОИСКОВАЯ СИСТЕМА | 2001 |

|

RU2199778C1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1274002A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU926717A1 |

...

Изобретение относится к области .запоминающих устройств.

Известны ассоциативные запоминающие устройства 11 и 3.

Известны ассоциативные запоминающие устройства (АЗУ), содержащие матрицу многоразрядных запоминающих элементов, формирователи опросного тока, регистры и детекторы 1.

.В этих устройствах запоминающие элементы помимо собственно функции запоминания, должны выполнять функцию «Неравнозначность (или «Равнозначность.) над хранимой и опросной информацией. Это значительно усложняет запоминающий элемент, и следовательно, все устройство и приводит к большим аппаратурным затратам, при которых использование таких АЗУ; особенно больщого объема, становится экономически невыгодным.

Из известных устройств наиболее близким техническим решением к данному изобретению, является ассоциативное запоминающее устройство, содержащее регистры, выходы которых соединены с соответствующими входами элементов ИЛИ, выходы одних из которых под1(лючены ко входам де-л

шифратора, запоминающие элементы, выходы которых соединены со входами соответствующих Детекторов 2.

Недостатком этого устройства является большое количество выходных шин дешифратора (при большой емкости устройства), а также значительные аппаратурные затраты и сло.жность самого дешифратора с большим количеством выходных шин, что также снижает быстродействие устройства и препятствует построению АЗУ большого объема.

10 Цель изобретения - увеличение информационной емкости и упрощение устройства. Поставле-йная цель достигается тем, что устройство содержит дополнительные дешифраторы и элементы И по чисЛу запоминающих элемРнтоБ, входы которых подключены

5 соответственно к выходам дешифраторов, выходы элементов И подключены ко входам соответствующих запоминаюШ.их элементов, входы дополнительных дешифраторов подключены к выходам других элементов ИЛИ.

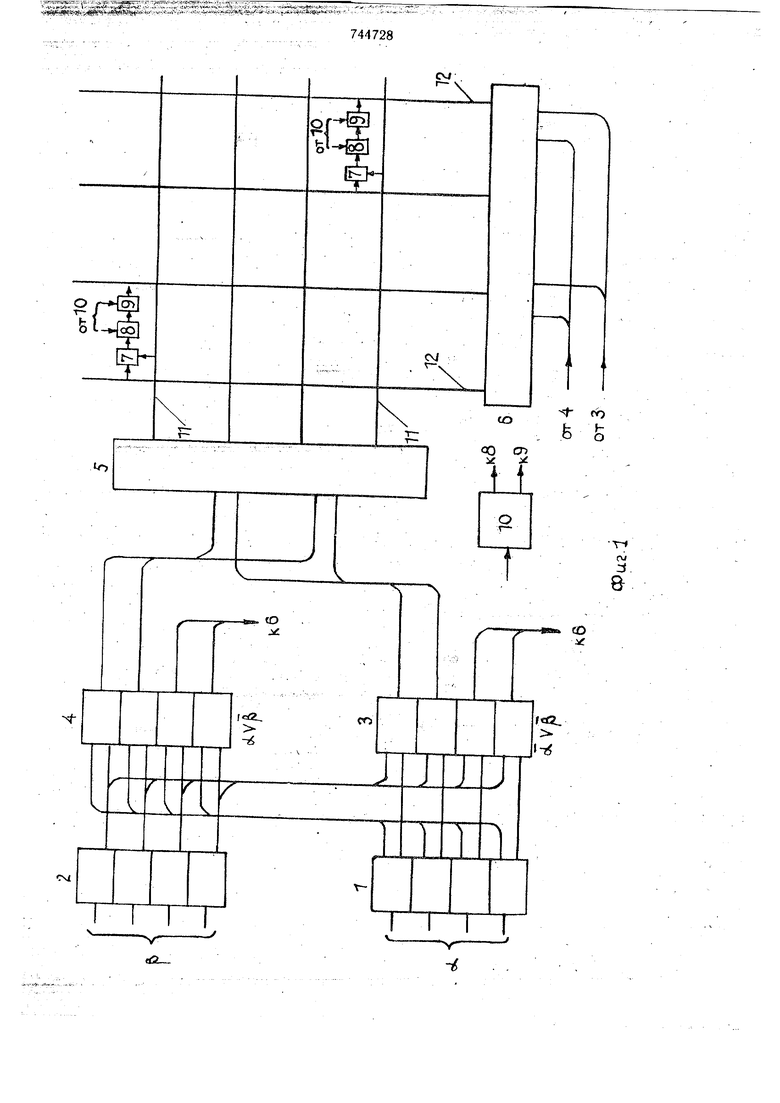

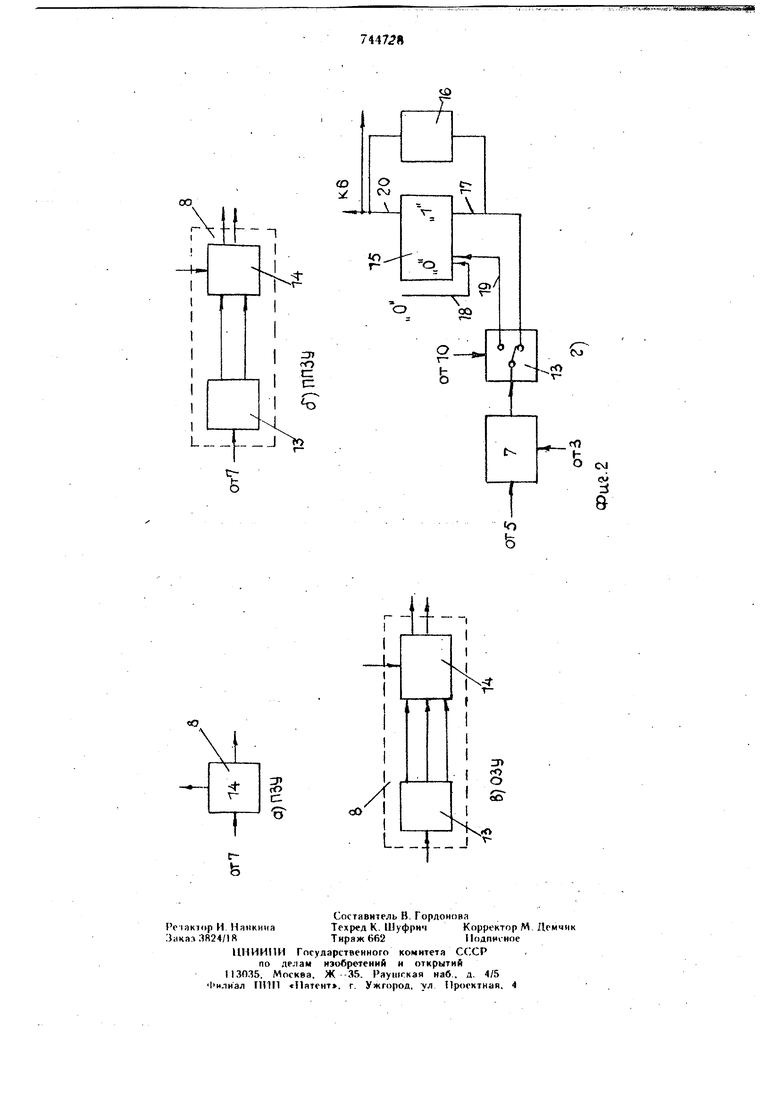

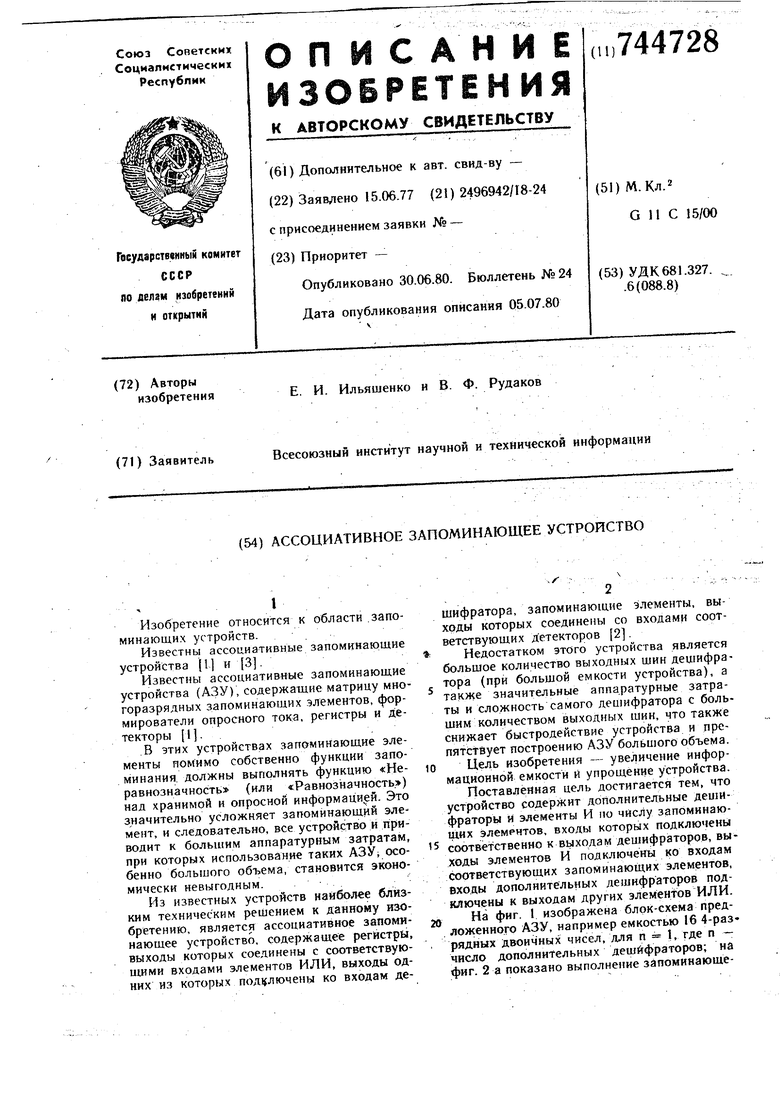

20 На фиг. I изображена блок-схема предложенного АЗУ, например емкостью 16 4-раз рядных двоичных чисел, для п 1, где п - число дополнительных дешифраторов; на фиг. 2 а показано выполнение запоминающе-f -

ro элемента для ПОСТОЯНЕЮГО запоминающего. устройства (АЗУ); на фиг. 2 б - то же,, для полупостоянного запомрткающего уст- ройства (ДПЗУ); на фиг. 2 в -- то же для оперативного зaпo fинaюlUeгo устройства (ОЗУ); на фиг. 2 г - из возможных вариантов запоминающего элемента для ОЗУ. ,

Устройство содержит (фиг. 1) регистр I, используемый в качестве опросного, регистр 2, являющийся маскирующим, группы элементов 3 и 4 ИЛИ, дешифратор 5, до полнительный дешифратор б, элементы 7 И, запоминающие элементы 8, детекторы 9, блок 10 управления, горизонтальные 11 и вертикальные 12 координатнь е шины.

Нулевые выходы регистров 1-й 2 соедипены с одними входами элементов 3 и 4 ИЛИ,другие входы элементов 3 и 4 ИЛИ соединены соответственно с иулевымй И единичными выходами регистров I и 2. Выходы элементов 3 ИЛИ соединены соответственно с нулевыми BxoiidMH дешифраторов и 6, а выходы элементов 4 ИЛИ подключены соответственно к единичным входам дешифраторов 5 и 6. Входы элементов И подключены соответственно к координатным шинам II и 12, соединенным с соответствующими выходами дешифраторов 5 и 6, выходы элементов 7 И подключены ко входам соответствующих запомй:на 6щих элёйентов 8.

В предлагаемом устройстве факт .записи любого 4-разрядного двоичного кода отождествляется с установкой, напрнмер, в единичное состояние соответствующего запоминающего элемента 5. .

В зависи.мости от требований к частоте и продолжительности времени .записи запоминающий элемент 5 может быть вЫполней различными способами.

Если в устройстве допустима однократная з-апись (ПЗУ), то. запоминающий элемент 5 может быть выполнен в виде уси тительного элемента, либо простОШрёВДШи, соединяющей выход элемента 7 И со входом соответствующего детектора 9 (в последнем случае факт отсутствия записи может быть представлен отсутствием соотй1г1 сТв7юЩёгЬ элемента 7 И и детектора 9).

Если в устройстве допустимы сравнитель но редкая и медленная перезапись информации (ПЗУ), то запоминающий элемент 8 может быть выполнен в виде ключа 13, два выхода которого, соответствующие C4HfHванию и записи, соединены со. входами собственного элемента 14 памяти (фиг. 26).

Еслч в устройстве требуется оперативная перезапись информации (ОЗУ),to в этом случае ключ 13 может иметь три выхода соотцёгственно для записи, считывания и избирательного стирания информации (фиг. 2п). либо ключ 13 может иметь два выхода (один - для записи, другой - для считывания и избирательного стирания ИнMSSSSSS

формации), а элемент памяти выполнен состоящим из триггера 15 и элемента 16 задержки (фиг. 2 г). В последнем случае стирающий импульс, поступающий иа триггер, должен иметь длитeльнoctь, превышающую время задержки в элементе 16 задержки.Ключ 13 (фиг. 26, в) уп|)авляется от блока 10, который может также быть использован и для стирания всей информации в АЗУ.

Рассмотрим работу устройства в предположении, что его запоминающие элементы вьшолнены по схеме, изображенной на фиг. 2

Устройство может работать в четырех режимах: записи информации, общего стирания информации, избирательного стирания информации и поиска информации.

При этом предполагается, что все триггеры устаиовлены первоначально в нулевое состояние.

Режим записи информации. В этом режиме в регистр 1 пбёТупает код чйсла, которое необходимо зaпиcatь, а в регистр 2 - код 1111 (т. е. содержащий все единицы). В .соответствии с этим кодом возбуждают один из выходов дешифратора 5 и один из выходов дешифратора 6. На выходе элемента И, оба входа которого подключены к возбужденным выходам дешифраторов 5 и 6, появляется импульс, который через ключ 13, управляемый блоком 10, поступает иа вход 17 триггера 15 и устанавливает его в единичное состояние.

Режим общего стирания информации. В этом режиме на входы 18 всех триггеров 15 из блока 10 поступает импульс, устанавливающий триггеры 15 в нулевое состояние.

Режим избирательного стирания информации. Этот режим отличается от режима записи тем, что с выхода ключа 13 импульс поступает на вход 19 выбранного триггера 15 и устанавливает его в нулевое состояние. При этом длительность импульса, поступающего на триггер 10 от ключа 8, должна бь1ть больще времени задержки элемента 16.

Режим поиска информации. Целью поиска является выяснение факта записи в устройстве любого числа или некоторого подмножества чисел из множества, состоящего

из чисел О, I, 2, ... 14, 15 (0000, 00011110,

1111 в двоичном коде), В соответствии с этим рассмотрим 2 случая поиска.

Первый случай. В этом случае требуется выяснить, записано ли в АЗУ, какое-либо конкретное число из множества чисел 0,1,...,

14, 15.;;. ;.. . iНа регистр 1 поступает двоичный код этого числа, который используется в качестве поискового образа, а иа регистр 2 - код 1111 (т. е. состоящий из всех единиц).

Как и -в режиме записи, на выходе единственного элемента 7 И, соответствующего коду поискового образа, появляется импульс, который через ключ 13 поступает на вход 19 соответствук)щего триггера 15. Если триг гер 15 находится в единичном состоянии,

5

что соответствует записи кода искомогй числа в АЗУ, то он переключается в нулевое состояние. Импульс, появляющийся на выходе 20, триггера 15, используется для переключения соответствующего детектора 9 в единичное состояние (перед началом поиска все детекторы 9 устанавливаются в нулевое состояние) и возврата в единичное состояние триггера 15 (через элемент 11 задержки). Если триггер 15 находится в нулевом состоянии, что соответствует отсутствию записи кода искомого числа в АЗУ, то он не изменяет своего состояния, поэтому не изменяет cedero состояния и детектор 9, связанный с этим триггером 15 (ни один из детекторов 9 не изменяет своего состояния).

Второй случай. В этом случае требуется выяснить, записаны ли в АЗУ какие-либо числа, часть разрядов которых совпадает с кодом числа, представляющего поисковый образ и входящего в множество чисел 0,1,...14,15.

Пусть конкретно требуется выяснить, записаны ли в АЗУ числа, совпадающие с кодом поискового образа во всех разрядах, кроме, например, младщега (младщий разряд считается замаскированньш).

На регистр 1 поступает код поискового образа, а на регистр 2 - код 1110 (т. е. состоящий из единиц во всех разрядах, кроме замаскированного). В этом случае возбужда ется один выход дешифратора 5 и два выхода дешифратора 6. На выходе двух элементов 7 И, оба входа которых связаны с координатными шинами 11 и 12, соединенными с возбужденными выходами дешифраторов 5 и 6, появляются импульсы (в общем случае при маскировании m разрядов кода поискового образа, где О т 4 появляется импульс на выходе элементов 7 И устройства (фиг. 1). Далее работа устройства подобна работе в режиме поиска (первый случай) с тем лишь отличием, что возможно переключение двух триггеров 15 и соответственно установление в единичное состояние стольких же детекторов 9- Обнару-. жение детекторов, установленных в единичное состояние, выполняется известными способами (3).

. В предлагаемом устройстве значительно сокращены аппаратурные затраты на дешифрирование (при одной и той же емкости АЗУ), а также существенно уменьшено количество дешифраторных шин. Для предложенного АЗУ, хранящего 16-разрядные числа и соответственно емкостью 2 чисел, количество деншфраторных щин уменьшается по сравнению с известным (прн

п 1) в 256 раз.

Уменьшение количества тин имеет важное значение при выполнении предложенного устройства на интегральных схемах.

15

Формула изобретения

Ассоциативное запоминающее устройство, содержащее регистры, выходы которых соединены соответственно со входами элеменe тов ИЛИ, выходы одних из KOTOJibix подключены ко входам дешифратора, запоминающие элементы, выходы которых соединены со входами соответствующих детекторов, огличающееся тем, что, с целью увеличения информационной емкостн и упрощения устройства, оно содержит дополнительные де-, шифраторы и элементы И по числу запоминающих элементов, причем входы элементов И Подключены соответственно к выходам дещифраторов, выходы - ко входам J соответствующих запоминающих элементов, входы дополнительных дешифраторов подключены к выходам других элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1957, с. 32-37.

744728

CN/

i:

CM

lO

to

f«,

т5

ЛГ

a2

-f fb

to

fe S

00 СГ)

и

T

(M

::

&

„да. CO

f«a. 5

-7

лг

Т

Авторы

Даты

1980-06-30—Публикация

1977-06-15—Подача