Изобретение относится к радиоэлектронике и может быть использовано в устройствах автоматики дискретного действия.

По авт. св. № 491204 известно устройство для контроля последовательности чередования асинхронных импульсных сигналов, содержащее входные и выходную шины и триггеры, единичные выходы которых подключены к одним из входов вентилей, каждая t-тая входная шина соединена с другим входом t-Toro вентиля, с единичным входом (L -- 1)-го триггера и с нулевым входом ( i,+ )-го триггера, выходы всех вентилей подключены ко входам элемента ИЛИ, выход которого соединен с входной шиной. Недостатком устройства является отсутствие контроля наличия ложных импульсов, которые могут поступить на устройство одновременно с текущими импульсными сигналами п результате возникновения сбоя или неисправности в контролируемой схеме, т. е. ислостягочно широкие функциональные возможности.

Цолью и (обретения является расширение

фуикциональны.ч возможностей устройства.

Цель а(1тигается тем, что в устройство

для контроля последовательности чередования асинхронных импульсных сигналов, содержащее входные и выходную шины и триггеры, единЕЕчные выходы которых под лючены к однн.м из входов вентилей, каждая (,-тая входная шина соединена с другим входом i-Toro вентиля, с единичным входом (6-1)-ого триггера, выходы всех вентилей подключены ко в.ходам элемента ИЛИ, выход которого соеди.чен с выходной шиной, введены дополнительные элементы И, дополнительный элемент ИЛИ, элемент загтре10 та, первый вход каждого дополнительного элемента И подключен к нулевому выходу каждого триггера, второй вход каждого дополнительного элемента И подключен к каждой 1-той входной шине, выходы дополнительных элементов И подключены ко

входам дополнительного элемента ИЛИ, выход которого подключен к первому входу элемента запрета, второй вход которого подключен к выходу элемента ИЛИ.

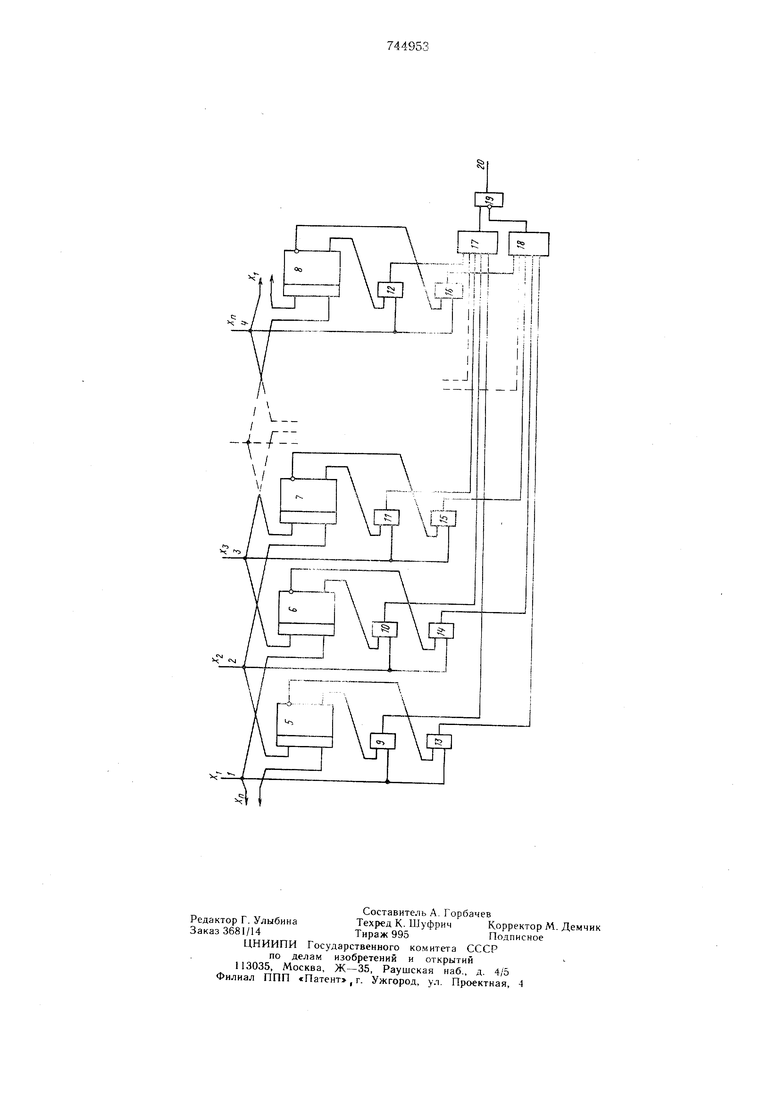

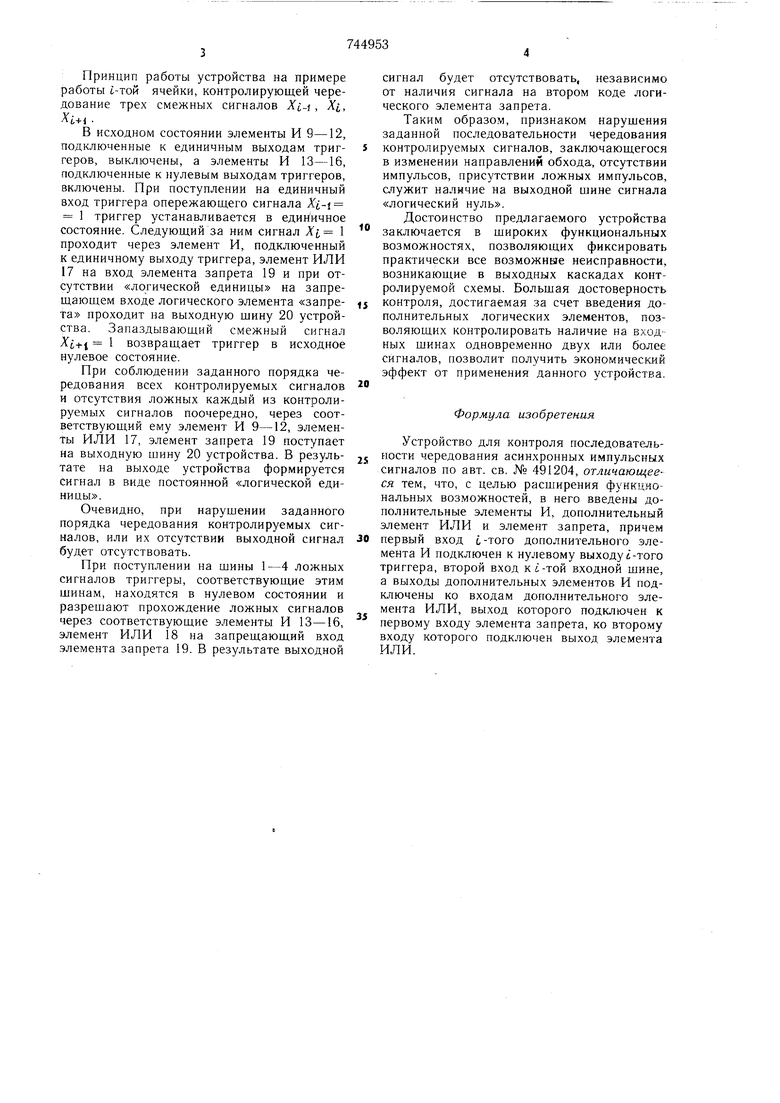

На чертеже приведена схема устройства.

2рУстройство содержит входные шины I - 4,

триггеры 5-8 от первого до t-Toro, элементы И 9--12, дополнительные от первого до i-Toro элементы Я 13 , элементы ИЛИ 17 и 18, элемент 19, выходную шину 20.

Принцип работы устройства на примере работы i-той ячейки, контролирующей чередование трех смежных сигналов Xi-i , Xi,

В исходном состоянии элементы И 9-12, подключенные к единичным выходам триггеров, выключены, а элементы И 13-16, подключенные к нулевым выходам триггеров, включены. При поступлении на единичный вход триггера опережающего сигнала Xi-i 1 триггер устанавливается в единичное состояние. Следующий за ним сигнал Xi 1 проходит через элемент И, подключенный к единичному выходу триггера, элемент ИЛИ 17 на вход элемента запрета 19 и при отсутствии «логической единицы на запрещающем входе логического элемента «запрета про.кодит на выходную щину 20 устройства. Запаздывающий смежный сигнал Xi+ 1 возвращает триггер в исходное нулевое состояние.

При соблюдении заданного порядка чередования всех контролируемых сигналов и отсутствия ложных каждый из контролируемых сигналов поочередно, через соответствующий ему элемент И 9-12, элементы ИЛИ 17, элемент запрета 19 поступает на выходную шину 20 устройства. В результате на выходе устройства формируется сигнал Б виде постоянной «логической единицы.

Очевидно, при нарушении заданного порядка чередования контролируемых сигналов, или их отсутствии выходной сигнал будет отсутствовать.

При поступлении на шины 1-4 ложных сигналов триггеры, соответствующие этим шинам, находятся в нулевом состоянии и разрешают прохождение ложных сигналов через соответствующие элементы И 13-16, элемент ИЛИ 18 на запрещающий вход элемента запрета 19. В результате выходной

сигнал будет отсутствовать, независимо от наличия сигнала на втором коде логического элемента запрета.

Таким образом, признаком нарушения заданной последовательности чередования

контролируемых сигналов, заключающегося в изменении направлений обхода, отсутствии импульсов, присутствии ложных импульсов, служит наличие на выходной шине сигнала «логический нуль.

Достоинство предлагаемого устройства

заключается в широких функциональных возможностях, позволяющих фиксировать практически все возможные неисправности, возникающие в выходных каскадах контролируемой схемы. Большая достоверность

контроля, достигаемая за счет введения дополнительных логических элементов, позволяющих контролировать наличие на входных шинах одновременно двух или более сигналов, позволит получить экономический эффект от применения данного устройства.

Формула изобретения

Устройство для контроля последовательности чередования асинхронных импульсных сигналов по авт. св. № 491204, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены дополнительные элементы И, дополните«1ьный элемент ИЛИ и элемент запрета, причем 0 первый вход t-Toro дополнительного элемента И подключен к нулевому выходу -того триггера, второй вход Ki-той входной шине, а выходы дополнительных элементов И подключены ко входам дополнительного элемента ИЛИ, выход которого подключен к первому входу элемента запрета, ко второму входу которого подключен выход элемента ИЛИ.

i i Ill

„. . i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности чередования асинхронных импульсных сигналов | 1973 |

|

SU491204A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| Генератор тактовых импульсов | 1979 |

|

SU855963A2 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Одноканальное устройство для фазового управления статическим преобразователем | 1977 |

|

SU736344A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Устройство для контроля серий импульсов | 1989 |

|

SU1676076A1 |

| Устройство для выделения экстремумов временных интервалов | 1979 |

|

SU864533A1 |

| Преобразователь кода в период повторения импульсов | 1978 |

|

SU744976A1 |

Авторы

Даты

1980-06-30—Публикация

1978-01-09—Подача