Предлагаемое устройство относится к цифро вой информационно-измерительной технике, может быть использовано при автоматизации разностных измерений в различных областях науки и техники. Известно устройство для определения разности двух импульсных последовательностей, содержащее реверсивный счетчик и Схемы синхронизации, в котором реверсивный счетчик служит в качестве двухканального интегратора разнос.ти частот эталонного и информационного сигналов. В зтом устройстве информация в реверсивном счетчике меняется с приходом каждотО импульса, что делает невозможным снятие результирующей информации. Известно отсчетно-измерительное устройство, содержащее два формирователя частотно-имнуль сных последовательностей, генератор тактовых импульсов, состоящий из задающего генератоар и подключенного к его выходу шагового ра пределителя тактовых импульсов, два блока син хронизации, каждый из которых включает в себя запоминаюишй триггер, первым входом подключевный к выходу одного из формирователей часгогао-импульсных последовательностей, и первую схему совпадения, одним нз входов подключенную к выходу заномннайщего триггера, а вторым входом - к первому управляющему выходу генератора T KTOBE IX импульсов, дискретный фильтр, СОСТОЯЩЮЁ из двух инверторов, входами подключенных к выходам первых схем совпадения соответствующих блоков жнхронизащм, двух схем совпадения, первыми входами подключенных к выходам инверторов, триггера вычитания с раздельными входа1«и, своими выходами подключенного ко BtopbiM входам схем совпадения дискретного фильтра, и реверсивный счетный блок, входами подключенный к выходам схем совпадения дискретного фильтра. Это устройство малонадежно из-за сбоев при одновременном поступлении входньгх импульсов.. Цель изобретения - повыщение надежности устройства. Поставленная цель достигается тем, что в известное отсчетно-измерительное устройство

введен логический блок, содержащий четыре схемы совпадения, три инвертора, триггер с раздельными вхсщами, дифференциальную цепь и блок установки в исходное состояние, причем первый вход первой схемы совпадения подключен к третьему входу первой схемы совпадения первого блока синхронизации и выходу первого формирователя частотнЬтх импульсных последовательностей; выход первого инвертора подключен ко второму входу первой схемы совпадения и к первому входу второй схемы совпадения; выход второй схемы совпадения соединен с первым входом триггера вычитания дискретного фильтра; вход второго инвертора подключен к третьему входу первой схемы совпадения второго блока синхронизации, к выходу второго формирователя частотно-импульсных последовательностей и к первому входу третьей схемы совпадения, выходКоторой соединен со входом первого инвертора; вход дифференцирующего звена подключен к выходу второго инвертора, а выход - ко второму входу третьей схемы совпадения; одни из входов триггера с раздельными входами подключен к выходу первой схемы совпадения, а выход триггера соединен с третьим входом третьей схемы совпадения; выход блока установки исходного состояния подключен ко второму входу триггера с раздельными входами и к первому входу четвертой схемы совпадения, выход которой соединен со вторь1М входом триггера вычитания дискретного фильтра, в каждый из блоков синхронизации введен триггер перезаписи, первым входом подключенный к выходу первой схемы совпадения синхронизации, а вторым входом соединенный с выходом запоминающего триггера, и вторая схема совпадения, первым входом подключенная к выходу триггера перезаписи, вторым входом соединенная со вторым управляющим выходом генератора тактовых импульсов, а выходом подключенная ко второму входу запоминающего триггера, причем вторая схема совпадения первого блока синхронизации выходом подключена ко втЬрому входу второй схемы совпадения логического блока, а вторая схема совпадения второго блОка синхронизации выходом подключена ко второму входу четвертой схемы совпадения логического блока.

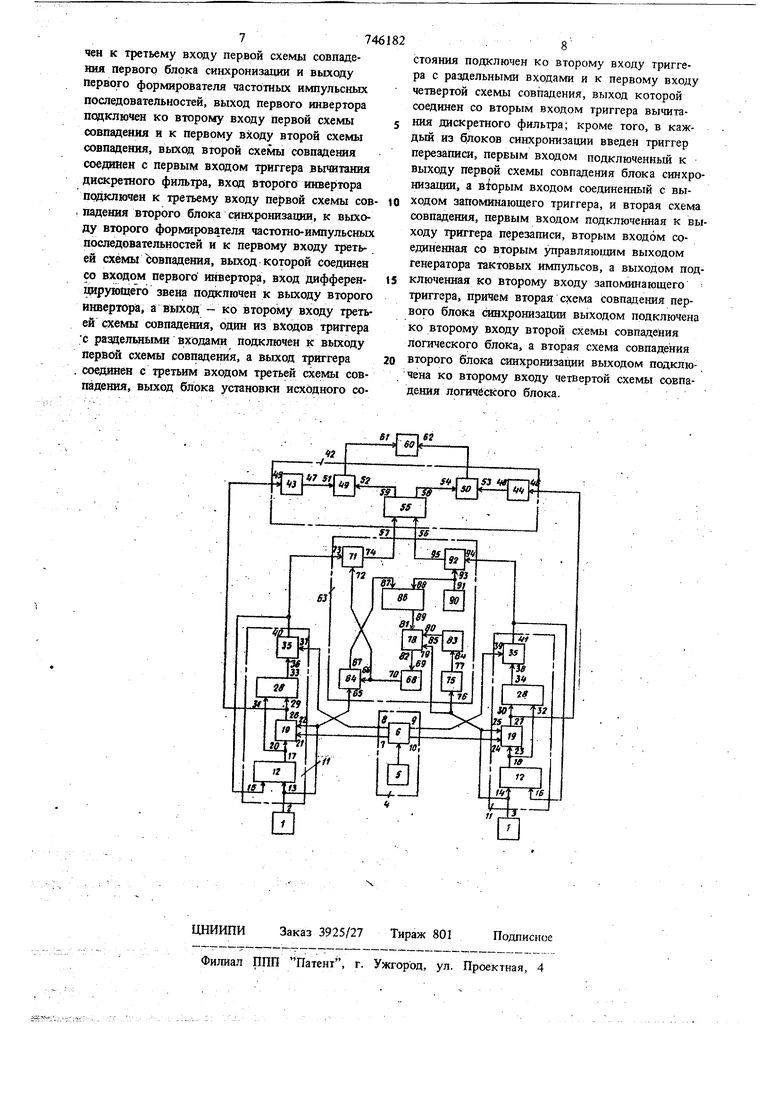

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит два формирователя частотных импульсных последовательностей 1, имеющих соответственно выходы 2 и 3, генератор тактовых импульсов 4, состоящий из задающего генератора 5 и подключенного к его выходу шагового распределителя тактовь1Х импульсов 6 с выходами 7-Ш; два блока синхронизации и, каждый и: которых состоит из запоминающего триггера 12, лмсгощегО единичный вход 13 (14), нулевой вход 15 (16) и единичный выход 17 (18), перпон схемы совпадения 19, имеющей входы 20-22 (23--25) и выход 26 (27), триггера перезаписи 28,, имеющего единичный вход 29 (30), нулевой вход 31 {32} и единичный выход 33 (34), второй схемы совпадения 35, имеющей входы 36 (37) и 38 (39) и выход 40 (41), дискретный фильтр 42, состоящий из двух инверторов 43 и 44, име ющих входы 45 и 46 и выходы 47 и 48, двух схем совпадения 49 и 50, имеющих входь 51, 52 и 53, 54, триггера вычитания 55, имеющего входы 56 и 57 и выходы 58 и 59, реверсивный счетный блок 60, имеющий входы 6 и 62, и логический блок 63, состоящий из первой схемы совпадения 64, имеющей входы 65, 66 и выход 67, первого инвертора 68, имеющего вход 69 и вькод 70, второй схемы совпадения 71, имеющей входы 72, 73 и выход 74, второго инвертора 75, имеющего вход 76 и выход 77 третьей схемы совпадения 78, имеющий входы 79, 80, 81 и выход 82, дифференцирующего звена 83, имеющего вход 84 и выход 85, триггера 86 с раздельными рхОдами 87, 88 и выходом 89, блока установки исходного состояния 90, имеющего вьйсод 91, и четвертой схемы совпадения 92, имеющей входы 93, 94 и выход 95

Принцип работы устройства заключается в следующем. Каждый входной импульс частотных последовательностей, формируемых формирователями 1, запоминается соответствующим триггером памяти 12 блоков синхронизации 11. Задающий генератор 5 через щаговый распределитель 6 разновременно опрацшвает состояния триггеров памяти 12 и перезаписывает состояния на триггеры перезаписи 28 с помощью трехвходовой схемы совпадения 19, а также считывает состояния триггеров перезаписи 28 с помощью двухвходовых схем совпадения 35. На выходах 40 и 41 блоков синхронизации 11 формируют- ся сянхронизировагшые с тактовыми импульсами щагового распределителя 6 последовательности импульсов постоянной длительности, равной интервалу между двумя соседними синхроимпульсами, которые поступают на входы дискретного фильтра 42, исключающего одиночночередующиеся входные импульсы и определяющего очередность поступления счетных и тульсов на входы 61 и 62 реверсивного счетного блока 60, на вь1Ходе которого представляется в используемом коде результат сравнения частотных импульсных последовательностей с учетом йнака их разности. Логический блок 63 устраняет неоднозначность исхощки-о состояния триггера вычитания 55 и устанапливает строгую очередность обработки информации, независимо от порядка поступления ее на входы соответствующих фо1)мир(1ватслей частотных импульсных посЛсдопательностей 1. В исходном состоянии триггер вычитагшя 55 запрещает прохождение и fflyльcoвчерез схему совпадения 49 и разрешает прохождение импуль сов через схему совпадения 50. В то же время триггер 86 разрешает прохождение через схему совпадения 78 импульса с дифференцирующего звена 83. В начале работы возможны два случая: первый импульс приходит с выхода 2 первого формирователя импульсных последовательностей 1 или с выхода 3 второго формирователя импульсных последовательностей. В первом случае с приходом импульса запоминающий триггер 12 устанавливается в со- , стояние, разрешающеепрохождение синхроимпульса через схему совпадения 19. Одновременно этим же импульсом через схему совпадения 64 сбрасывается в нуль 1риггер 86, запрещая прохождение импульса через схему совпадения 78. С приходом первого синхроимпульса триггер перезаписи 28 разрешает прохождение второго синхроимпульса через схему, совпадения 35 В то же время первый синхроимпульс через инвертор 43 поступает на вход схемы совпадения 49. Однако, поскольку на второй вход этой схемы с триггера вычитания 55 поступает запрещающий сигнал, на вход 61 реверсивного счетного блока 60 импульс не проходит. Второй синхроимпульс через схемы совпадения 35 и 71 перебрасывает триггер 55 в состоя1ше, разрешающее прохождение сигнала через схему совпадения 49 и запрещающее прохождение сигнала через схему совпадения 50. С приходом следующего илйтуль i с выхода 3 формирователя импульсных последовательностей 1 процесс прохождения сигнала по этому каналу аналогичен описанному выше, и происходит очередной переброс триггера вычитания, а на вход 62 реверсивного счетного блока сигнал не поступает. Таким образом, при поочередном приходе импульсных последовательностей по двум каналам сигналы на входы 61 и 62 реверсивного счетного блока 60 не поступают. Если же на какой-то из каналов пришло подряд два или более импульсов, то они попадают на один из входов блока 60, так как с окончанием первого импульса .триггер ВЬ1ЧИтания 55 устанавливается в состояние, разрешающее прохождение импульсов соответствующего канала, и реверсивный счетный блок 60 фиксирует разницу числа импульсов по двум каналам. Во втором cviyiiie отсчет импульсных последовательностей начинается с выхода 3 формирователя ). При )1()м первый импульс, поступающий на Kxo.i l-i запоминающего триггера 12 с задержкой во времени, определяемой параметрами дифференцирующего звена 83, через инвертор 75, дифференцирующее звено К., схему совпадения 78, инвертор 68 и схему ci падения 71 поступает на вход 57 триггера 55 и устанавливает его в состояние, запрещающее прохождение импульса через схему совпадения 50 на вход реверсивного счетного блока 60. Одновременно этим же импульсом через схему совпадения 64 триггер 86 перебрасьтается в состояние, запрещающее прохождение последующих импульсов с дифференцирующего звена 83 через схему совпадения 78. В дальнейшем схема работает, как было описано в первом случае.. Предложенное устройство позволяет достоверно определять величину и знак разности част6тнь1х ймпульснь1х последовательностей независимо от величины абсолютных значений частот входных импульсных последовательностей, обладает высокой надежностью в работе, определяемой исключением вероятности одновременного прихода счетных им11ульсов на входы реверсивного счетного блока. Формула изобретения Отсчетно-измерительное устройство, содержащее два формирователя частотно-импульсных .последовательностей, генератор тактовых импульсов, состоящий из задающего генератора и подключенного к его выходу шагового распределителя тактовых импульсов, два блока синхронизации, каждый из которых включает в себя за:поминающий триггер, первым входом подключенный к выходу одного из формирователей частотно-импульсных последовательностей, н нервую схему совпадения, одним Из входов подключенную к выходу запоминающего триггера, а вторым входом - к первому управляющему выходу генератора тактовых импульсов, дискретный фнльтр, состоящий из двух ннверторов, входами подключенных к вь1ходам первых схем совпадения соответствующих блоков синх15онизации, двух схем совпадения, первыми входами подключенных к выходам инверторов, триггера вычитания с раздельными входами, своими выходами подключенного ко вторым входам схем совпадения дискретного фильтра, и реверсивный счетный блок, входами подклгоченный к выходам схем совпадения дискретного фильтра, отличающееся тем, что, с целью повышения надежности работы, в него введены логический блок, содержащий четыре схемы совйадёния, три инвертора, чриггер с раздельными входами, дифференциальную цепь и блок установки в исходное состоятше, причем первый вход первой схемы совпадения подклю7746

чен к третьему входу первой схемы совпадения первого блока синхронизации и выходу первого формирователя частотных импульсных последовательностей, выход первого инвертора подключен ко второму входу первой схемы

совпадения и к первому входу второй схемы совпадения, выход второй схемы совпадения соединен с первым входом триггера вычитания дискретного фильтра, вход второго инвертора подключен к третьему входу пе|)вой схемы совI падения второго блока синхронизации, к выходу второго формирователя частотно-импульсных последовательностей и к первому входу третьей схемы (ювпадения, выход которой соединен со входом первого инвертора, вход дифференЩ1рующег6 звена подключен к вькоду второго инвертера, а выход - ко второму входу третьей схемы совпадения, один из входов триггера с раздельными входами подключен к выходу первой схемы совпадения, а выход триггера

. соединен с третьим входом третьей схемы совпадения, выход блока установки исходного ш 8

стояния подключен ко второму входу триггера с раздельными входами и к первому входу четвертой схемы совпадения, выход которой соединен со вторым входом триггера вычитания дискретного фильтра; кроме того, в каждый из блоков синхронизации введен триггер перезаписи, первым входом подключенный к выходу первой схемы совпадения блока синхронизации, а вторым входом соединенный с выходом запоминающего триггера, и вторая схема совпадения, первым входом подключенная к выходу триггера перезаписи, вторым входом соединенная со вторым управляющим выходом генератора тактовых импульсов, а выходом подключенная ко второму входу запоминающего триггера, причем вторая схема совпадения первого блока синхронизации выходом подключена ко второму входу второй схемы совпадения логического блока, а вторая схема совпадения второго блока синхронизации выходом подключена ко второму входу четвертой схемы совпадения логического блока.

«

53 «

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Фазосдвигающее устройство | 1981 |

|

SU957124A1 |

| Цифровой фазометр | 1977 |

|

SU690407A1 |

| Устройство для измерения качества канала связи | 1979 |

|

SU788400A1 |

| Устройство тактовой синхронизации с дискретным управлением | 1979 |

|

SU951739A1 |

| Цифровой фазометр с постоянным измерительным временем | 1985 |

|

SU1270719A1 |

| Устройство для сравнения периодов следования импульсов | 1986 |

|

SU1328932A1 |

| ИМПУЛЬСНЫЙ РАДИОЛОКАТОР | 1985 |

|

SU1840927A1 |

| Цифровое устройство для управления инвертором с квазисинусоидальным напряжением | 1983 |

|

SU1089756A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

Авторы

Даты

1980-07-05—Публикация

1978-02-15—Подача