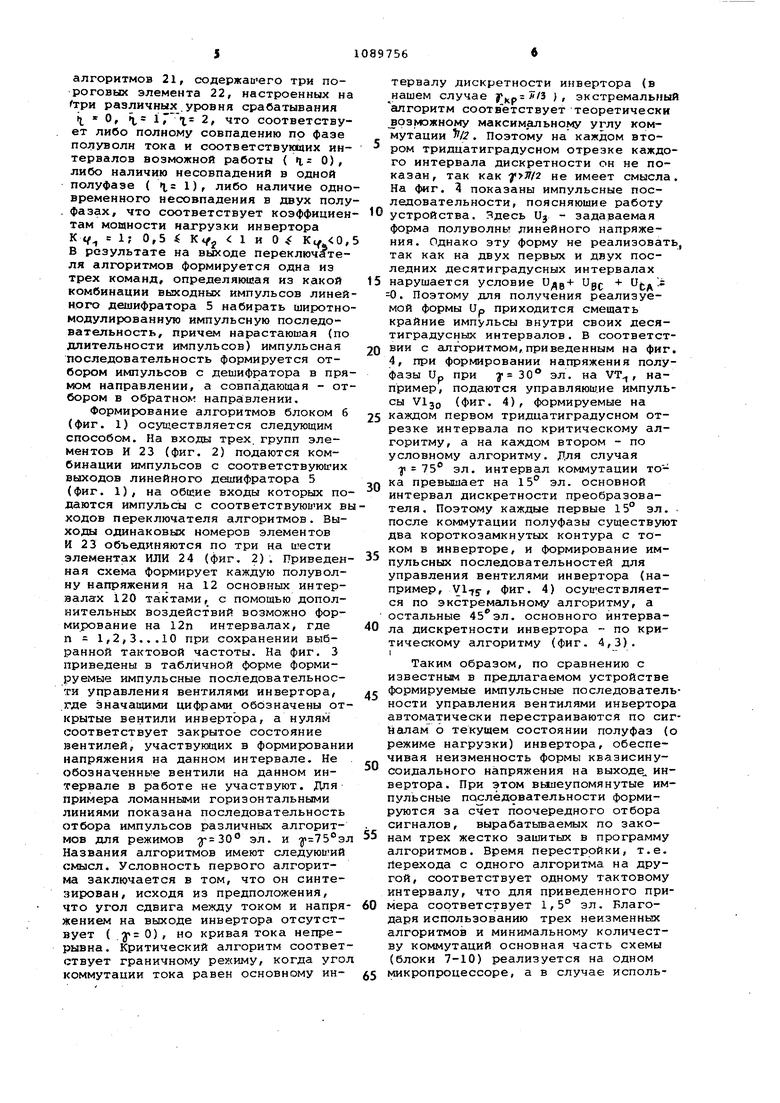

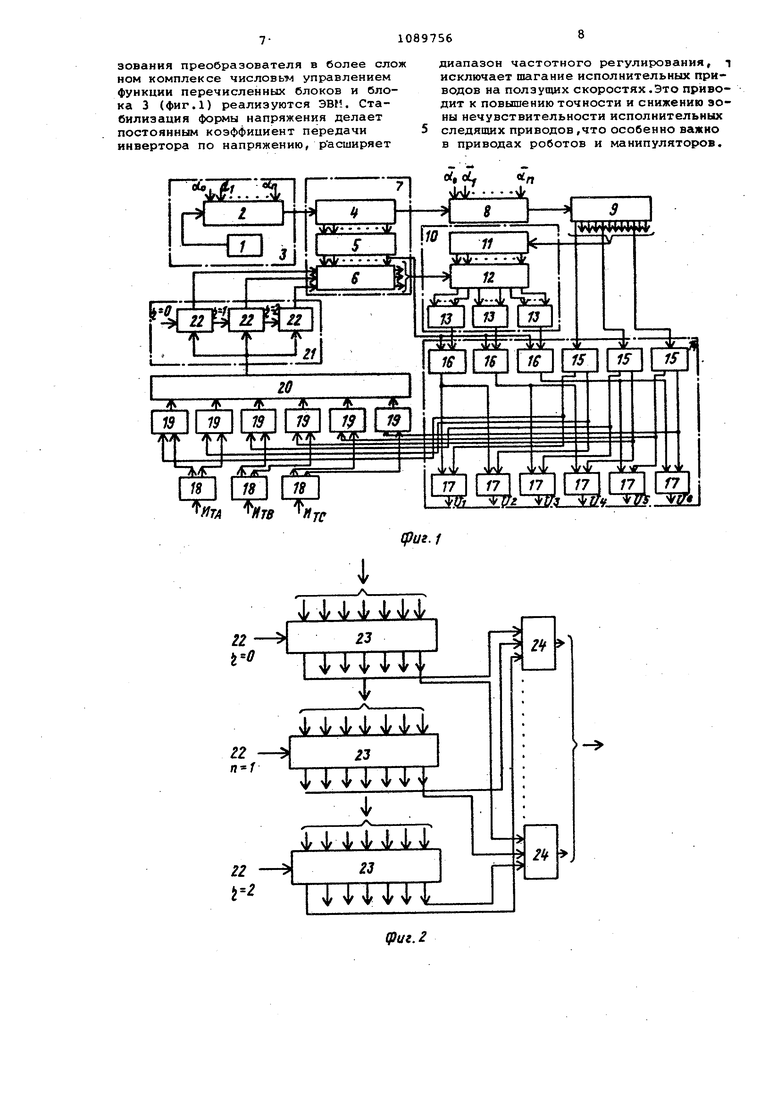

Изобретение относится к электро технике, а именно к системам управ ления автономными инверторами напря жения, и может быть особенно эффективным в частотно-регулируемых ;)лек ропринодах с управлением от микропроцессоров и миниЭВМ. Известна цифровая схема управления инвертором напряжения/ содержащ преобразователь код-частота, два реверсивных счетчика с дешифраторами, формирователь тактовых интервалов, распределитель и переключатель кратности tlJ. Эта система обладает чрезмерной сложностью из-за нерационального использования счетчиков, а качество выходного напряжения невысоко. При необходимости формирования трехфазной системы управляющих импульсов в известном устройстве требуется двенаддать реверсивных счетчиков и сложная схема формирователя на выхо распределителя. Кроме того,- в известном устройстве образованы замкнутые контура, например, выход преобразователя аналог-код, вход преобразователя аналог-код. Это может из-за запаздывания привести к нарушению тактовой синхронизации всей системы и к появлению сбоев. Наиболее близким по структуре, алгоритму функционирования и достигаемому результату к изобретению яв ляется цифровое устройство для управления инвертором напряжения, содержащее генератор, управляемый кодом, включающий в себя последовател но соединенные генератор тактовой частоты и управляемь делитель час тоты, формирователь квазисинусоидал ного напряжения, включающий в себя последовательно соединенные счетчик и линейнЕ.й. дешифратор, переключател кратности, распределитель, логический блок, состоящей из двух групп ячеек ИЛИ и ячеек И, и формировател включающий в себя первую и вторую группы триггеров, выходами соединен ных с входами ячеек И формирователя, причем выход выщеупсмянутого ге нератора соединен с входом формирователя квазисинусоидального напряже ния, первый вьжод которого соединен с одним из входов переключателя кра ности, а второй выход связан с первым входом логического блока,- выход переключателя кратности соединен с входом распределителя, выходы которого подключены к второму входу ло1-ического блока, кроме того, первый пятый и десятый выходы распределителя соединены с входами первой гру пы триггеров формирователя, в то время как соответствующие входы второй группы триггеров формирователя связаны с седьмым выходом формирователя квазисинусоидального напряжения и с выходами логического блока С21. Известное устройство не содержит аналоговых элементов, основная часть алгоритма просто реализуется на микропроцессоре, а на выходе устройства формируется шесть последовательностей управлякадих импульсов, модулированных по закону синуса, что улучшает форму выходного напряжения инвертора. Основным недостатком известного устройства является зависимость формы выходного напряжения и тока инвертора от коэффициента нагрузки, что приводит к снижению точности частотно-регулируемых приводов и зависимости коэффициента передачи бт нагрузки. Цель изобретения - улуч1ление формы напряжения на выходе инвертора и обеспечение независимости формы напряжения от режима нагрузки инвертора. - . Для достижения этой цели устройство для управления инвертором, содержащ.ем преобразователь код-частота, формирователь квазисинусоидального напряжения, включающий счетчик, к выходу которого подключен линейный дешифратор, к входу счетчика подключен преобразователь код-частота, к вЕлходу - вход управляемого кодом переключателя кратности, выходом подключенного к входу распределителя, логический блок, выполненный на первых элементах ИЛИ, подключенных через первые входы соответствующих элементов И к входам трех вторых элементов ИЛИ, выходы распределителя подключены к соответствующим первым элементам ИЛИ, первый, пятый и десятый выходы распределителя подключены к входам трех триггеров со счетным входом выходного формирователя, одни входы трех RS-триггеров с прямым и инверсным выходами которого подключены к выходам трех вторых элементов ИЛИ, выход каждого RS-триггера выходного формирователя подключен к первым входам двух соответствующих элементов И выходного формирователя, к вторым входам которых подключены выходы соответствующего триггера со счетным входом,снабжено датчиками положительной и отрицательной полуволн токов инвертора, элементами И-НЕ по числу всех указанных датчиков, сумматором, тремя пороговыми блоками, а формирователь квазисинусоидального напряжения - тремя группами элементов И и элементами ИЛИ, выходы датчиков положительной и отрицательной полуволн токов инвертора подключены к первЕЛ11 входам соответствую11 их элементов И-НЕ, вторые входы которых подключены к прямым и инверсным выходам соответствуьэших RS-триггеров. выходы через сумматор - к входам пороговых блоков, выхода которых по ключены к первым входам элементов И схютветствуюшей группы формирователя кваэисинусоидального напряжения, вторые входы которых подключены к выходам линейного дешифратора, выходы одноименных элементов И всех груп объединены через элементы ИЛИ, выходы которых подключены к вторым вхо дам соответствующих элементов И логи ческого блока. На фиг, 1 приведена схема устрой ства; на фиг. 2 - схема формирователя вспомогательных алгоритмов; на фиг. 3 - таблица вспомогательных алгоритмов; на фиг. 4 - диаграммы работы устройства. Схема устройства (фиг. 1) содержит генератор 1 тактовых импульсов, счетчик 2, образующий с генератором тактовых импульсов генератор, управляемый кодом, и выполняющий функции преобразователя 3 код-частота, последовательно соединенные счетчик 4 линейный дешифратор 5 и формирователь 6 вспомогательных алгоритмов, образующие формирователь 7 квазисинусоидального напряжения, делитель, управляемый кодом и выполненный на счетчике 8, распределитель 9 импульсов, логический блок 10, собранный на последовательно соединенных элементах И 12 и элементах ИЛИ 13, формирователь 14 импульсов, содержа1;ий первую группу триггеров 15 со счетным входом, вторую группу RS-триггеров 16 и элементы И 17, датчики 18 положительного и отрицательного полу волн токов инвертора элемента И-НЕ 19, сумматор 20, переключатель 21 алгоритмов, содержащий три пороговых блока 22. Формирователь 6 вспомогательных алгоритмов (фиг. 1) содержит три группы элементов И 23 (фиг.2), выходы соответствующих номеров которых объединены элементами ИЛИ 24. На фиг. 4 приведено задаваемое напряжение полуфазы Uj , реализуемое напряжение Up , а также отпирающие импульсы одного транзистора при (Vl.. 4), для эл. (Viy,) и для эл. () . Устройство работает следуюсим образом. Импульсы с выхода генератора 1 тактовой частоты (фиг. 1) поступают на счетный вход счетчика 2 импульсов на параллельные входы которого при каждом его переполнении записьшается инверсный код требуемой частоты (S-i,Ai-- )- Таким образом реализуется простая схема управляемого делителя частоты, в совокупности с генератором тактовой частоты выполняющая функции преобразователя 3 кодчастота. с вг-хода преобразова теля код-частота поступает на вход счетчика 4, который вместе с линейным дешифратором 5 и формирователем 6 вспомогательных алгоритмов вьтюлняет функции формирователя 7 квазисинусоидального напряжения, т.е. формирует широтно-модулированные импульсньае последовательности, обеспечивающие требуемую форму напряжения на выходах инвертора. Выход счетчика 4 поступает на вход переключателя 8 кратности, выполненного на счетчике, образующем управляемый кодом (ot olj-- ц) делитель, причем изменение коэффициента деления задается тем же кодом, что и задание частоты. Переключатель кратности формирует импульсы переключения позиций распределителя 9, с кратростью (по частоте), пропорциональной величине входной частоты, задаваемой кодом. Все двенадцать выходов распределителя поступают на входы логического блока 10 (входы 1-й группы элементов ИЛИ 11), на другие входы которого (входы элементов И 12), подается одна из трех импульсных последовательностей (соответствуюц-их одному из трех алгоритмов переключения вентилей инвертора) с выходов формирователя 7 квазисинусоидального напряжения. Импульсы с первого, пятого и десятого выходов распределителя, а также с выходов логического блока поступают на соответствующие входы формирователя 14, причем импульсы с распределителя поступают на входы 1-й группы триггеров 15, а импульсы с логического блока - на входы второй группы триггеров 16. На вьходе триггеров 15 формируются импульсы интервала возможного включения вентилей инвертора, а на выходах триггеров 16 импульсы, модулированные по требуемому закону. Эти две системы импульсов объединяются на входах элементов И 17, с которых импульсные последовательности поступают на выходные каскады системы управления вентилями инвертора. Одновременно с измерительных элементов (в схеме использованы шунты) сигналы и-гд, UTB. тс (Фиг. 1) поступают на входы датчиков 18, на выходах которого формируются шесть прямоугольных импульсных последовательностей, совпадающих по фазе с полуволнами токов на выходе инвертора. Эти импульсные последовательности подактся на первые входы элементов И 19, выполняюиих функции датчиков состояния полуфаз инвертора, а на вторые входы которых поступают импульсы с выходов триггеров 15, определяющие интервалы возможной работы вентилей инвертора. Сигналы с выходов дп- чиков состояния полуфаа через сумматор 20 подаются на вход переключателя

алгоритмов 21, содержацего три пороговых элемента 22, настроенных на три различных.уровня срабатывания IOf I i 1- 2f что соответствует либо полному совпадению по фазе полуволн тока и соответствукедих интервалов возможной работы (Ч- 0), либо наличию несовпадений в одной полуфазе ( цг 1), либо наличие одновременного несовпадения в двух полу. фазах, что соответствует коэффициентам мощности нагрузки инвертора К / 1; 0,5 Ktfy 1 и О Ki 0, В результате на выходе переключателя алгоритмов формируется одна из трех команд, определяющая из какой комбинации выходных импульсов линейного дешифратора 5 набирать широтномодулированную импульсную последовательность, причем нарастаюшая (по длительности импульсов) импульсная последовательность формируется отбором импульсов с дешифратора в прямом направлении, а совпадающая - отбором в обратном направлении,

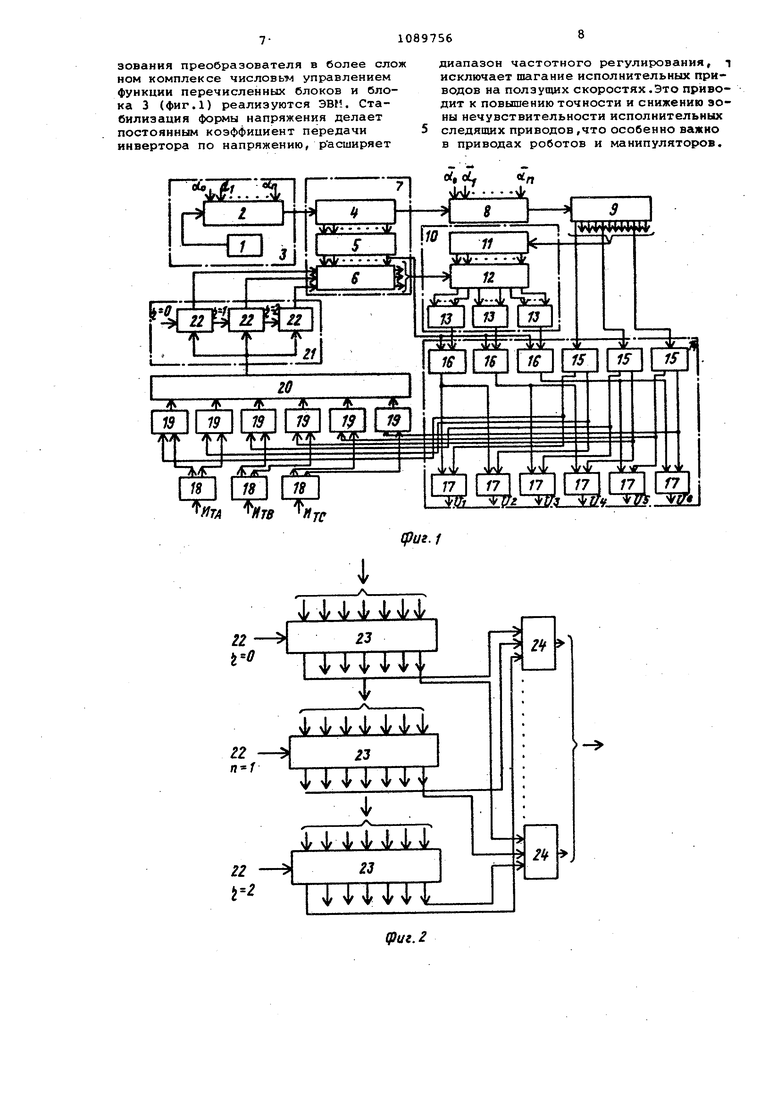

Формирование алгоритмов блоком б (фиг. 1) осуществляется следующим способом. На входы трех, групп элементов И 23 (фиг. 2) подаются комбинации импульсов с соответствующих выходов линейного доыифратора 5 (фиг. 1), на общие входы которых подаются импульсы с соответствуювих выходов переключателя алгоритмов. Выходы одинаковых номеров элементов И 23 объединяются по три на шести элементах ИЛИ 24 (фиг. 2). Приведенная схема формирует каждую полуволну напряжения на 12 основных интерзэалах 120 тактами, с помощью дополнительных воздействий возможно формирование на 12п интервалах, где п 1,2,3...10 при сохранении выбранной тактовой частоты. На фиг. 3 приведены в табличной форме формируемые импульсные последовательности управления вентилями инвертора, где значащими цифрами обозначены открытые вентили инвертора, а нулям соответствует закрытое состояние вентилей, участвуквдих в формировании напряжения на данном интервале. Не обозначенные вентили на данном интервале в работе не участвуют. Для примера ломанными горизонтальными линиями показана последовательность отбора импульсов различных алгоритмов для режимов эл. и у 75°эл Названия алгоритмов имеют следующий смысл. Условность первого алгоритма заключается в том, что он синтезирован, исходя из предположения, что угол сдвига между током и напряжением на выходе инвертора отсутствует ( у 0) , но кривая тока непрерывна. Критический алгоритм соответствует граничному , когда угод коммутации тока равен основному интервалу дискретности инвертора (в нашем случае у, ), экстремальный алгоритм соответствует теоретически возможному максимальному углу коммутации /2. Поэтому на каждом втором тридцатиградусном отрезке каждого интервала дискретности он не показан, так как не имеет смысла. На фиг. Д показаны импульсные последовательности, поясняющие работу устройства. ;Чдесь Uj - задаваемая форма полуволны линейного напряжения. Однако эту форму не реализовать, так как на двух первых и двух последних десятиградусных интервалах нарушается условие идв+ Upj. + . Поэтому для получения реализуемой формы Up приходится смещать крайние импульсы внутри своих десятиградусных интервалов. В соответствии с алгоритмом,приведенным на фиг. 4, при формировании напряжения полуфазы Up при -уг 30° эл. на VT , например, подаются управляющ.ие импульсы VljQ (фиг. 4), формируемые на каждом первом тридцатиградусном отрезке интервала по критическому алгоритму, а на каждом втором - по условному алгоритму. Для случая

f эл. интервал коммутации тока превышает на 15 эл. основной интервал дискретности преобразователя. Поэтому каждые первые 15° эл. после коммутации полуфазы существуют два короткозамкнутых контура с током в инверторе, и формирование импульсных последовательностей для управления вентилями инвертора (например, Vlfj-f фиг. 4) осуществляется по экстремальному алгоритму, а остальные 45эл. основного интервала дискретности инвертора - по критическому алгоритму (фиг. 4,3). I

Таким образом, по сравнению с известным в предлагаемом устройстве формируемые импульсные последовательности управления вентилями инвертора автоматически перестраиваются по сигйалам о текущем состоянии полуфаз (о режиме нагрузки) инвертора, обеспечивая неизменность формы квазисинусоидального напряжения на выходе инвертора. При этом вьшеупомянутые импульсные последовательности формируются за счет поочередного отбора сигналов, вырабатываемых по законам трех жестко зашитых в программу алгоритмов. Время перестройки, т.е. Перехода с одного алгоритма на другой, соответствует одному тактовому интервалу, что для приведенного при0 мера соответствует 1,5° эл. Благодаря использованию трех неизменньлх алгоритмов и минимальному количеству коммутаций основная часть схемы (блоки 7-10) реализуется на одном

5 микропроцессоре, а в случае использования преобразователя в более слож ном комплексе числовьм управлением функции перечисленных блоков и блока 3 (фигЛ) реализуются ЭВМ. Стабилизация формы напряжения делает постоянным коэффициент передачи инвертора по напряжению, расширяет

ПЖШП

Tf(

п

ф Л у ф у 1/ Ф

диапазон частотного регулирования, т исключает шагание исполнительных приводов на ползупшх скоростях.Это приводит к повышению точности и снижению зоны нечувствительности исполнительных следящих приводов,что особенно важно в приводах роботов и манипуляторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления трехфазным транзисторным инвертором с квазисинусоидальным напряжением | 1984 |

|

SU1244772A1 |

| Способ управления трехфазным мостовым инвертором,работающим на двигатель переменного тока,и устройство для его осуществления | 1984 |

|

SU1270850A1 |

| Цифровое устройство для управления инвертором напряжения | 1981 |

|

SU985923A1 |

| Способ управления трехфазным мостовым инвертором и устройство для управления трехфазным мостовым инвертором | 1981 |

|

SU1032592A1 |

| Статический преобразователь с устройством для его управления | 1986 |

|

SU1403215A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Устройство для управления транзисторным мостовым инвертором | 1982 |

|

SU1102009A1 |

ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНВЕРТОРОМ С КВАЗИСИНУСОИДАЛЬНЫМ НАПРЯЖЕНИЕМ, содержащее преобразователь код-частота, формирователь квазисинусоидального напряжения, включаюший счетчик, к выходу которого подключен линейный дешифратор, к входу счетчика подключен преобразователь код-частота, к выходу - вход управляемого кодом переключателя кратности, вькодом подключенного к входу распределителя, логический блок, выполненный на первых элементах ИЛИ, подключенных через первые входы соответствующих элементов И к входам трех вторых элементов fUItf, выходы распределителя подключены к соответствующим первые элементаин ИЛИ первый, пятый и десятый выходы распределителя подключены к входам трех триггеров со счетным входом выходного формирователя, одни входы трех RS-триггеров с прЯ1лам,и инверсным вы ходами которого подключены к выходам трех вторых элементов ИЛИ, выход каждого RS-триггера выходного формирователя подключен к первым входам двух соответствуницих элементов И выходного формирователя, к вторьм входам которых подключены выходы соответствующего триггера со счетным входом, отличающееся тем, что, с целью улучшения формы напряжения на выходе инвертора и обеспечения независимости формы от режима нагрузки, оно снабжено датчиками положительной и отрицательной полуволн токов инвертора, элементами И-НЕ по числу всех указанных датчиков, сумматором, тремя пороговыми блоками, а формирователь квазисинусоидального напряжение - тремя груп(/) пами элементов И и элементами ИЛИ, причем выходы указанных датчиков подключены к первым входам соответcTBSTOffiHX элементов И-НЕ, вторые входы которых подключены к прямым и инверсньм выходам соответствующих RS-триггеров, а выходы через сумматор - к входам пороговых блоков, выходы пороговых блоков подключены к первым входам элементов И соответ00 ствующей группы формирователя квази х синусоидального напряжения, вторые входы которых подключены к выходам ел линейного дешифратора, выходы одноименных элементов И всех групп объ единены через элементы ИЛИ, выходы о: которых подключены к вторым входам соответствующих элементов И логичес кого блока.

фиг. 2 От 1 колии. такта ffffum.ctfcmoft/f7Muij $ maffmox r m Условный д/rw055flumff ЛЛ 0 092 «« Qfit Критический SS5 5f$ алгоритм jsr (/ QOO 95f алеоритп / Kenuvecmto токДлит, состоя//7нии 6 тйктох ntn ozff 333 Условный алгоfffSритм у 30 QOt ЛТ.Т Критический a,4topumfi K7S Экстренольный ffffff ffff алгоритм 0т 207 30т tor 50Т SOr 70т 80т 90т «От 110т 120т h g . r i fg i r|r J- 7J yjf Л7 Л7 W gf /77 //7 /J /J /У7 ifffff ooi oai f// f/r iii J11 Of 1 ffff i« m Ш w азо озо т m WSS Iffffff f -(ff Ч9. fg Р .-.. ого 02о 011 ffrf vfff Iffff Mл 4 Тл 9/1 I л Л I Л« f л« l/lft I я « т 4МЛ I / оог k m i I t S55 5SS 555 ff05 BBS gfg WS0 i ff B /5 Tfor mr шт KOr 2wr ггот isor 2wr r/ yjf; yjf; //7; ш ix zn in ne azff оог оаг Z2Z ггг 2i2 222 ваг вгг вгг OM П9П rla9 I «0 Л Ijjj 333 Ijjj взз 033 333 41 fffff fffff fSe p50 050 wo5 m 5f 5S5 i 001 fffff OJO огг eZ2 2Z2 222 аЗЗ 033 JJJ JJJ iJJJ JJJ .003 003 03Q. 03(L /7.7 ДЗЗ W.7 .7.7.T iJ.7.7 .7.7.7 ./7Л7 1Л7Т .ЛТ/7 1Л7/ fss Bse efe ms ffOf ofo oso oss ass Ш BSS :ГiII1IIr ffffff I ifffff w 111 I 4 U7«tf aw- itff t 50S L -. m OAI iMV22 ш ЬгП ifffff ffffff I I 3ffJ I JJ 7JJ Uw fffff Iffff

%

ИГ.

7Д

30 fo 90 m зооззо sso

n

И/

Ji

Л7 Л7 5/7 m fSO m 2Л7 2W 270 ZOQ 330nsO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровая система управления инвертором напряжения | 1976 |

|

SU613476A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3304215/24-07, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| . | |||

Авторы

Даты

1984-04-30—Публикация

1983-01-12—Подача