54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СТАТИЧЕСКИХ ПАРАМЕТРОВ rffiKPOCXEM

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРИЧЕСКАЯ СХЕМА БЛОКА ОБРАБОТКИ СИГНАЛА ДАТЧИКА ИНТЕНСИВНОСТИ УЛЬТРАФИОЛЕТОВОГО ИЗЛУЧЕНИЯ | 1998 |

|

RU2154811C2 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для измерения электрических параметров интегральных микросхем | 1990 |

|

SU1775691A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Устройство для функционально-параметрического контроля электронных блоков | 1982 |

|

SU1104520A1 |

| Измеритель динамических параметров электронных блоков | 1983 |

|

SU1167550A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для определения нагрузочной способности микросхем | 2022 |

|

RU2793145C1 |

Изобретение относится к области контрольно-измерительной техники.

Известны устройства для контроля логических микросхем 1 и 2 , со- . 5 держащие генератор тестовых комбинаций, эталонную микросхему и компа- . ратор.

Недостатком данных устройств является низкая точность измерений. jQ

Наиболее близким по технической сущности к изобретению является устройство для контроля статических параметров микросхем З, содержащее блок управления, выход которого подключен ко входу эталонной микросхемы, первый компаратор и первый коммутатор. .

Недостаточная точность работы такого устройства обусловлена отсут- 20 ствием допускового контроля по верхнему и нижнему уровням проверяемых сигналов.

Целью изобретения является повышение точности работы устройства. 25

Эта цель достигается тем, что предложенное устройство содержит второй коммутатор, первый и второй источники эталонных сигналов, второй и третий компараторы, элемент

ИЛИ, стабилизатор входных сигналов, первый вход которого соединен с выходом генератора воздействий,выход через эталонный нагрузочный sjieMeHT - с его вторым входом и непосредственно с первым входом первого компаратора, соединенного вторым входом через первый коммутатор с ВЫХО.ЦОМ эталонной микросхемы и первым входом второго коммутатора, первый выход которого соединен через второй компаратор с первым входом элемента ИЛИ, второй аход которого подключен через третий компаратор ко второму выходу второго коммутатора, третий вход - с BBIXOдом первого компаратора, а выход - со входом блока управления. Выход первого источника эталонных сигналов подключен ко второму входу второго компаратора, а -выход второго источника эталонных сигналов - ко второму входу третьего компаратора, третий вход которого соединен с третьим входом второго компаратора.

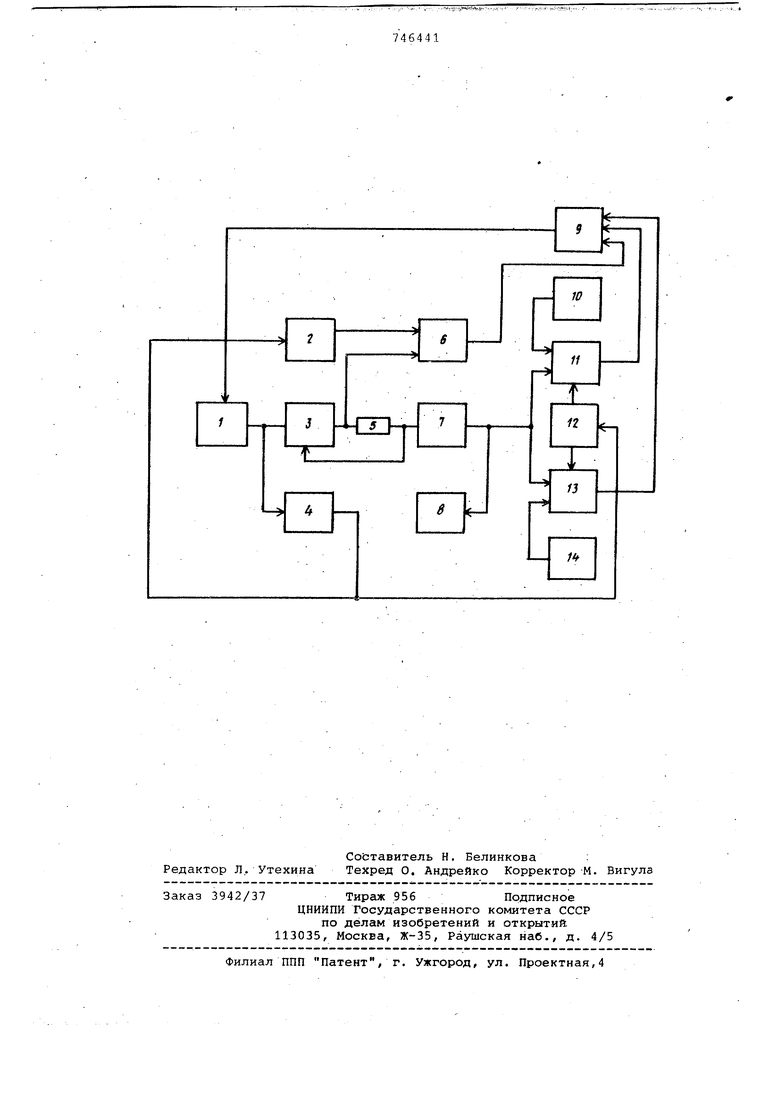

Структурная схема устройства представлена на чертеже, где обозначены блок управления 1, первый коммутатор 2, стабилизатор входных сигна лов 3, эталонная микросхема 4, эталонный нагрузочный элемент 5, первый компаратор 6, объект контроля 7, нагрузка 8, элемент ИЛИ 9, первый ис точник эталонных сигналов 10, второй компаратор 11, второй коммутатор 12 третий компаратор 13 и второй источник эталонных сигналов 14. Устройство работает следующим образом. - . Тестовые комбинации с блока 1 поступают на микросхему 4 и через ст билизатор 3 и элемент 5 на проверяемую микросхему объекта 7. Стабилизатор 3 предназначен для точного задания входных уровней О и 1 на проверяемой микросхеме. Обратная связь стабилизатора 3 берется непосредственно со входа проверяемой мик росхемы объекта 7, что обеспечивает поддержание точных значений входных напряжений. При этом падение напряжения на элементе 5 пропорционально входному току проверяемой микросхемы, а напряжение на выходе стабилизатора 3 равно сумме напряжения на входе объекта 7 и падения напряжения на элементе 5. Учитывая, напряжение на входах микросхем принимает дискретные значения (О и 1), а напряжение на выходе стабилизатора 3 пропорционально входному току проверяемой микросхемы объекта 7, допусковый контроль величины входного тока может быть осуществлён сравнением напряжения на выходе стабилизатора 3 с опорным Сравнение производится компаратором 6, на второй эталонный вход которого подано напряжение с коммутатора 2, управляемого выходным напряжением эталонной микросхемы 4. В случае превышения входным током объекта 7 заданных пределов на выходе компаратора 6 образуется сигна который через элемент ИЛИ 8 останавливает работу блока 1. Выходные напряжения проверяемой микросхемы 7 при подключенной нагру ке 8 контролируются компараторами 11 и 13, на вторые (эталонные) входы которых подано напряжение с исто ников 10 и 14. Выбор компаратора производится коммутатором 12, который управляетс выходными сигналами микросхемы 4. Введение двух ТсоМпараторов и дву опорных источнйкЬё 11бзволяёт получить любую заданнуто точность работы устройства, которая определяется то ностью эадайия ойорных уровней и по реи1ностью 1 оМгГй|Гй брШТ В случае пр вышений яаходным сигналом проверяем микросхемы объекта 7 заданных источ никами 10 и 14 уровней на выходах компараторов 11 или 13 образуются сигналы, которые, проходя через элемент ИЛИ 9, Останавливают работу блока 1 в состоянии, при котором произошло рассогласование. Проверяемая микросхема 7 считается годной в случае отсутствия сигнала остановки блока 1 за полный периЬд его работы. Точность работы предлагаемого устройства по сравнению с известным повышена за счет использования второго и третьего компараторов и первого и второго источников этс1лонных сигналов . Формула изобретения Устройство для контроля статических параметров микросхем, содержащее блок управления, выход которого подключен ко входу эталонной микросхемы, первый компаратор и первый коммутатор, отличающееся тем что, с целью повышения точности работы устройства, оно содержит второй коммутатор, первый и второй источники эталонных сигналов, второй и третий компараторы, элемент ИЛИ, стабилизатор входных сигналов, гкрвый вход которого соединен с выходом генератора воздействий,выход через эталонный нагрузочный элемент - с его вторым входом и непосредственно с первым входом первого компаратора, соединенного вторым входом через первый KOMiviyTaTop с выходом эталонной микросхемы и первым входом второго коммутатора, первый выход которого соединен через второй компаратор с первым входом элемента ИЛИ, второй вход которого подключен через третий компаратор ко второму выходу второго коммутатора, третий вход - с выходом первогокомпаратора, а выход - со входом блока управления, выход первого источника эталонных сигналов подключен ко второму входу второго компаратора, а выход второго, источника эталонных сигналов - ко второму входу третьего компаратора, третий вход которого соединен с третьим входом второго компаратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 337738, кл. G 05 В 23/02, 1972. 2.Авторское свидетельство СССР № 530287, кл. G 01 R 31/28, 1977. 3.Авторское свидетельство СССР кл. G Об F 11/04, .1975 (прототип).

Авторы

Даты

1980-07-05—Публикация

1978-04-10—Подача