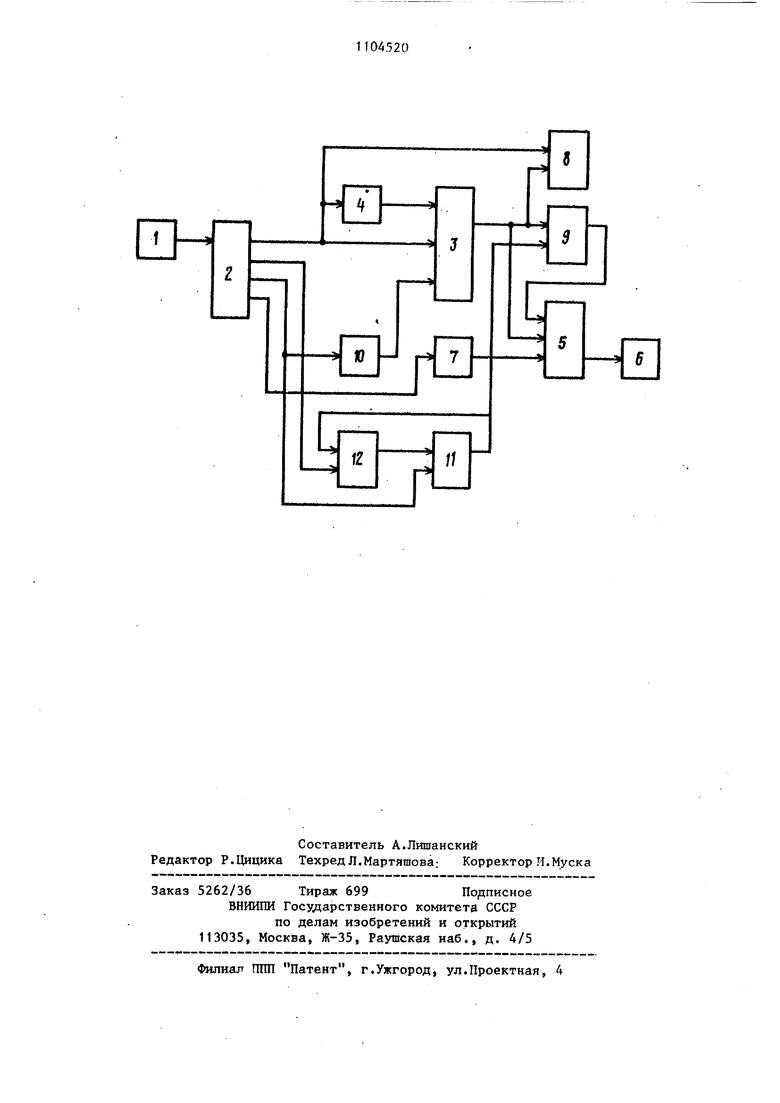

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функциональнопараметрического контроля смонтированных гибридных электронных блоков, содержащих логические элементы и ста билизаторы напряжения, а также для входного контроля логических блоков и стабилизаторов напряжения, в том числе интегральных микросхем, у потребителя . Известно устройство для контроля логических блоков, содержащее блок управления, генератор псевдослучайных кодов, блок свертки и накапливаю щий сумматор Известно устройство для контроля стабилизаторов напряжения, содержащее блок вьщачи команд, блок задания уровня выходного напряжения стабилизатора, блок управления узлами устройства, блок контроля токов блок питания, блок нагрузок, коммутатор, блок допускового контроля, блок индикации и блок печати 2 у, Недостатком устройства является невозможность контроля гибридных электронных блоков, содержащих, кроме стабилизаторов напряжения, и логические элементы. Наиболее близким к изобретению является устройство для функционально-параметрического контроля логичес ких элементов, содержащее последовательно соединенные тактовьй гёнератор и первьй счетчик, первые выходы которого через коммутатор - преобраг зователь и через последовательно сое диненные ,дешифратор и коммутаторпреобразователь подключены к входам контактного блока, выходы контактного блока через коммутатор-преобразователь соединены с одними входами мультиплексора, адресные входы ко-торого через коммутатор-преобразователь подключены к выходам второго счетчика, счетный вход которого чере коммутатор-преобразователь соединен Со старшим разрядом первого счетчика, выход мультиплексора подключен к информационному входу сигнатурного анализатора З . Недостатком известного устройства является невозможность контроля гибридных электронных блоков, содержащих, кроме логических элементов, и стабилизаторы напряжения. Целью изобретения является расишрение облас;ги применения устройства, т.е. наделение его функциями контроля гибридных электронных блоков, содержащих .как логические элементы, так и стабилизаторы напряжения (в том числе имеющие логику управления, например, входы электронного включенияотключения) . Указанная цель достигается тем, что в устройство, содержащее последовательно соединенные тактовый генератор и первый счетчик, подключенный первыми выходами к входам контактного блока и входу дешифратора, соединенного выходом с входом контактного блока, связанного выходом с первым информационньм входом мультиплексора, соединенного выходом с входом сигнатурного анализатора, а адресным входом - с выходом второго счетчика, подключенного входом к выходу старщего разряда первого счетчика, введены блок нагрузок, блок компараторов, триггер, элемент И и формирователь тестов, подключенный выходами к входу контактного блока, входами - к третьему выходу первого счетчика, соединенного вторым вькодом с первым входом элемента И, подключенного вторым входом к прямому выходу триггера и стробирующему входу блока компараторов, а выходом - к S-входу триггера, связанного R-BXOдом с третьим выходом первого счетчика, адресный вход блока нагрузок соединен с входом дешифратора, а информационный вход - с выходом контактного блока и информационным входом блока компараторов, соединенного вькодом с вторым информационным входом мультиплексора. На чертеже приведена структурная схема устройства. Устройство содержит тактовый генератор 1 , которьй формирует тактовые сигналы рабочей частоты; первый счетчик 2, предназначенный для обеспечения перебора входных тактовых последовательностей; контактный блок 3, в который вставляется контролируемый электронный блок; дешифратор 4, необходимый для формирования тестовых сигналов для несовместимых входов контролируемого электронного блока (несовместимыми называются входы, одновременная ; подача управляющих сигналов на которые приводит к неопределенному тоянию на выходе блока); мультиплексор 5, выбирающий в каждый отрезок времени один из входных сигналов (в качестве мультиплексора в устройстве используется микросхема К155КП7 сигнатурный анализатор 6, являющийся регистратором последовательностей выходных сигнапов контролируемого электронного блока; второй счетчик 7 осуществляющий перебор адресных входов мультиплексора 5; блок 8 нагрузок, задающий токи нагрузки на выходах контролируемого электронного бло ка, величины которых определяются значениями на адресных входах блока; блок 9 компараторов, фиксирующих выход за пределы допусков выходных напряжений контролируемого электронног блока каждый компаратор блока содер жит микросхему К55С4А1, представляющую собой сдвоенный компаратор напря жения, на один вход каждого из которых падает соответствующее пороговое напряжение, другие входы обоих компараторов соединены между собой и на них поступает выходное напряжение .контролируемого электронного бло ка ;формирователь 10 тестов, обеспечивающий тестовые напряжения стандартной или специальной формы на входах контролируемого электронного блока, величины которых определяются значениями входных сигналов; триггер 11, запрещающий прохождение сигнала через блок 9 компараторов, начиная с момента изменения входного сигнала формирователя 10 тестов; эле мент И 12, устанавливающий триггер 1 в исходное состояние по фронту сигнала на втором выходе первого счетчика 2, при этом длительность запрещающего сигнала на прямом выходе триггера 11 не менее длительности переходного процесса выходных напряжений формирователя 10 тестов. Устройство работает следующим образом. При проверке конкретного электронного блока его подключают к устройству с помощью контактного блока 3. После этого включается тактовый генератор I, запускаются первый счетчик 2, дешифратор 4 и второй счетчик 7. Фармирователь 10 тестов и блок 8 нагрузок под управлением первого счетчика 2 обеспечивают формирование всех необходимых значений входных тестовых напряжений и выходных токов соответственно стабилизаторов напряжения контролируемого электронного блока. Благодаря этому осуществляется полный перебор всех необходимых стимулирующих воздействий для контролируемого гибридного электронного блока (как для входящ51х в него логических элементов, так и стабилизаторов напряжения). Выходные последовательности с выходов контролируемого электронного блока непосредственно или через блок 9 koMnapaторов последовательно подаются через мультиплексор 5 на вход сигнатурного анализатора 6, формирующего сигнату- ру электронного блока. Полученная сигнатура сравнивается с эталонной. При совпадении сигнатур контролируемый электронньй блок исправен. i Предлагаемое устройство позволяет осзга ествлять функционально-параметрический контроль гибридных электронных блоков, содержащих логические элементы и стабилизаторы напряжения (в том числе имеющие логику управления, например входы электронного включения-отключения). При этом уменьшается количество требуемых устройств и операции контроля, что обеспечивает экономию материальных затрат на обеспечение производственного контроля производимых электронный блоков и входного контроля комплектующих, сокращение требуемых производственных площадей, уменьшение обслуживающего персонала. Кроме того, повышается производительность контроля за счет уменьшения числа установок контролируемого гибридного электронного блока на устройство контроля (для электронных блоков с малым числом входов и выходов время установки элемента значительно больше времени контроля).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ЭЛЕКТРОННЫХ БЛОКОВ, содержащее последовательно соединенные тактовый генератор и первый счетчик, подключенный первыми выходами к входам контактного блока и входу дешифратора, соединенного выходом с входом контактного блока, связанного выходом с первым информационньм входом мультиплексора, соединенного выходом с входом сигнатурного анализатора, а адресным выходом - с выходом второго счетчика, подключенного входом к выходу старшего разряда первого счетчика, отличающееся тем, что, с целью расширения области применения устройства, в него введены блок нагрузок, блок KONmapaTOpoB, триггер, элемент И и формирователь тестов, подключенный вькодами к входу контактного блока, входами - к третьему выходу первого счетчика, соединенного вторым выходом с первым входом элемента И, подклю(Л ченного вторым входом к прямому выходу триггера и стробирующему входу блока компараторов, а выходом - к S-входу триггера, связанного R-BXOдом с третьим выходом первого, счетчика, адресный вход блока нагрузок соединен с входом дешифратора, а информационный вход - с выходом контактного блока и информационным входом блока компараторов, соединенного выходом с вторым информационным входом мультиплексора.

| , 1 | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Автоматический контроль транзисторных стабилизаторов напряжения | |||

| - Сборник Миниатюризация вторичных источников электропитания электронной аппаратуры | |||

| Материалы сеьшнара | |||

| М., МДНТП, 1973, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1982-12-02—Подача