электрического контакта между выводами проверяемой микросхемы и блоком переходных контактов непосредственно в процессе проведения теста и построения устройства на микросхемах ТТЛ логики. При совпадении вида ожидаемых сигналов с реальными сигналами устройство формирует признак, характеризующий наличие контакта между выводами, проверяемой микросхемы и устройством контроля, при несовпадении указанных сигналов индицируется инфор1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля параметров интегральных схем.

Цель изобретения - повьппение быстродействия.

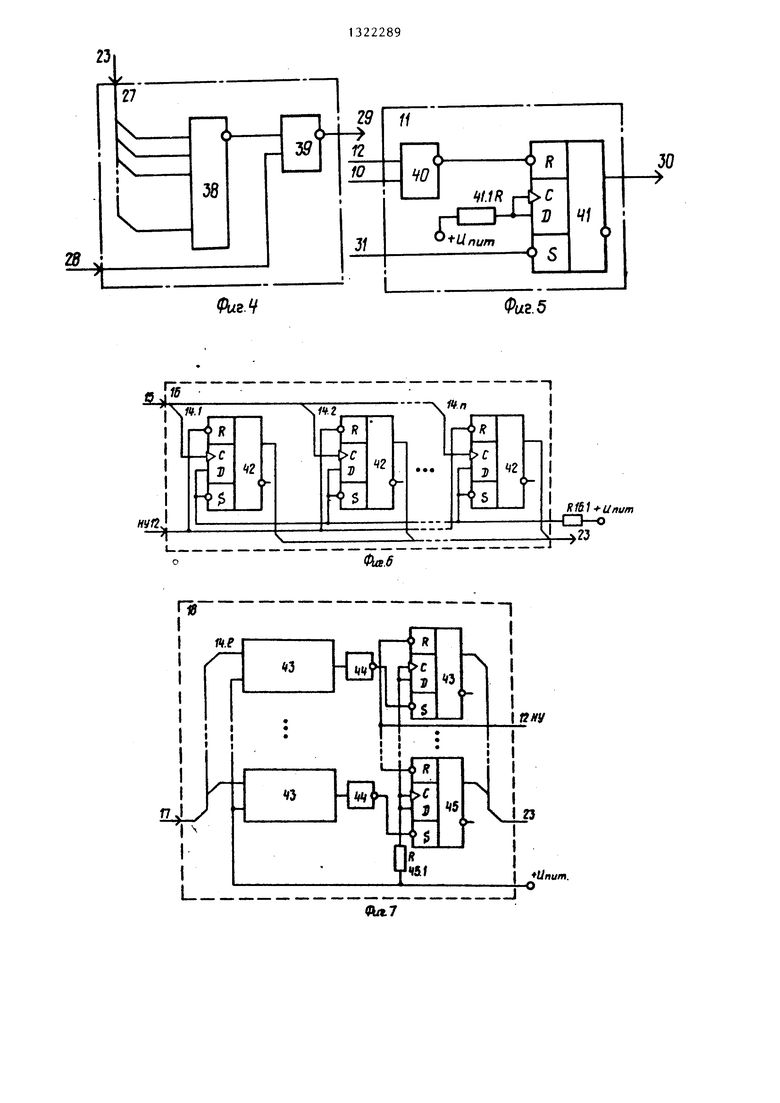

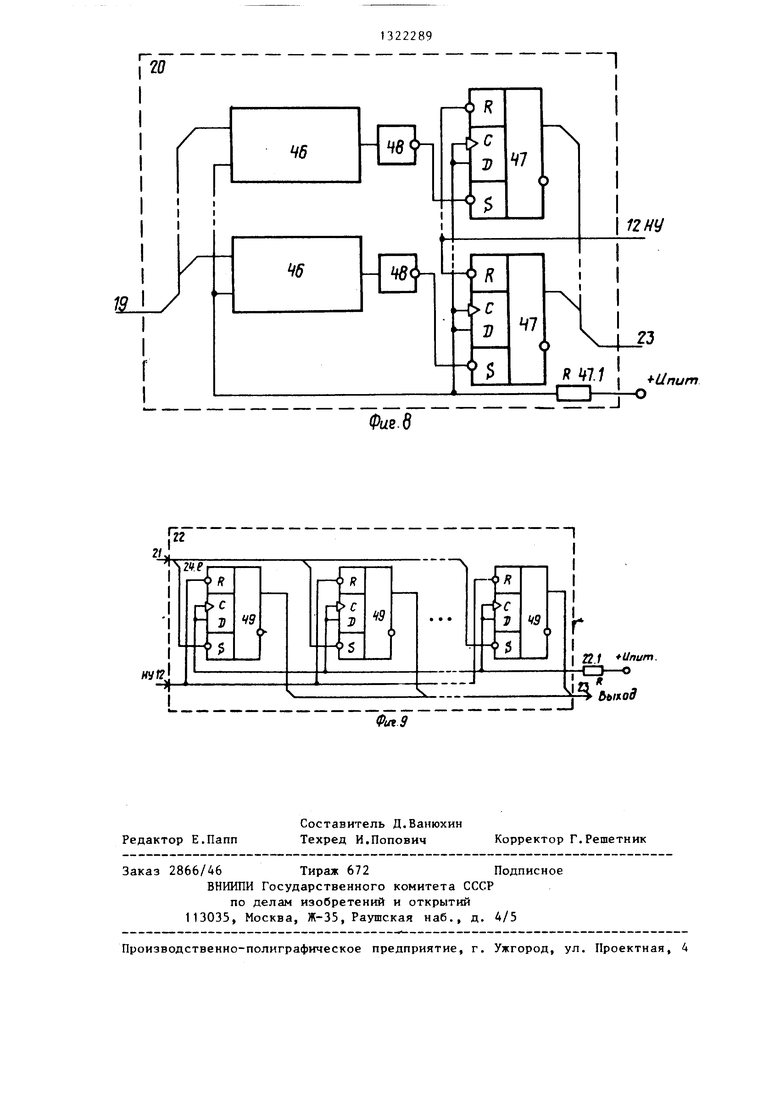

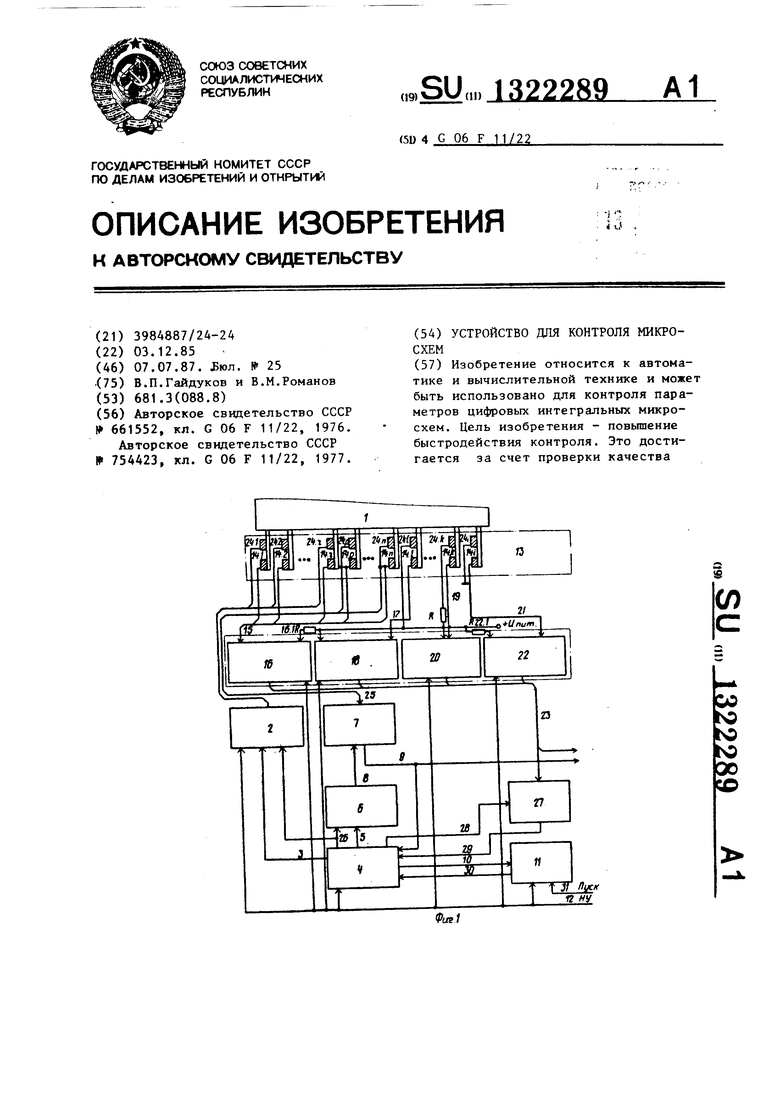

На фиг.1 представлена функциональная схема устройства для контроля микросхем ; на фиг.2 - схема блока сравнения; на фиг.З - схема блока уп- равления на фиг.4 - схема коммутатора; на фиг.З - схема блока пуска; на фиг.6 - схема первого регистра контроля контактирования; на фиг.7 - схема первого блока контроля контактирования; на фиг.З - схема второго блока контроля контактирования; на фиг.9 - схема второго регистра контроля контактирования .

Устройство (фиг.1) содержит контролируемую микросхему 1, регистр 2 воздействий, первый информационный вход 3 блока управления, блок 4 управления, второй информационный выход 5 блока управления, регистр 6 эталонных реакций, блок 7 сравнения, выходы 8 регистра эталонных реакций, выход 9 блока сравнения, выход 10 останова блока управления, блок 11 пуска, вход 12 начальной установки устройства, блок 13 переходных контактов, первую группу контактов 14 блока переходных контактов, входы 13 синхронизации, разрядов первого регистра контроля контактирования, первый регистр 16 контроля контактирования, третий согласующий резистор 16.1, второй информационный вход 17 первого блока

мация о причине останова. Устройство для контроля микросхем содержит два регистра контроля контактирования 16 и 22, два блока контроля контактирования 18 и 20, блок сравнения 7, коммутатор 27, регистры воздействий 2 и эталонных реакций 6, блок управления А, два согласующих резистора 16.1 и 22. 1, блок пуска II, содержащий триггер пуска, элемент ИЛИ-НЕ и согласующий резистор. 3 з.п. ф-лы, 9 ил.

O

5

контроля контактирования, первый блок 18 контроля контактирования, второй информационный вход 19 второго блока контроля контактирования, второй блок 5 20 контроля контактирования, второй установочный вход 21 второго регистра контроля контактирования, второй регистр 22 контроля контактирования, второй согласующий резистор 22.1, информационный выход 23 устройства, вторую группу контактов 24 блока переходных контактов, вторую группу 23 информационных входов блока сравнения, выход 26 синхронизации блока управления, коммутатор 27, управляющий вход 28 коммутатора, выход 29 коммутатора, вход пуска 30 блока управления, вход 31 пуска устройства.

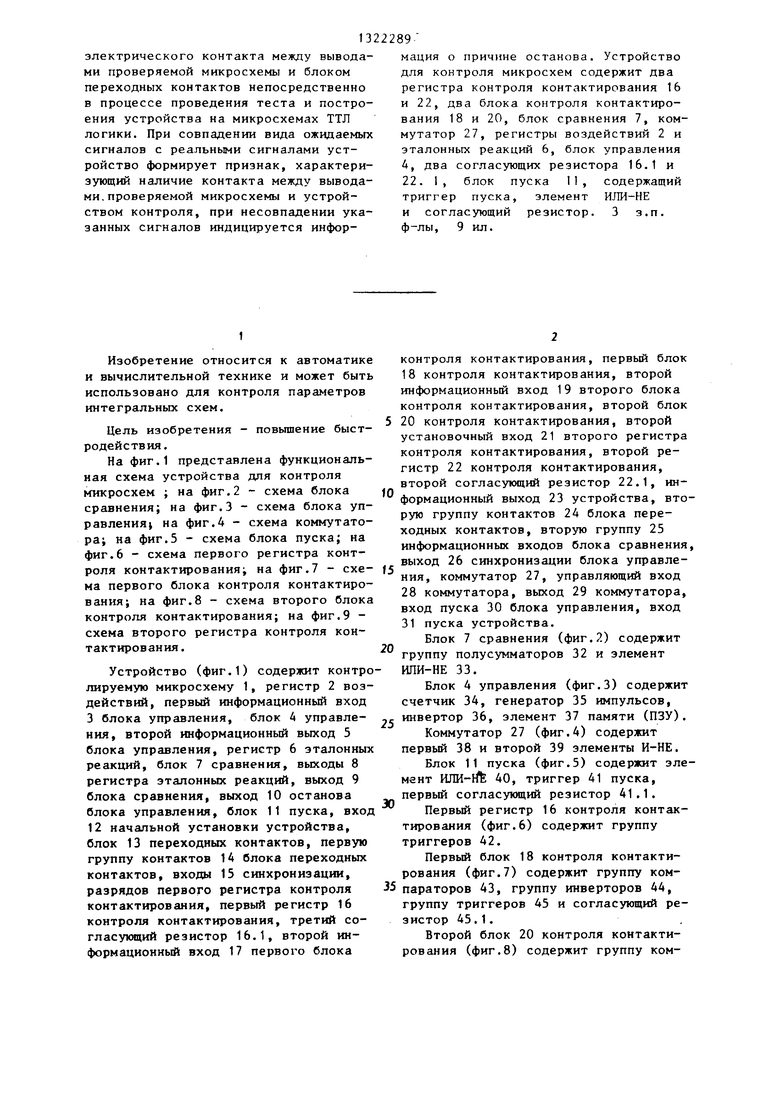

Блок 7 сравнения (фиг.2) содержит группу полусумматоров 32 и элемент ИПИ-НЕ 33.

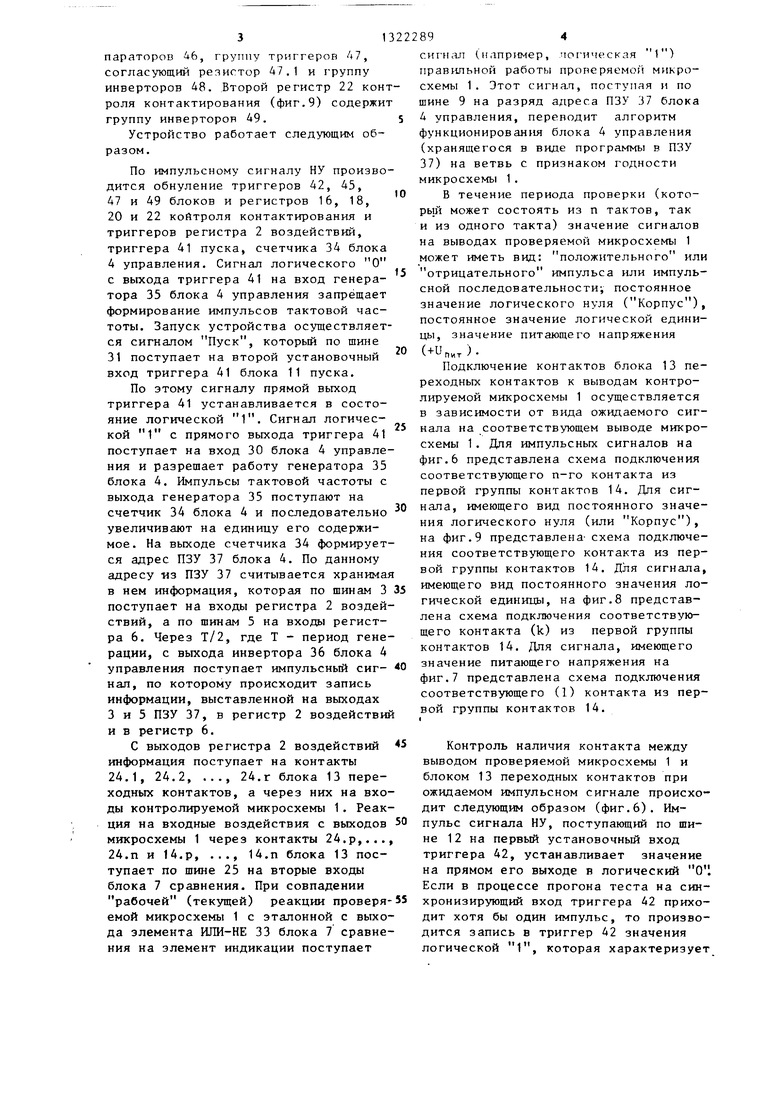

Блок 4 управления (фиг.З) содержит счетчик 34, генератор 33 импульсов, , инвертор 36, элемент 37 памяти (ПЗУ).

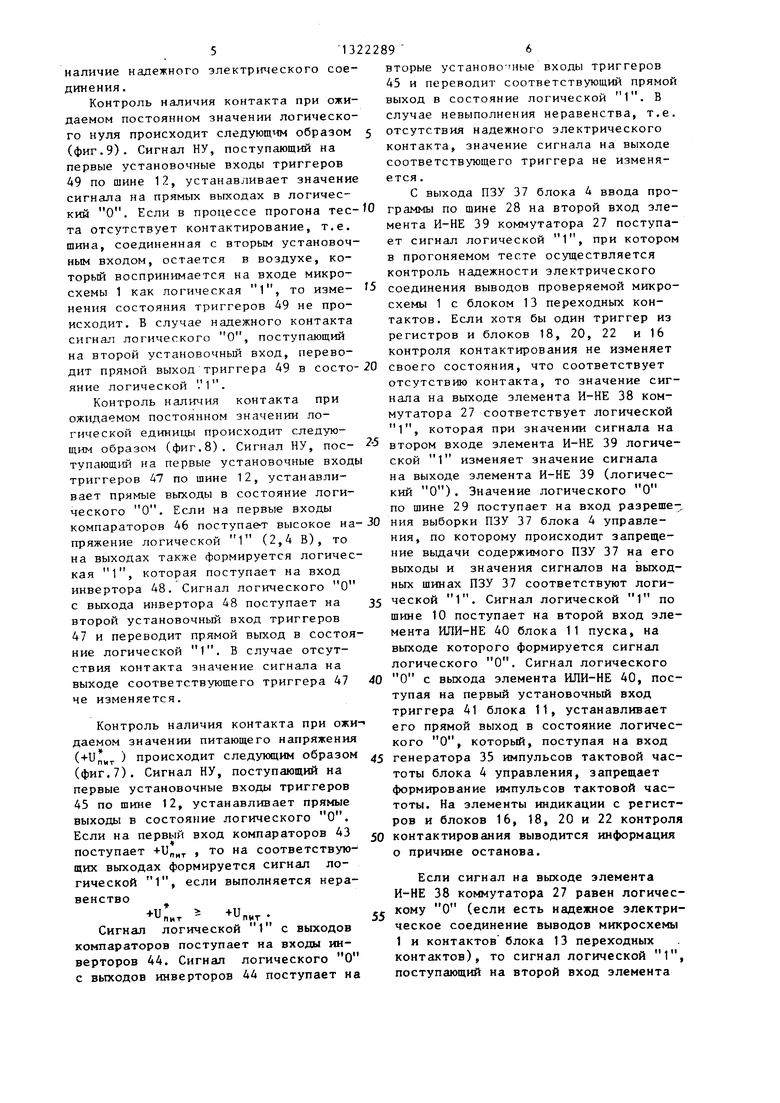

Коммутатор 27 (фиг.4) содержит первый 38 и второй 39 элементы И-НЕ.

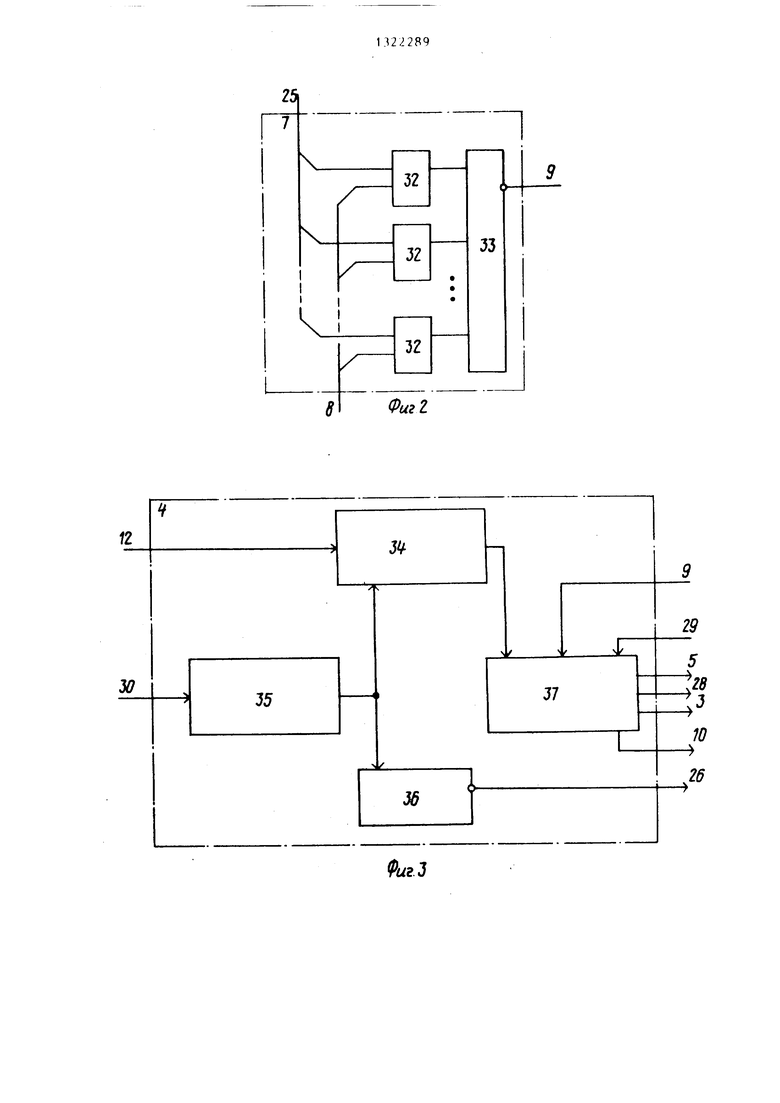

Блок 11 пуска (фиг.З) содержит элемент ИЛИ-fft 40, триггер 41 пуска, первый согласующий резистор 41.1.

Первый регистр 16 контроля контактирования (фиг.6) содержит группу триггеров 42.

Первый блок 18 контроля контактирования (фиг.7) содержит группу ком- 5 параторов 43, группу инверторов 44, группу триггеров 43 и согласующий резистор 43. 1.

Второй блок 20 контроля контактирования (фиг.8) содержит группу ком0

параторов 46, группу триггеров 47, согласующий резистор 47.1 и группу инверторов 48. Второй регистр 22 контроля контактирования (фиг.9) содержит группу инверторов 49.

Устройство работает следующим образом.

По импульсному сигналу НУ производится обнуление триггеров 42, 45, 47 и 49 блоков и регистров 16, 18, 20 и 22 койтроля контактирования и триггеров регистра 2 воздействий, триггера 41 пуска, счетчика 34 блока 4 управления. Сигнал логического О с выхода триггера 41 на вход генератора 35 блока 4 управления запрещает формирование импульсов тактовой частоты. Запуск устройства осуществляется сигналом Пуск, который по шине 31 поступает на второй установочный вход триггера 41 блока 11 пуска.

По этому сигналу прямой выход триггера 41 устанавливается в состояние логической 1. Сигнал логической 1 с прямого выхода триггера 41 поступает на вход 30 блока 4 управления и разрешает работу генератора 35 блока 4. Импульсы тактовой частоты с выхода генератора 35 поступают на счетчик 34 блока 4 и последовательно увеличивают на единицу его содержимое. На выходе счетчика 34 формируется адрес ПЗУ 37 блока 4. По данному адресу из ПЗУ 37 считывается хранимая в нем информация, которая по шинам 3 поступает на входы регистра 2 воздействий, а по шинам 5 на входы регистра 6. Через Т/2, где Т - период генерации, с выхода инвертора 36 блока 4 управления поступает импульсный сиг- нал, по которому происходит запись информации, выставленной на выходах 3 и 5 ПЗУ 37, в регистр 2 воздействий и в регистр 6.

С выходов регистра 2 воздействий информация поступает на контакты 24.1, 24.224.г блока 13 переходных контактов, а через них на входы контролируемой микросхемы 1. Реакция на входные воздействия с выходов микросхемы 1 через контакты 24.р,..., 24.п и 14.р, ..., 14.п блока 13 поступает по шине 25 на вторые входы блока 7 сравнения. При совпадении рабочей (текущей) реакции проверяемой микросхемы 1 с эталонной с выхода элемента ИЛИ-НЕ 33 блока 7 сравнения на элемент индикации поступает

0

5

0

5

5 0 5

сиг н;гл (например, лог ическая 1) правильной работы проперяемоГ микросхемы 1. Этот сигнап, поступая и по шине 9 на разряд адреса ПЗУ 37 блока 4 управления, переводит алгоритм функционирования блока 4 управления (хранящегося в виде программы в ПЗУ 37) на ветвь с признаком годности микросхемы 1.

В течение периода проверки (кото- рь1й может состоять из п тактов, так и из одного такта) значение сигналов на выводах проверяемой микросхемы 1 может иметь вид: положительного или отрицательного импульса или импульсной последовательности; постоянное значение логического нуля (Корпус), постоянное значение логической единицы, значение питающего напряжения

( + ипит)Подключение контактов блока 13 переходных контактов к выводам контролируемой микросхемы 1 осуществляется в зависимости от вида ожидаемого сигнала на соответствующем выводе микросхемы 1. Для импульсных сигналов на фиг.6 представлена схема подключения соответствующего п-го контакта из первой группы контактов 14. Для сигнала, имеющего вид постоянного значения логического нуля (или Корпус), на фиг.9 представлена- схема подключения соответствующего контакта из первой группы контактов 14. Для сигнала, имеющего вид постоянного значения логической единицы, на фиг.8 представлена схема подключения соответствующего контакта (k) из первой группы контактов 14. Для сигнала, имеющего значение питающего напряжения на фиг.7 представлена схема подключения соответствующего (1) контакта из первой группы контактов 14. I

Контроль наличия контакта между выводом проверяемой микросхемы 1 и блоком 13 переходных контактов при ожидаемом импульсном сигнале происходит следующим образом (фиг.6). Импульс сигнала НУ, поступающий по шине 12 на первый установочный вход триггера 42, устанавливает значение на прямом его выходе в логический 01 Если в процессе прогона теста на синхронизирующий вход триггера 42 приходит хотя бы один импульс, то производится запись в триггер 42 значения логической 1, которая характеризует

наличие надежного электрического соединения.

Контроль наличия контакта при ожидаемом постоянном значении логического нуля происходит следующим образом (фиг.9). Сигнал НУ, поступающий на первые установочные входы триггеров 49 по шине 12, устанавливает значение сигнала на прямых выходах в логичесвторые установо- ные входы триггеров 45 и переводит соответствующий прямой выход в состояние логической 1. В случае невыполнения неравенства, т.е. отсутствия надежного электрического контакта, значение сигнала на выходе соответствующего триггера не изменяется .

С выхода ПЗУ 37 блока 4 ввода прокий О. Если в процессе прогона тес- О граммы по шине 28 на второй вход элета отсутствует контактирование, т.е. шина, соединенная с вторым установочным входом, остается в воздухе, который воспринимается на входе микросхемы 1 как логическая 1, то изменения состояния триггеров 49 не происходит. В случае надежного контакта сигнал логического О, поступающий на второй установочный вход, переводит прямой выход триггера 49 в состо- 20 своего состояния, что соответствует

яние логической . 1.

Контроль наличия контакта при ожидаемом постоянном значении логической единиць происходит следуюской 1 изменяет значение сигнала на выходе элемента И-НЕ 39 (логический О). Значение логического О по шине 29 поступает на вход разреше-,

управлеотсутствию контакта, то значение сигнала на выходе элемента И-НЕ 38 коммутатора 27 соответствует логической 1, которая при значении сигнала на щим образом (фиг.8). Сигнал НУ, пос- втором входе элемента И-НЕ 39 логичетупающий на первые установочные входы

триггеров 47 по шине 12, устанавливает прямые выходы в состояние логического О. Если на первые входы

компараторов 46 поступает высокое на-30 ния выборки ПЗУ 37 блока 4 пряжение логической 1 (2,4 В), то на выходах также формируется логическая 1, которая поступает на вход инвертора 48. Сигнал логического О с выхода инвертора 48 поступает на второй установочный вход триггеров 47 и переводит прямой выход в состояние логической 1. В случае отсутствия контакта значение сигнала на

40

выходе соответствующего триггера 47 не изменяется.

Контроль наличия контакта при ожи-даемом значении питающего напряжения

,

ние выдачи содержимого ПЗУ 37 на его выходы и значения сигналов на выходных щинах ПЗУ 37 соответствуют логи- 35 ческой 1. Сигнал логической 1 по щине 10 поступает на второй вход элемента ИЛИ-НЕ 40 блока 11 пуска, на выходе которого формируется сигнал логического О, Сигнал логического О с выхода элемента ИЛИ-НЕ 40, поступая на первый установочный вход триггера 41 блока 11, устанавливает его прямой выход в состояние логического О, который, поступая на вход

( -Unvr ) происходит следующим образом 5 генератора 35 импульсов тактовой час(фиг.7). Сигнал НУ, поступающий на первые установочные входы триггеров 45 по шине 12, устанавливает прямые выходы в состояние логического О. Если на первый вход компараторов 43 поступает +и„„ , то на соответствующих вьпсодах формируется сигнал логической 1, если выполняется неравенство

+Unv,T ,.

Сигнал логической 1 с выходов компараторов поступает на входы инверторов 44. Сигнал логического О с выходов инверторов 44 поступает на

тоты блока 4 управления, запрещает формирование импульсов тактовой частоты. На элементы индикации с регистров и блоков 16, 18, 20 и 22 контроля 50 контактирования выводится информация

0причине останова.

Если сигнал на выходе элемента И-НЕ 38 коммутатора 27 равен логичес- кому О (если есть надежное электрическое соединение выводов микросхемы

1и контактов блока 13 переходных контактов), то сигнал логической 1, поступающий на второй вход элемента

вторые установо- ные входы триггеров 45 и переводит соответствующий прямой выход в состояние логической 1. В случае невыполнения неравенства, т.е. отсутствия надежного электрического контакта, значение сигнала на выходе соответствующего триггера не изменяется .

С выхода ПЗУ 37 блока 4 ввода промента И-НЕ 39 коммутатора 27 поступает сигнал логической 1, при котором в прогоняемом тесте осуществляется контроль надежности электрического соединения выводов проверяемой микросхемы 1 с блоком 13 переходных контактов. Если хотя бы один триггер из регистров и блоков 18, 20, 22 и 16 контроля контактирования не изменяет

ской 1 изменяет значение сигнала на выходе элемента И-НЕ 39 (логический О). Значение логического О по шине 29 поступает на вход разреше-,

управле

ния выборки ПЗУ 37 блока 4

ния выборки ПЗУ 37 блока 4

ние выдачи содержимого ПЗУ 37 на его выходы и значения сигналов на выходных щинах ПЗУ 37 соответствуют логи- ческой 1. Сигнал логической 1 по щине 10 поступает на второй вход элемента ИЛИ-НЕ 40 блока 11 пуска, на выходе которого формируется сигнал логического О, Сигнал логического О с выхода элемента ИЛИ-НЕ 40, поступая на первый установочный вход триггера 41 блока 11, устанавливает его прямой выход в состояние логического О, который, поступая на вход

генератора 35 импульсов тактовой частоты блока 4 управления, запрещает формирование импульсов тактовой частоты. На элементы индикации с регистов и блоков 16, 18, 20 и 22 контроля контактирования выводится информация

0причине останова.

Если сигнал на выходе элемента И-НЕ 38 коммутатора 27 равен логичес- кому О (если есть надежное электрическое соединение выводов микросхемы

1и контактов блока 13 переходных контактов), то сигнал логической 1, поступающий на второй вход элемента

7

И-НЕ 39 коммутатора 27 по шине 28, не изменяет значения сигнала на его выходе (т.е. на шине 29 остается сигнал логической 1), следовательно, блок 4 управления продолжает функцио- 5 нирование по проведению контрольного теста. Момент поступления логической 1 по шине 28 с выхода ПЗУ 37 блока 4 управления обуславливается периодом проверки надежности контактирования.

В блоке 7 сравнения значения уставок, поступающих с регистра 6 эталонных реакций по шинам 8, сравниваются с действительными значениями выходных сигналов проверяемой микросхемы 1 (на блок-схеме, представленной на фиг.1 контакты первой и второй группы блока 13 переходных контактов соединены, так как можно считать, что функции

реакц1П1, блок сравнения, триггер пус

10

ка, три согласующих резистора, комму татор и элемент ИЛИ-НЕ, причем инвер сный S-вход триггера пуска подключе к входу пуска устройства, выход триг гера пуска соединен с входом пуска блока управления, первый и второй ин формационные выходы которого соедине с информационными входами соответственно регистра воздействий и регис тра эталонных реакций, выходы регист ра эталонных реакций соединены с пер вой группой информационных входов бл ка сравнения, выход которого являетс выходом годности устройства, инверсный R-вход триггера пуска соединен с выходом элемента ИЛИ-ИЕ, синхровход и D-вход триггера пуска через первый согласующий резистор подключены к вх

первых (задающих) контактов выполняют ду устройства для подключения к вывход ГЫе цепи проверяемой микросхемы 1, а функции вторых (контролирующих) контактов выполняют объединенные контакты первой и второй групп блока 13 переходных контактов), поступакмцих по шине 25 на вторые входы блока 7. Результат сравнения поступает по щине 9 на элементы индикации и на второй вхо ПЗУ 37 блока 4 в виде сигнала Годен или Брак.

Приход сигнала с выхода блока 7 сравнения определяет работу алгоритма функционирования блока 4 управления, хранящегося в ПЗУ 37 в виде программы тестирования микросхемы 1.

В случае соответствия проверяемой микросхемы 1 требованиям, заложенным в тесте, сигнал Годен выставляется на выходе блока 7 сравнения, а блок управления 4 остается в состоянии, соответствующем последнему управляющему воздействию.

Таким образом, предлагаемое устройство позволяет производить проверку качества электрического контакта меж ду выводами проверяемой микросхемы и блоком переходных контактов непосредственно в процессе проведения теста, что позволяет существенно повысить быстродействие контроля в целом. Построение устройства на микросхемах (ТТЛ логики) позволяет повысить надежность.

Формула изобретения

1. Устройство для контроля микросхем, содержащее регистр воздействий, блок управления, регистр эталонных

8

блок сравнения, триггер пус5

0

ка, три согласующих резистора, коммутатор и элемент ИЛИ-НЕ, причем инверсный S-вход триггера пуска подключен к входу пуска устройства, выход триггера пуска соединен с входом пуска блока управления, первый и второй информационные выходы которого соединены с информационными входами соответственно регистра воздействий и регистра эталонных реакций, выходы регистра эталонных реакций соединены с первой группой информационных входов блока сравнения, выход которого является выходом годности устройства, инверсный R-вход триггера пуска соединен с выходом элемента ИЛИ-ИЕ, синхровход и D-вход триггера пуска через первый согласующий резистор подключены к вхо ду устройства для подключения к вы

ходней шине источника питания, отличающееся тем, что, с целью повьшзения быстродействия, устройство содержит первый и второй регистры контроля контактирования, первый и второй блоки контроля контактирования, причем вход начальной установки устройства подключен к установочным входам регистра воздействий, блока управления, первого и второго блоков контроля контакт1фования, к первому входу элемента ИЛИ-НЕ и к первым установочным входам первого и втогюго регистров контроля контактирования, выход синхронизации блока управления соединен с синхровходами регистров

40

45

воздействий и эталонных реакций, выход блока сравнения соединен с информационным входом блока управления, разрешающий вход которого соединен с выходом коммутатора, второй вход элемента ИЛИ-НЕ соединен с выходом останова блока управления, разрешающий выход которого соединен с управляющим входом коммутатора, выходы первого и второго регистров контроля контактирования и первого и второго блоков контроля контактирования соединен4.1 с группой информационных входов коммутатора и образуют информационный выход устройства, группа выходов регистра воздействий подключена к группе выходов устройства для подключения к ГС двунаправленной шине импульсных последовательностей контролируемой микросхемы, синхровходы разрядов первого регистра контроля контактирования подключены к группе входов устройства

50

для подключения к двунаправленной шине и выходной шине импульсных последовательностей контролируемой микросхемы, вторая группа информационных входов блока сравнения подключена к группе входов устройства для подключения к выходной шине импульсных последовательностей контролируемой микросхемы, первые информационные входы первого и второго блоков контроля контактирования подключены к входу устройства для подключения к выходной шине источника питания, информационный вход и синхровход второго регистра контроля контактирования через второй согласующий резистор подключены к входу устройства для подключения к выходной шине источника питания, информационный вход и второй установочной вход первого регистра кон-20 онным входам и синхровходам триггеров

троля контактирования через третий согласующий резистор подключены к входу устройства для подключения к выходной шине источника питания, второй информационный вход первого блока контроля контактирования подключен к входу устройства для подключения к выходной шине уровня питающего напряжения контролируемой микросхемы, второй информационньй вход второго блока Контроля контактирования подключен к входу устройства для подключения к выходной шине единичного потенциала контролируемой микросхемы, второй установочный вход второго регистра контроля контактирования подключен к входу устройства для подключения к выходной шине нулевого потенциала контролируемой микросхемы.

2, Устройство по п. 1, о т л и ч а-40 мационный вход второго блока контроля

ю щ е е с я тем, что блок управления содержит счетчик, генератор импульсов, инвертор и элемент памяти, выходы первого и второго информационных полей, поля останова и поля разрешения которого являются соответствующими выходами блока управления, вход сброса счетчика является уста- новрчным входом блока управления, вход пуска генератора импульсов является входом пуска блока управления, выход генератора импульсов соединен со счетным входом счетчика и через инвертор подключен к выходу синхронизации блока управления, выход счетчика ,и информационный вход блока управления образуют вход адреса элемента памяти, вход разрешения выбора элемента памяти является разрешающим входом блока управления.

3. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что первый блок контроля контактирования содержит группу компараторов, группу инверторов, согласующий резистор и группу триггеров, причем первые входы компараторов группы образуют второй информационный вход первого блока контроля контактирования, первый информационный вход которого подключен к вторым входам компараторов группы и через согласующий резистор к информацигруппы, выходы компараторов группы через соответствующие инверторы соединены с инверсными S-входами соответствующих триггеров группы, уста- новочный вход первого блока контроля контактирования подключен к инверсным R-входам триггеров группы, выходы которых образуют выход первого блока контроля контактирования.

5

4. Устройство по П.1, отличающееся тем, что второй блок контроля контактирования содержит группу компараторов, группу инверторов, согласующий резистор и группу триггеров, причем первые входы компараторов группы образуют второй информационный вход второго блока контроля контактирования, первый инфорконтактирования через согласующий резистор подключен к вторым входам компараторов группы и к информационным входам и синхровходам триггеров группы, выходы компараторов группы через соответствующие инверторы соединены с инверсными S-входамн соответствующих триггеров группы, установочный вход второго блока контроля контактирования подключен к инверсным R- входам триггеров группы, выходы которых образуют выход второго блока контроля контактирования.

25|

33

I

12

30

J5

Фиг 2

J

ч / f

37

:2B

Фиъ.Ч

Фи2.5

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И СВЯЗИ | 2008 |

|

RU2400805C2 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля электрического монтажа | 1988 |

|

SU1520550A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля параметров цифровых интегральных микросхем. Цель изобретения - повьппение быстродействия контроля. Это достигается за счет проверки качества (Л Фие1

ПР

пну

Unum.

20

Редактор Е.Папп

Составитель Д.Ванюхин Техред И.Попович

Заказ 2866/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Unum

Фие.д

Корректор Г.Решетник

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 754423, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-12-03—Подача