(54) ПРЕОБРАЗОВАТЕЛЬ КОД-ВЕРОЯТНОСТЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-вероятность | 1973 |

|

SU450153A1 |

| Преобразователь код-вероятность | 1983 |

|

SU1233172A1 |

| Устройство для преобразования двоичного кода в вероятностно-импульсную последовательность | 1978 |

|

SU734666A1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2096918C1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1005045A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Генератор случайных чисел | 1980 |

|

SU935952A1 |

| Многоканальный генератор псевдослучайных чисел | 1978 |

|

SU739603A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU924706A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

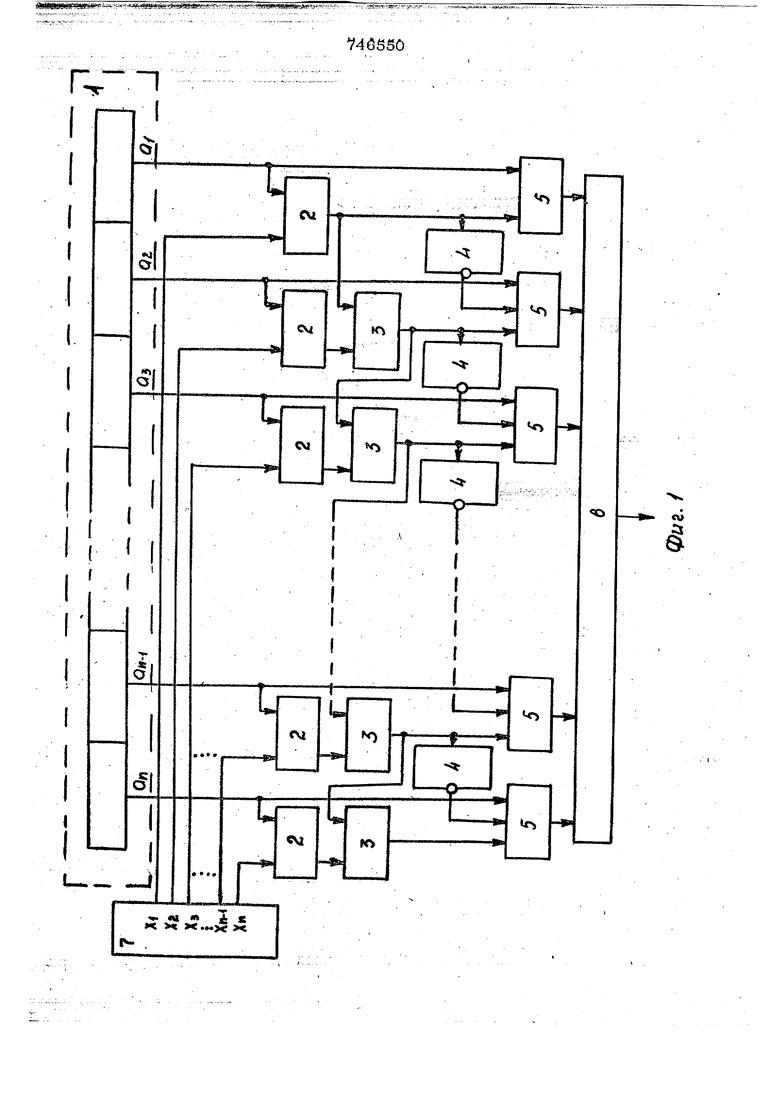

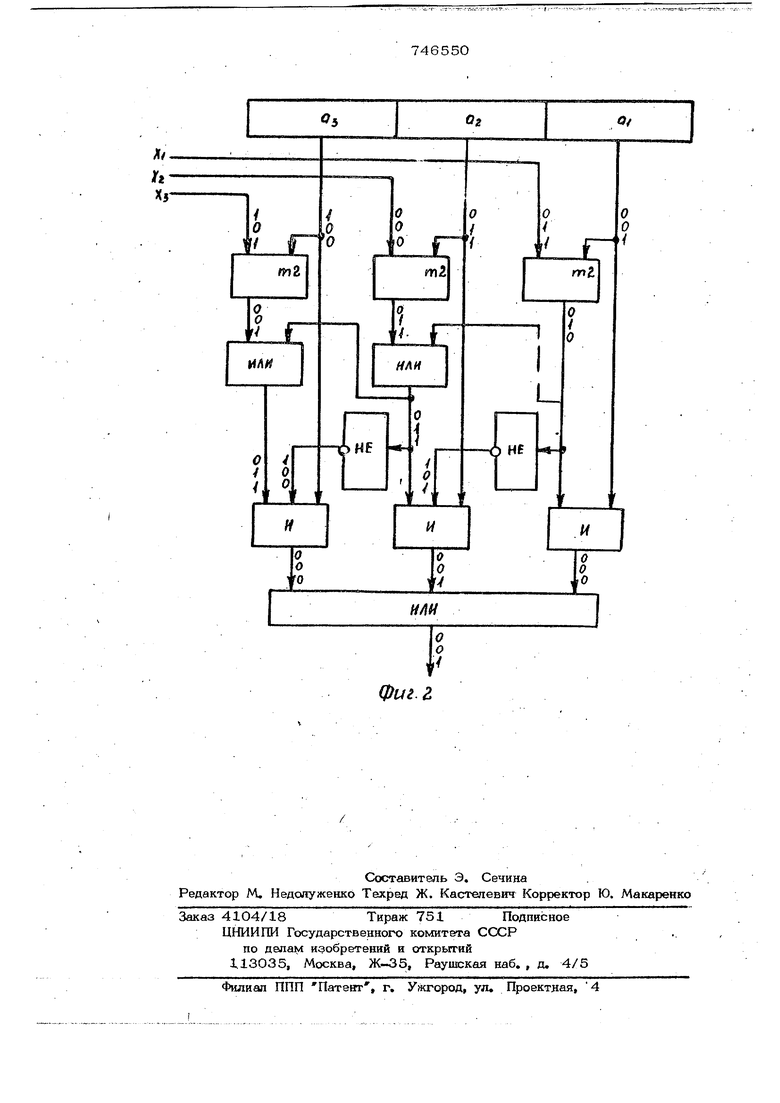

Изобретение относится к вычислитель ной гахнике и может быть использовано совместно с генератором рандомизи - рованных псевдослучайных чисел, либо с любым другим генератором, вырабатывающим случайную последовательность двоичных символов в качестве преобразователя кодг-вероятность для стохастических вьгаислительных машин, у которых случайное появление импульсов возможно лишь в строго фиксированные моменты времени (такты), а также в качестве устройства для сравнения двоичных чисал Известен вероятностный преобразователь с последовательным пострЬением устройства преобразования, содержащий П -разрядный регистр преобразуемого числа, распределитель И1 шульсов, последовательную схему и логическую схему, Последовательная схема содержит комбинационные элементы и элементы памятиW Недостатком устройства является его низкое быстродействие вследствие TCffO, что результат преобразования вьадается за п -тактов. Известно также устройство для сравнения чисел, содержащее дешифратор, входы которого подключены к шинам младШИ.Х разрядов первого двоичного числа, схема ИЛИ, и инверторы J Недостатками устройства явл$потся его узкое функциональное назначение, TaiK как сравниваемые числа находится в единичном позиционном и единичном нормальном кодах, а также сложность устройства, так как для преобразования двоичного кода в единичный необходимы дешифраторы. Наиболее близким по технической сущности к предложенному является вероятностный преобразователь с параллельным выполнением устройства преобразования, Известный веройтностный преобразователь содержит Л -разрядный регистр преобразуемого числа, (п-1) схему ИЛИ, (3 п -2) схемь И, причем на входы И подключены прямой и инверсный выходы регистра преобразуемого числа и значение разряда псевдослучайного числа и его инверсии. Выходы ссхэтгветствую щих схем И подключены к входам схем ИЛИ. Преобразователь предназначен для сравнения в каждом такте случайного двоичного числа i , j,, ...X-p}i вьфабатьшаемого генератором сл чайньгх чи сел, с кодом детерминированного числа (, oi;j, ,... . случае, если X Л выходе появляется символ , в про тивном случае - символ 0 З. Недостатками известного устройства являются сравнительно малое быстродействие и относительная сложность. Целью изобретения является повышение быстродействия, а также упрощение устройства. Цель достигается тем, что в преобра зователь код - вероятность, содержащий генератор псевдослучайных чисел, (п-1 элементов ИЛИ, п -разрядный регистр преобразуемого числа, вькоды которого соединены соответственно с первыми вхо дами о элементов И, введены (п-1) элементов НЕ, о сумматоров по модулю два и о -входовой элемент ИЛИ, входы которого соединены соответственно с выходами п элементов И, первые аходы сумматоров по модулю два соединены соответственно с выходами п -разрядного регистра преобразуемого числа, вторые входы сумматоров но модулю два подключены соответственно к выхойам Генерато ра псёвдослучайнья чисел, выход ( -го ( i -2 - п ) сукшатора по модулю два подключен к первому аходу J- -го ( 1-( 1П-2)) элемента ИЛИ, выкод которого подключен к второму ахо ду ( -1-1)-го элемента ИЛИ, к входу (К4-1)-ого (к 1-(п-1) элемента НЕ и к второму входу ( I +1)-ого элемента И, третий вход которого соединей с вь ходом i -ого элемента НЕ, выход парь вого сумматора по модулю два подключен к второму входу первого элемента ИЛИ; к второму входу первого элемента И, входу t -ого элемента НЕ, выход h -входового элемента ИЛИ является выходом преобразователя На фиг. 1 приведена структурная схема предлагаемого преобразователя; на фиг. 2 - функциональная схема ripifeобразователя код-вероятность для Y 3 Преобразователь код-вероятность со стоит из п -разрядного регистра Ij преобразуемого чнсяа, п- сумматс х 2 по модулю два, (h-l) элементов 3 ИЛИ( п -1) элементов 4 НЕ , п эле- ментов 5 И, одного П -аходового элемента 6 ИЛИ, генератора псевдослучайных чисел. Регистр 1 представляет собой стандартный п -разрядный регистр двоичного числа, предназначенный для хранения кода преобразуемого числа. Значение -го разряда регистра совместно с -ым разрядом псевдослучайного числа подано на 1 -ый сумматор 2 по модулю два, выполняющий операцию сложения по модулю два. Выход ( -ого сумматора по модулю два подключен к аходу ( -1) элемента 3 ИЛИ, на другой вход которого подан сигнал с ( -2) элемента ИЛИ, j -ый элемент ИЛИ выполняет операцию логического сложения. К входам ( -ого элемента 5 И, выпопшпоще- го операцию логического умножения, подключены выходы ( -Г)-го элемента ИЛИ, выход (к-1)-го элемента 4 НЕ, который осуществляет инверсию выходного сигнала ( i -2)-го элемента ИЛИ, а также на один из входов i -ого элемента И поступает значение i -го разряда кода преобразуемого числа из регистра 1. К | -ому входу п -аходового элемента 6 ИЛИ, формирующего выходной сигнал преобразователя, подключен выход i- -ого элемента И.. Преобразователь работает следующим образом. В начальный момент на аходы сумматоров 2 по модулю два поступают значения разрядов кода преобразуемого числа А а,,cii,ji,.., О(п} и значения разрядов псевдослучайного числа с генератора 7x{X,., SaTSM код, сформированный на вькодах сумматоров по модулю два, сравнивается на элементах 3 ИЛИ, с кодом, полученным на выходах предыдущих элемейТов ИЛИ, выходной сигнал с элементов 3 ИЛИ инвертируется и совместно с неинвертируемым выходным сигналом последующего элемента ИЛИ и значениями разрядов кода преобразуемого числа А поступает на элемент 5 И, сигнал с выходов элементов И поступает на многовходовой элемент 6 ИЛИ, на выходе которого формируется сигнал р , являющийся выходным сигналом преобразователя, причем сигнал Р принимает значение 1 при выполнении условия А Л , и значение О при условии А)ч . При конкретной реализации преобразователя во избежание эффекта гонок целесообразно выходную последовательность случайных импульсов стробировать. Преимущества предлагаемого преобразователя код-вероятность заключаются в повышении быстродействия устройства. При реализации вероятностного преобразователя совместно с генератором рандомизированных псевдослучайных ЧйСед: устройство отличается простотой технической реализации и минимальными затра тами оборудования. Использование предлагаемого устройства возможно не «тол ко как преобразователя код-вероятность, а и как устройства для сравнения двоичных чисел. Реализация устройства на ссюременной элементной базе позволит достигнуть высоких технико-экономических показателей. Формула изобретения Преобразов-атель код-вероятность, содержащий генератор псевдослучайных чисел, (п -1) элементов ИЛИ, п -разряд ный регистр преобразуемого числа, вььходы которого соединены соответственно с первыкш входами п элементов И, отличающийся тем, что, с целью увеличения быстродействи, он содержит (n-l) элементе НЕ, п сумматоров по модулю два и п -аходовой элемент ИЛИ, входы которого соединены соответственно с выходами п элемен-, тов И, первые входы сумматоров по модулю два соединены соответственно с выходами п -разрядного регистра преобразуемого числа, вторые входы сумматоров по модулю два подключень соответст венно к выходам генератора псевдослучайных чисел, выход i -го (i -2-п) сумматора по модулю два подключен к первому входу -го ((o -2)) элемента ИЛИ, выход которого подкгаочен к втфому входу ( j +1)-го элемента ИЛИ, к нходу (к +1)-го ((п-1) элемента НЕ и к второму входу (i +1)-го элемента И, третий вход которого соединен с выходом jf- -ого элемента НЕ, ВЬРход первого сумматора по модулю два подключен к второму входу первого элемента ИЛИ, к Ьторому входу первого элемента И, ьходу п -ого элемента НЕ, выход П -входового элемента ИЛИ является выходом преобразователя. Источники информации, принятые во внимание при экспертизе 1.Яковлев В. В. и Федоров Р. Ф. Стохастические вычислительные машинь}, Машиностроение, 1974, с. 84. 2.Авторское свидетельство СССР 443383, кл. q Об F 7/02, БИ № 34, 1974. , 3.Яковлев В. Ф. , Федоров Р. Ф. Стохастические вычислительные машины, Машиностроение, 1974, с. 8-1 (прототип).

V46S50

фиг. г

Авторы

Даты

1980-07-05—Публикация

1978-05-03—Подача