I

Изобретение относится к вычислительной технике и может быть применено в цифровых системах управления для построения вероятностных вычислительных устройств, оперирующих с псевдослучайными последовательностями импульсов.

Известно устройство для преобразования двоичного кода в псевдослучайные последовательности, содержащее схему сравнения, генератор импульсов, регистр ис}фдного числа, логический блок и элемент ИЛИ 1.

Недостатком этого устройства является низкое быстродействие, связанное с необходимостью проведения большого числа статистических испытаний.

Наиболее близким по технической сущности к предложенному является преобразователь двоичного кода в вероятностно-импульсную последовательность, содержащий сдвиговый регистр с обратной связью, регистр преобразуемого кода, группу элементов И, элемент ИЛИ, входы которого соединены с выходами элементов И группы, первые входы которых соединены с группой выходов регистра преобразуемого кода. Кроме того, это устройство содержит многовходовый логический блок, входы которого соединены с выходами сдвигового регистра с обратной связью, а выходы - с входами группы элементов И 2.

Недостатком известного устройства яв, ляется его сложность, связанная- с наличием логического-блока, быстрый рост количества аппаратуры при увеличении числа разрядов преобразуемого кода, большое число связей между сдвиговым регистром с обратной связью и логическим блоком, слож10 ность перестройки устройства и относительно невысокое быстродействие.

Цель изобретения - упрощение устройства и повышение регулярности его структуры

Указанная цель достигается тем, что в

15 устройстве вместо многовходового логического блока используется управляемый сдвиговый регистр управляющий вход которого соединен с выходом сдвигового регистра с обратной связью, вход записи первого разряда управляемого сдвигового регистра сое20динен с источником сигнала логической единицы, информационный вход и входы записи остальных разрядов управляемого сдвигового регистра соединены с источником сигнала логического нуля, а выходы управляемого сдвигового регистра соединены со вторыми входами группы элементов И.

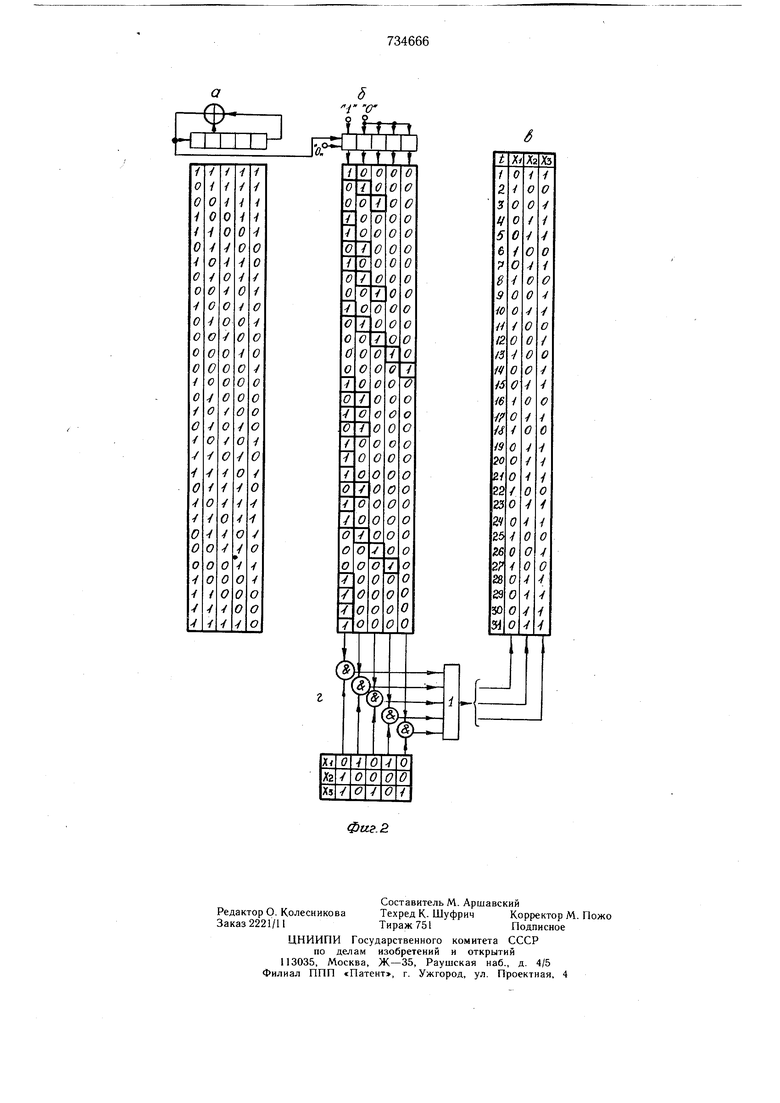

На фиг. 1 представлена блок-схема устройства.

Схема устройства содержит сдвиговый регистр 1 с обратной связью, управляемый регистр 2 сдвига, группа 3 элементов И, регистр 4 преобразуемого кода, элемент 5 ИЛИ.

Двоичный код преобразуемой величины записывается в регистр 4 (.старше разряды на фиг. 1, 2 в левой части регистра), в котором хранится до окончания полного цикла преобразования. Последовательность .максимальной длины (М-последовательность), формируемая на выходе сумматора (или сумматоров) по модулю 2 в цепи обратной связи регистра 1, потактно поступает на вход этого регистра и на управляющий вход управляемого регистра 2 сдвига. Управляемый регистр 2 сдвига работает следующим образом.

в начальный момент времени в него записывается код 1000...О, если в процессе работы на его управляющем входе появляется сигнал, соответствующий уровню логического нуля, то регистр работает в режиме сдвига, продвигая потактно «1 вправо (при этом левая часть регистра, заполняется «О), если же на управляющем входе появляется сигнал, соответствующий уровню логической единицы, то регистр 2 работает в режиме записи параллельного кода (в данном случае кода 1000.0). На выходе первого разряда регистра 2 формируется псевдослучайная последовательность с вероятностью появления «1 р(1)-2- (М-последовательность). На выходе каждого последующего разряда вероятность появления «1 уменьщается вдвое по сравнению с вероятностью появления «1 на выходе предыдущего разряда. В произвольный момент времени «1 может появиться только на одном из разрядных выходов регистра 2. Таким образом, последовательности, формируемые на разрядных выходах этого регистра, ортогональны, что определяет несовместность потоков, формируемых на выходах вентилей 3, подключенных ко входам логического элемента 5 ИЛИ. Выход элемента 5 является выходом устройства. Управляющий входь регистра 2 может быть подключен к любому разрядному выходу регистра 1 с обратной связью, так как последовательности максимальной длины (М-последовательности), формируемые на этих выходах, отличаются друг от друга только сдвигом фаз.

Пример, пусть разрядность устройства п 5. На фиг. 2а приведены состояния сдвигового регистра с обратной связью (характеристический многочлен .f(x) ) на всем цикле преобразования (начальное

состояние 11111). На фиг. 26 приведены состояния управляемого регистра сдвига (програм мная матрица состояний). Начальное ссгстояние регистра 10000. В первой графе на фиг. 2е указано дискретное время в тактах. Так как работа всего устройства происходит потактно, то эта графа относится к а, б, в (на фиг. 2а, б графи для простоты не показаны). В остальных графах на фиг. 2в приведены выходные последовательности преобразователя для трех произвольных величин X i, X , X , пятиразрядные коды которых приведены в строках на фиг. 2г (старщие разряды кодов слева). Сумма импульсов («единицы) в выходной последовательности численно равна соответствующей преобразуемой величине А: 1, х i, х ,. Программные матрицы на выходе блоков 2 в известном и предлагаемом устройстве полностью совпадают.

По сравнению с известным устройством рост количества оборудования, необходимого для реализации управляемого регистра (заменивщего логический блок), с увеличением разрядности происходит строго линейно. Ниже приведены оценки затрат оборудования, необходимого для реализации блоков 2 предлагаемого и известного устройств для трех значений разрядности п i 8, П)12, . Затраты оборудования определены методом доведения функциональных схем блоков 2 до принципиальных с использованием микросхем расширенной 133 серии, и составляют:

П4 8 пг 12 Спр 3

Спр 4 , гдеСпр - затраты оборудования на блок 2 предлагаемого устройства в корпусах микросхем 133ИР1; Сиз-затраты оборудования на блок 2 известного устройства в корпусах микросхем 133ЛА1 - 133ЛА4, 133ЛИ1, 133ЛН1.

Число связей между блоками 1 и 2 в предлагаемом устройстве доведено до одной (вместо 2п-1 в известном). Это имеет особое значение, если принять во внимание, что блок 1 (генератор псевдослучайных чисел) обычно в приборах общий, а блоков, формирующих последовательности кратных ортогональных частот, может быть несколько в зависимости от количества преобразуемых величин. При этом, если необходимо, чтобы результирующие вероятностно-импульсные последовательности были некоррелированы, в предлагаемом устройстве достаточно обеспечить нужный сдвиг М последовательностей, поступающих на управляющие входы регистров 2, друг относительно друга. В известном устройстве это осуществляется сложнее, так как возникает необходимость анализа всех (2п-1) к связей между блоком i и логическими блоками 2 (к - число преобразуемых величин).

Предлагаемое устройство имеет более высокое быстродействие по сравнению с известным. Время формирования сигнала на выходе блока 2 (в одном такте) в предлагаемом устройстве (Тпр) определяется выражением.

хгде te- время, необходимое для сдвига регистра 2 на один разряд; tj - время, необходимое для записи в

регистр 2 кода 1000...0. Время формирования сигнала на выходе блока 2 в известном устройстве:

TU Тс 4- -ГА..

где tb - время, необходимое для сдвига регистра 1 на один разряд вправо; ТА.Л- задержка распространения сигнала в логическом блоке 2. Таким образом, Тпр Тиа.

Схемная простота, высокая регулярность структуры, высокое быстродействие дают возможность создания специальной микросхемы, подобной микросхеме 133ИЕ8 (но с иными функциональньпйи возможностями), в одной или нескольких сериях интегральных микросхем.

Формула изобретения

Устройство для преобразования двоичного кода в вероятностно-импульсную последовательность, содержащее сдвиговый регистр с обратной связью, регистр преобразуемого кода, группу элементов И, элемент ИЛИ, входы которого соединены с выходами группы элементов И, первые входы которых соединены с группой выходов регистра преобразуемого кода, отличающееся тем, что, с целью упрощения устройства, оно содержит управляемый сдвиговый регистр, управляющий вход которого соединен с выходом сдвигового регистра с обратной связью, вход записи первого разряда управляемого сдвигового регистра соединен с источником сигнала логической единицы, информационный вход и входы записи остальных разрядов управляемого сдвигового регистра соединены с источником сигнала логического нуля, а выходы управляемого сдвигового регистра соединены со вторыми входами элементов И группы.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 401993, кл. G 06 F 5/02, 1973.

2. Ерухимович В. М., Шпильберг А. Я. Способ получения псевдослучайных последовательностей с заданной средней частотой появления импульсов. Сб. «Приборы и системы автоматики 1970. вып. 14 изд. ХГУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Псевдостохастический интегратор | 1981 |

|

SU962938A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК | 2009 |

|

RU2395834C1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Стохастическое устройство для вычисления характеристик графов | 1981 |

|

SU1010628A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1332384A2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК И СОЧЕТАНИЙ | 2010 |

|

RU2427885C1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU951301A1 |

Вход Фиг.1

Авторы

Даты

1980-05-15—Публикация

1978-01-23—Подача