Изобретение относится к области криптографических преобразований и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации.

Известен способ шифрования, предназначенный для криптографической защиты информации в вычислительных системах и заключающийся в многократном прибавлении ключа к преобразуемой информации с последующим применением подстановочных и перестановочных преобразований. С использованием этого способа построена система Lucifer фирмы IBM и стандарт шифрования данных национального бюро стандартов США.

В известном стандарте шифрования данных к содержимому двух 32-разрядных ячеек 64-разрядного информационного регистра 16 раз прибавляют по модулю 2 содержимое 64-разрядного ключевого регистра с последующим воздействием на 32-разрядную сумму 32-разрядным функциональным преобразованием f.

Известный стандарт шифрования данных шифрует информацию блоками по 64 бита, а это при зашифровании требует предварительного накапливания 64 бит информации, а при расшифровании требует дополнительной синхронизации для выделения начала очередного блока зашифрованной информации. Кроме того, процесс зашифрования очередного блока состоит из 16 циклов, что вносит определенную задержку при зашифровании очередных блоков информации. Перечисленные особенности известного стандарта шифрования данных делают его неудобным при использовании в системах радиосвязи.

Целью настоящего изобретения является обеспечение побитного шифрования информации с использованием ключа необходимого пользователю размера.

Поставленная цель достигается тем, что в способе шифрования двоичной информации, заключающемся в зависящем от 64-разрядного ключа преобразовании 64-разрядного блока шифруемой информации путем 16-кратного выполнения набора операций, включающего сложение 32-разрядных чисел из информационного и ключевого регистра и функциональное преобразование полученной 32-разрядной суммы, на передаче содержимое M-разрядного регистра сдвига преобразуют блоком функционального преобразования данных fд и первым датчиком М-разрядных псевдослучайных чисел, результат преобразования складывают (при M N, например, по модулю 2 или 2N) с N-разрядным содержимым ключевого регистра блока формирования n-разрядного ключа, сумму преобразуют блоком N-разрядного функционального преобразования суммы fc, в полученном N-разрядном результате преобразования мажоритарным элементом определяют преобладание нулей или единиц и в зависимости от результата прибавляют по модулю 2 к двоичному знаку шифруемой информации соответственно 0 или 1, полученный в результате зашифрованный двоичный знак направляют в канал связи и на вход M-разрядного регистра сдвига, а на приеме выполняют те же действия, что и на передаче, за исключением того, что на выход M-разрядного регистра сдвига направляют пришедший из канала связи зашифрованный двоичный знак, к которому одновременно прибавляют по модулю 2 выработанный мажоритарным элементом двоичный знак и получают знак открытой информации. Чтобы мажоритарный элемент однозначно реагировал на поступающее на его вход число, разрядность числа N выбирается нечетной.

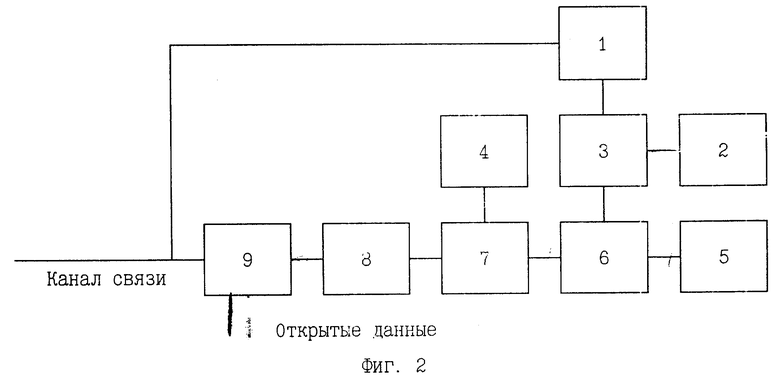

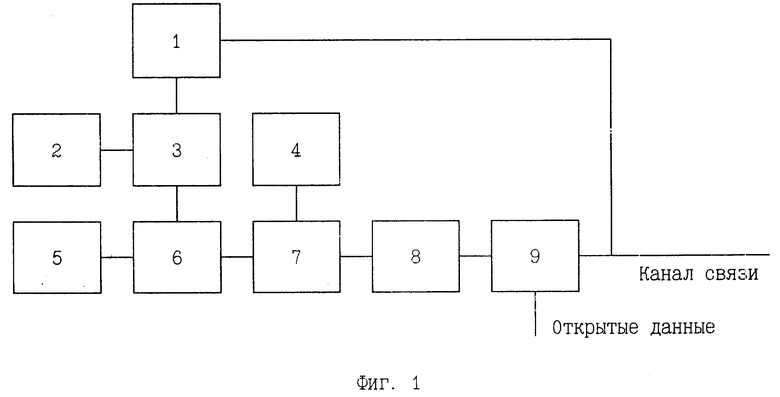

На фиг. 1 и 2 представлены соответственно блок-схемы устройств зашифрования и расшифрования для осуществления способа шифрования двоичной информации. Устройства зашифрования и расшифрования содержат: M-разрядный регистр сдвига 1, первый датчик M-разрядных псевдослучайных чисел 2, блок N-разрядного функционального преобразования данных 3, второй датчик N-разрядных псевдослучайных чисел 4, блок формирования N-разрядного ключа 5, N-разрядный сумматор 6, блок N-разрядного функционального преобразования суммы 7, мажоритарный элемент 8 и одноразрядный сумматор 9.

Процесс зашифрования бита открытой информации осуществляют следующим образом. M-разрядное содержимое M-разрядного регистра сдвига 1 преобразуют блоком N-разрядного функционального преобразования данных 3 и складывают (например, по модулю 2 и 2N) в N-разрядном сумматоре 6 с N -разрядным содержимым ключевого регистра блока формирования N-разрядного ключа 5, полученную сумму преобразуют блоком N-разрядного функционального преобразования суммы 7, мажоритарным элементом 8 определяют количество единиц в N-разрядном результате преобразования. Если единиц больше, чем нулей, то в одноразрядном сумматоре 9 к двоичному знаку открытой информации прибавляют 1, в противном случае 0. Полученный в результате суммирования двоичный знак зашифрованной информации направляют в канал связи и на вход M-разрядного регистра сдвига 1, содержимое которого предварительно сдвигают на один разряд в сторону младших разрядов с потерей выдвинутого самого младшего разряда.

N-разрядное функциональное преобразование информации выполняют, например, путем суммирования по модулю 2 или 2n N-разрядных чисел с N-разрядными двоичными псевдослучайными числами соответствующих датчиков 2 или 4. При этом разрядность регистра сдвига 1 M и разрядность псевдослучайных чисел первого датчика 2 M выбирается равной значению N.

Процесс расшифрования бита зашифрованной информации осуществляют следующим образом. М-разрядное содержимое М-разрядного регистра сдвига 1 преобразуют блоком N-разрядного функционального преобразования данных 3 и складывают (например, по модулю 2 или 2N) в N-разрядном сумматоре 6 с N-разрядным содержимым блока формирования N-разрядного ключа 5, полученную сумму преобразуют блоком N-разрядного функционального преобразования суммы 7, мажоритарным элементом 8 определяют количество единиц в N-разрядном результате преобразования. Если единиц больше чем нулей, то в одноразрядном сумматоре 9 к пришедшему из канала связи знаку зашифрованной информации прибавляют 1, в противном случае 0. В результате суммирования получают двоичный знак открытой информации. Пришедший из канала связи зашифрованной информации одновременно направляют на вход M-разрядного регистра 1, содержимое которого предварительно сдвигают на один разряд в сторону младших разрядов с потерей выдвинутого самого младшего разряда.

Как в устройстве зашифрования, так и в устройстве расшифрования N-разрядное функциональное преобразование данных выполняют с использованием M-разрядных двоичных псевдослучайных чисел первого датчика псевдослучайных чисел 2 (M≥N), а N -разрядное функциональное преобразование суммы выполняют с использованием N-разрядных двоичных псевдослучайных чисел второго датчика псевдослучайных чисел 4.

Если 0(i) i-й двоичный знак открытой информации, III(i) i-й двоичный знак зашифрованной информации, то III(i) 0(i)  G(i) на передаче и 0(i) III(i)

G(i) на передаче и 0(i) III(i)  G(i) на приеме, где

G(i) на приеме, где  знак операции суммирования по модулю 2.

знак операции суммирования по модулю 2.

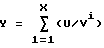

Обозначив содержимое M-разрядного регистра сдвига 1 в i-й момент времени R(i) r1(i), r2(i), rm(i), ri(i) 0,1, а M-разрядное псевдослучайное число первого датчика S1(i) (s11(i), s12(i), s1m(i)), S1j(i) 0, 1, 1≅j≅M, i≥1 в результате первого преобразования получаем N-разрядное число R1(i) (r11(i), r12(i), r1n(i)) fд(R(i), S1(i)), где r1j(i) rj(i)  s1j(i) для случая M N и преобразования данных в форме, например, суммирования по модулю 2, что при хороших статистических характеристиках последовательностей псевдослучайных чисел позволяет значительно улучшить статистические характеристики зашифрованной информации.

s1j(i) для случая M N и преобразования данных в форме, например, суммирования по модулю 2, что при хороших статистических характеристиках последовательностей псевдослучайных чисел позволяет значительно улучшить статистические характеристики зашифрованной информации.

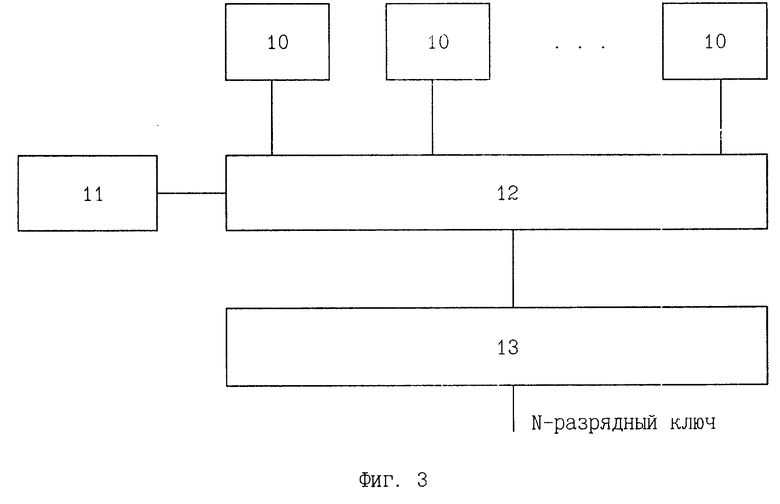

Если содержимое ключевого регистра блока формирования N-разрядного ключа C(i) (c1(i), c2(i), cn(i)), cj(i) 0, 1, 1≅j≅N, то мажоритарный элемент в i-й момент времени выработает двоичный знак G(i) Maj(fc(R1(i)  C(i))), где Maj(a) 0, если число единиц в двоичном представлении числа a <N/2; 1, если число единиц в двоичном представлении числа a > N/2} Изменение содержимого N-разрядного ключевого регистра блока формирования N-разрядного ключа в процессе зашифрования улучшает статистические характеристики зашифрования информации. Достигается это формированием N-разрядного ключа в N-разрядном ключевом регистре блока формирования ключа K-разрядными (где 1≅K≅N) словами, выбираемыми из содержимого B (B-произвольное) D-разрядных (D≥K) регистров рабочих ключей в соответствии с L-разрядным выходным кодом (L Log2(B/K)) P-разрядного регистра (P≥L) управляющего ключа. Принцип действия блока формирования N-разрядного ключа поясняется блок-схемой на фиг. 3. P-разрядный регистр управляющего ключа 11 представляет из себя, например, сумматор с L-разрядным выходным кодом, по которому управляемый вентиль 12 определяет адрес K-разрядного слова (порядковые номера D-разрядного регистра 10 и K-разрядного слова в его D-разрядном (H≥N) содержимом) и включает его в состав N-разрядного ключа содержимого N-разрядного ключевого регистра 13. По окончании процедуры формирования ключа, когда содержимое ключевого регистра полностью обновлено, N-разрядный ключ выдается на N-разрядный сумматор. В i+1-й момент времени в процессе шифрования будет участвовать ключ C(i+1) (c1(i+1), c2(i+1), cn(i+1)), cj(i) 0, 1, 1≅j≅N, i>1. Обновление N-разрядного ключа, кроме того, достигается выполнением регистров управляющего 11 и рабочих ключей 10 в виде регистров сдвига с линейной функцией в обратной связи. Если характеристический многочлен регистра имеет вид

C(i))), где Maj(a) 0, если число единиц в двоичном представлении числа a <N/2; 1, если число единиц в двоичном представлении числа a > N/2} Изменение содержимого N-разрядного ключевого регистра блока формирования N-разрядного ключа в процессе зашифрования улучшает статистические характеристики зашифрования информации. Достигается это формированием N-разрядного ключа в N-разрядном ключевом регистре блока формирования ключа K-разрядными (где 1≅K≅N) словами, выбираемыми из содержимого B (B-произвольное) D-разрядных (D≥K) регистров рабочих ключей в соответствии с L-разрядным выходным кодом (L Log2(B/K)) P-разрядного регистра (P≥L) управляющего ключа. Принцип действия блока формирования N-разрядного ключа поясняется блок-схемой на фиг. 3. P-разрядный регистр управляющего ключа 11 представляет из себя, например, сумматор с L-разрядным выходным кодом, по которому управляемый вентиль 12 определяет адрес K-разрядного слова (порядковые номера D-разрядного регистра 10 и K-разрядного слова в его D-разрядном (H≥N) содержимом) и включает его в состав N-разрядного ключа содержимого N-разрядного ключевого регистра 13. По окончании процедуры формирования ключа, когда содержимое ключевого регистра полностью обновлено, N-разрядный ключ выдается на N-разрядный сумматор. В i+1-й момент времени в процессе шифрования будет участвовать ключ C(i+1) (c1(i+1), c2(i+1), cn(i+1)), cj(i) 0, 1, 1≅j≅N, i>1. Обновление N-разрядного ключа, кроме того, достигается выполнением регистров управляющего 11 и рабочих ключей 10 в виде регистров сдвига с линейной функцией в обратной связи. Если характеристический многочлен регистра имеет вид  то в (i+1)-й момент содержимое обобщенного (P или D)-разрядного регистра сдвига 11 или 10 станет K(i+1) (K1(i+1) K2(i), Kn-1(i+1) Kn(i), Kn(i), Kn(i+1) K1(i)

то в (i+1)-й момент содержимое обобщенного (P или D)-разрядного регистра сдвига 11 или 10 станет K(i+1) (K1(i+1) K2(i), Kn-1(i+1) Kn(i), Kn(i), Kn(i+1) K1(i)  (i)). При этом значительно возрастает эквивалентная длина генерируемой последовательности, что позволяет увеличить криптостойкость зашифрованной информации.

(i)). При этом значительно возрастает эквивалентная длина генерируемой последовательности, что позволяет увеличить криптостойкость зашифрованной информации.

Улучшение статистических характеристик преобразуемой информации и значительная эквивалентная длина последовательности псевдослучайных N-разрядных чисел позволяют выполнить датчики N-разрядных псевдослучайных чисел в виде N-разрядных регистров сдвига с линейной функцией в цепи обратной связи.

Так как зашифрованная информация по сути представляет собой последовательность псевдослучайных чисел практически произвольной длины, то датчик N-разрядных псевдослучайных чисел может быть выполнен на основе предлагаемого устройства в целом по схеме, приведенной на фиг. 4. Он включает описанное устройство шифрования двоичной информации 14 с независимыми параметрами исполнения и шифрования и N-разрядный регистр сдвига 15, являющийся N-разрядным выходом датчика N-разрядных псевдослучайных чисел, при этом одноразрядный вход регистра сдвига подключен к выходу описанного устройства 14, вход которого подключается к выходу мажоритарного элемента 8 или одноразрядного сумматора 9.

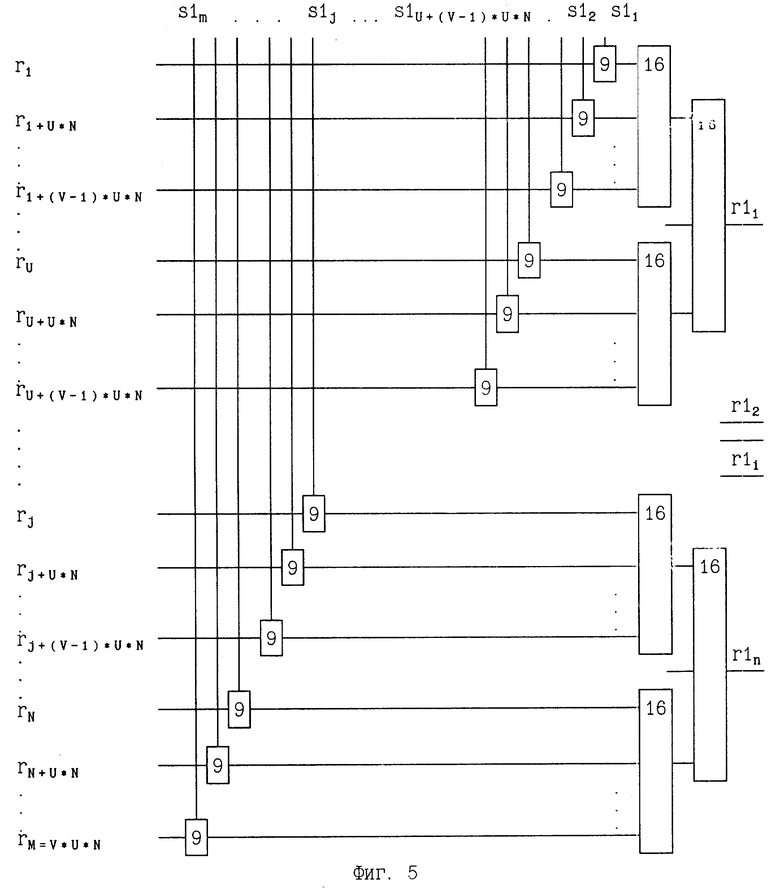

В качестве любого из N-разрядных функциональных преобразований может быть избрано, например, прибавление по модулю 2 к преобразуемому N-разрядному числу R (r1, r2, rN) N-разрядного псевдослучайного числа S (s1, s2, sN) или логическое преобразование указанных чисел, например, F-значная конъюнкция (1≅F≅N) указанных чисел. При N<M N-разрядное функциональное преобразование M-разрядных данных fд может быть выполнено параллельно в N каналах на основе мажоритарного преобразования данных одного из N различных непересекающихся сегментов регистра сдвига 1. Предлагаемый принцип преобразования данных поясняется рисунком на фиг. 5. Каждый из N идентичных каналов преобразования уплотняет данные H двоичных разрядов регистра сдвига 1, причем H M/N и выбирается целым, а совокупность уплотняемых разрядов образует одно из N непересекающихся подмножеств элементов, равномерно расположенных по длине сдвига 1. Каждое из подмножеств, в свою очередь, является объединением U непересекающихся сегментов по V двоичных разрядов регистра 1 (U и V выбираются целыми), равномерно распределенных по его длине, поэтому H U•V, а M V•U•N. Аналогичным образом организуются M двоичных разрядов регистра датчика псевдослучайных чисел 2, в результате чего устанавливается однозначное соответствие разрядов обеих регистров.

Таким образом каждый из N каналов преобразования включает U устройство мажоритарного уплотнения данных V двоичных разрядов регистра сдвига 1 и X-каскадный мажоритарный элемент, образующий иерархическую структуру. При этом для случая V-входовых мажоритарных элементов 16 каскадный мажоритарный элемент включает

мажоритарных элементов, а число каскадов преобразования определяется выражением X LogvU. Данные некоторого V-сегмента разрядов регистра сдвига 1 и соответствующего ему V-сегмента разрядов датчика псевдослучайных чисел 2 поразрядно суммируются соответствующими одноразрядными сумматорами 9. Мажоритарным элементом 16 устройства мажоритарного уплотнения разрядов среди V одноразрядных результатов подсчитывается число 1 или 0 и на выход мажоритарного элемента 16 выдается 1, если среди одноразрядных результатов преобладают 1, и 0 в противном случае. Совокупность выходных данных U устройств мажоритарного уплотнения разрядов поступает на вход каскадного мажоритарного элемента, каждый из элементарных мажоритарных элементов которого на любом из каскадов реализует вышеописанный алгоритм мажоритарного преобразования. При этом число входов каждого из мажоритарных элементов для однозначности преобразования выбирается нечетным. Описанный рекуррентный алгоритм мажоритарного преобразования заканчивается единственным мажоритарным элементом последнего каскада уплотнения разрядов, выходные данные которого являются содержимым соответствующего двоичного разряда результата N-разрядного функционального преобразования данных fд.

Источники информации

1. Д.Сяо, Д.Керр, С.Мэдник. Защита ЭВМ. М. Мир, 1982, с. 137 162.

2. И. М. Тепляков, Б.В.Рощин, А.И.Фомин, В.А.Вейцель. М. Радио и связь, 1982, с. 146 152.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2097931C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2004 |

|

RU2262204C1 |

| СПОСОБ ШИФРОВАНИЯ БЛОКОВ ДАННЫХ | 2001 |

|

RU2207736C2 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2007884C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ "АЛБЕР" | 1991 |

|

RU2024209C1 |

| Способ шифрования информации и устройство для осуществления способа | 2020 |

|

RU2756976C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА - "АЛБЕР" | 1994 |

|

RU2099890C1 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ ДАННЫХ | 2001 |

|

RU2226041C2 |

| СПОСОБ СКРЫТОЙ ПЕРЕДАЧИ ЗАШИФРОВАННОЙ ИНФОРМАЦИИ ПО МНОЖЕСТВУ КАНАЛОВ СВЯЗИ | 2011 |

|

RU2462825C1 |

Изобретение относится к области криптографических преобразований и может быть использовано в связных, вычислительных и информационных системах для криптографического закрытия двоичной информации. Предлагаемое устройство выгодно отличается от известных шифрующих устройств (например, системы Lucifer фирмы IBM и стандарта шифрования данных национального бюро стандартов США) возможностью побитного шифрования двоичной информации с использованием ключа необходимой пользователю длины. Это делает его удобным при использовании в системах радиосвязи. 2 с. и 2 з.п. ф-лы, 5 ил.

| Сяо Д., Керр Д., Мэдник С | |||

| Защита ЭВМ | |||

| - М.: Мир, 1982, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

Авторы

Даты

1997-11-20—Публикация

1995-07-07—Подача