(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1569825A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

I

Изобретение относится к области вычислительной техники и может быть использовано автономно, либо в составе универсальных или специализированных цифровых машин.

Известны устройства для деления чисел l, 2 , содержащие сумматор, регистры делимого и делителя, устройство управления. Известные устройства обеспечивают нахождение частного, делимого и делителя путем представления вычислительного процесса в виде последовательности шагов.

Из известных устройств наиболее близким по своей технической сущности к изобретению является устройство, описанное в з , включающее три параллельных сумматора на И разрядов, первый из которых дополнен младшими разрядами в количестве П , блок формирования знака, вход делитвпя, вход делимого З . Устройство выполняет операцию деления путем последовательной реализации алгоритма определения частного,

ЧТО и определяет его относительно невысокое быстродействие.

Целью настоящего изобретения является увеличение быстродействия устройства для деления двоичных Чисел.

Указанная цель достигается тем, что устройство для деления двоичных чисел содержит три параллельных (М +2) разрядных сумматора и блок формирования знака частного, входы которого подсоеди10нены к шине знака делимого и шине знака делителя, (И -3) паратшельных (П+2)-х разрядных сумматоров, ()1-1) управляемьй и один неуправляемый (п+1)-разрядные преобразователи прямого кода в дополни15тельный, причем выход каждого т -го разряда j-го сумматора 1 1,2..., п, j 1,2..., h, соединен с первым входом (1+1)-го разряда (-j+1)-го сумматора, второй вход (1+1)-го разряда С,-го сум- .

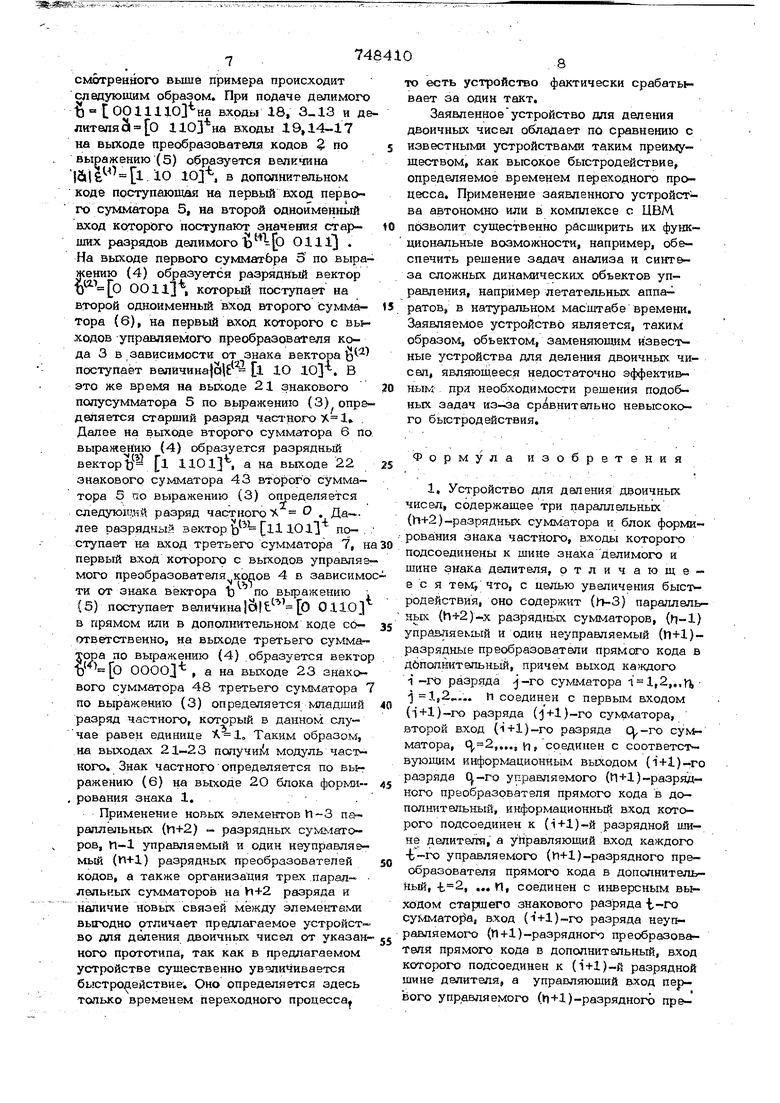

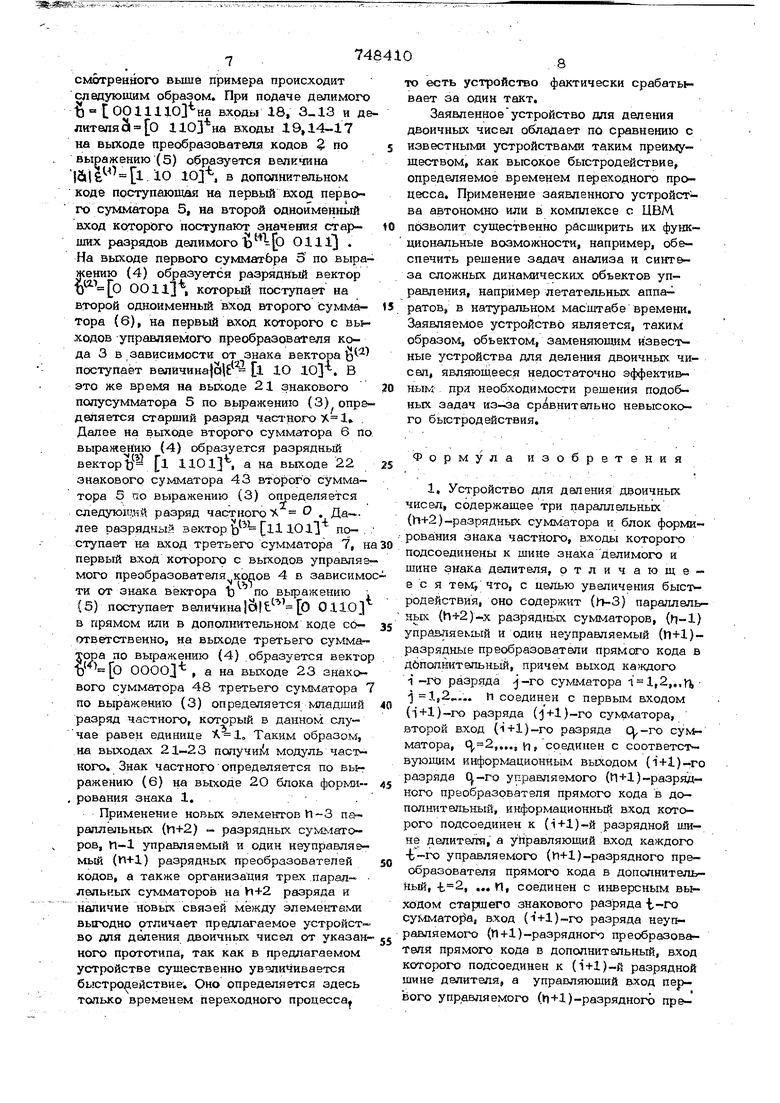

20 матора, С 2,.., П, соединен с соответствующим информационным выходом (i+1 )-го разряда управляемого (и+1)-разрядного преобразователя прямого кода в дополнительный, информационный аход которого подсоединен к (i+l)u разряд, 1ной шине дшитеяя а управляющий вход каждого t-го управляемого {1+1}-разрядного преобразователя прямого кода в дополнительный, 2,... , соединён с .инверсным выходом старшего знакового расэряда t нго сумматора, вход (1+1)-го разряда неуправляемого (h+l)ro разрядного преобразователя прямого кода в дополнительный, вход которого подсоединен к (1+1)-й разрядной шине делителя, а управляющий вход первого управляемого (П+1)-разрядного прес разователя прямого кода в дополнительный связан с выходом блока формирования знака частного, второй вход (П+2)-го разряда Г-го сумматора (,.,.П) соединен с выходом (П+1)-гх разрядного (r-l)-ro сумматора, второй аход (11+2)-го разряда второго сум матора подсоединен к выходу блока формированйя знака частного, второй вход k-ro разряда первого сумматора (/k l, ...,VI,) подключен к Ч-ой шине делимого, каждъй (п+ г)-ьй разряд делителя, К П4-2, п-ь,3,... 2П , подключен ко аходу младшего разряда р-го cyjvCMtaTOpa, ,3,...И, выход нулевого разряда .. неуправляемого (ti+ Д.)-разрядного преобразователя из прямого кода в дополнительный подсоединен ко входу переноса первого с мматора, а также тем, что в устройстве неуправляемый преобразовател прямого кода в дополнитеттьный содержит первый и второй генераторы единицы и t1 элементов НЕ, причем вход j-ro элемента НЕ (-j,..,, П+1) связан с j-ым входом преобразователя, j -ый вь4ход неуправляемого преобразоватэля прямого ко да в дополнительный, выходом нулевого разряда которого является выход первого генератора единицы, выход второго Ге йератора единицы является {11+1)-м выхбдом неуправляемого преобразователя прямого кода в допол штальный, а также тем, что в нем управляющие преобразоватеяи содержат (tt-1) сумматоров по мо дулю 2, первые входы которых объединен и являются управляющим входом управляе мого преобразователя, а вторые входы яв Л1потся соответствующими информационны аходами преобразователя, а вы.ходы сумматора по модулю 2 являются соответствуюишми информационными вьгходамй прео разователя, На чертеже представлена схема устро ствй для деления двоичнпыя чисел в частном случае, KornBi депнтапь представляется , а делимое - соответственно двоичными разрядами. Устройство содержит блок 1 формирования знака частного, неуправляемый преобразователь 2 кода из прямого в дополнительный, первый управляемый преобразователь 3 кода, второй управляемый преобразователь 4 кода, три параллельньк сумматора 5,6,7, соответственно, вход 8-13 делимого, вход 14-17 делителя, аход 18 знака делимого, акод 19 знака делителя, выход 20 знака частного, выход 21-23 модуля частного. Неуправляемьй преобразователь 2 кода состоит, например, из генератора 24 единиц, четырех инверторов 25-28, второго генератора 29 единиц. Управляемый преобразователь 3 кода состоит, например, из схем 30-33 сложения по модулю два, первые входы которых объединены между собой и являются управляющим входом преобразователя. Управляемый преобразователь 4 состоит, например, из схем 3437 сложения по модулю два, первые входы которых объединены между собой и являются управляющим входом преобраэова- твпя. Первый параллельный сумматор 5 состоит, например, из знакового полусумматора 38 и одноразрядных сумматоров 39-42о Второй параллельный сумматор 6 состоит, например из знакового одноразркдного сумматора 43 и рдноразрядньгх су;мматоров 44-47, Третий-параллельный сумматор 7 состоит, например, из знакового одноразрядного сумматора 48 и одноразрядных сумматоров 4&-52, Входы инверторов 25-28 неуправляемого .преобразователя 2 кодов и вторые одноименные входы схем 30-33 сложения по модулю два первого управляемого преоб- разоват&ля 3 кодов и 34-37 второго управляемого преобразователя 4 кодов подключены ко входам 14-17 делителя соответственно. Выходы неуправляемого преобразователя 2 кодов, инверторов 2528 подключены к первым входам первого сумматора 5, одноразрядных сумматоров 39-42, вторые одноименные входы которого соединены со входами 8-11 делимого h+1 старшими разрядами. Кроме того, первый вход знакового полусумматора 38 первого сумматора 5 и третий вход одноразрядного суммаггора 42 младшего разряда первого сумматора 5 соединен) с выходом генератора 24 и 29 единиц соответственно. Выходы первого сумматора 5, одноразрядных сумматоров 39-42 соединены со вторыми (одноименными входами второго сумматора 6 соответственно, со знаковым одноразрядным сумматором 43 и одноразрядными сумматорами 44-46, Инверсный выход 21 знакового полусумматора 38 первого сумматора 5 подключен, к первому В.ХОЛУ одноразрядного знакового сумматора 43 второго сумматора 6, управляющему входу первого управляемого преобразователя 3 кодов и ко второму одноименному аходу одноразрядного суммато ра 47 младшего разряда второго сумматора 6, Вьрсоды второго сумматора 6, одноразрядных сумматоров 44-47 соединены со вторым одноименным входом третьего сумматора 7 соответственно, со знаковым одноразрядным сумматором 48 и однораз(рядными сумматорами 49-51. Инверсный выкод 22 знакового сумматора 43 подклю чен ко входу второго одноразрядного сум.матора 48 третьего сумматора 7, к управляющему входу второго управляемого преобразователя кодов 4, и ко второму одноименному аходу одноразрядного суммато ра 52 младшего разряда третьего сумма- тора 7 . Третьи одноименные входы одноразряднык сумматоров 47,52 младших раз рядов сумматоров 6 и 7 подключены к (М+2) и (ш-3) входам 12, 13 делимого соответственно. Работу предлагаемого устройства поясним на примере определения частного . X , делимого Ъ и делителя а , предварительно представленных в разрядной форме в виде следующей зависимости: 1-ЬхГДеЪ ЗцЬ ,ЬЪ ... разрядный вектор, представля ющий разрядное изображение делимого; разрядная мата а а рица, представ ляющая собой изображ:ение делителя при x--bHX.xV.. ,..., - разрядные векторы, представл ющие собой раз рядное изображение неизвестнсго частного и нуля. процесс нахождения искомого вектора при может быть представлен в виде При этом каждый Х вектора х определяется по выражению ;.) О - .п-и.-а.-.п разрядный вектор, определяемый на оснований зависимости вида V -lb l-i2i|E ) в величина, принимающая значения ,2 л) ...-. ) . V2- t)IUl- модули векторов 4 a Из выражения (1) очевидно, что при i-1, Ъ, б . Знак частного при этом попонситепен, если знаки делимого и делителя одинаковы, -к отрицателен в противном случае. Поскольку положительный и отрицательный знаки делимого и делителя представляются логическим нулем и единицей соответственно, то знак частного вычисляется на основании выражения,- , , .. ЗнХ Ъна-Зм1эу Зий-зн-Ь (б) Для конкретных значений О sO,75; ,468755 ,625. ипн в разрядной . ррмей- Со 01 11 107 ; 0 101Уна основании выражений (2),, (3), (4), (5) получим V . 1 V « -4 2 . Ь ООНИЗ 1 - й ооооО хг (1) - + t- 11010 Г {ч 4000003 х Работа предлагаемого устройстэа Arta конкретных значений 4 IP llOj , . О 01 11 103 , 0 1010 рас-.

смотренногчэ выше примера происходит следующим образом. При подаче делимого

«{оОНЦОЗ -на входы 18, и делителя входы 19,14-17 на выходе преобразователя кодов 2 по5

выражению (5) образуется величина juj Ю . в дополнительном коде поступающая на первый вход первого сумматора 5, на второй одноименный вход которого поступают значения стар- Ю ших разрядов делимого Olll . На выходе первого сумматЬра 3 по выражению (4) образуется разрядный вектор ООН, который поступает на второй одноименный вход второго сумма- 15 тора (6), на первый вход которого с вььходов управляемого преобразователя кода 3 в зависимости от знака вектора Ь поступает веяичина о|6 fl Ю Ю}. В это же время на выходе 21 знакового 30 полусумматора 5 по вьфажению (3) определяется старший разряд частного , Далее на выходе второго сумматора 6 по выражению (4) образуется разрядный вектор ll- l а на выходе 22 25 знакового сумматора 43 второго сумматора 5 по выражению (3) определяется следуюхилй разряд частного Х О . Да-лее разрядный векторЬ lllOll по-.: ступает на нход третьего сумматора 7, на 30 первый вход которогр с выходов управляе- мого преобразователя кодов 4 в зависимоети от знака вектора Ъ по выражению (5) поступает величина1&|1 0 0110 в гфямом или в дополнительном коде об- 35 ответственно, на выходе третьего сумматора по выражению (4) образуется вектор о ООООД , а на выходе 23 знакового сумматора 48 третьего сум1 1атора 7 по выражению (3) определяется младший 40 разряд частного, который в данном случае равен единице 1, Таким образом, на вы.ходах 21-23 поп. частного. Знак частного определяется по вьн ражению (6) на выходе 2О блока форми- 45

. рования знака 1. .. .

Применение новых элементов h-3 па раллельных (Л+2) - разрядных cyiviMaTOров, ti-l управляемый и один неуправляемый () разрядньрс преобразователей 50 кодов, а также организация тре.х парал- лельных сумматоров на Vi+2 разряда и

наличие новых связей между элементами

вьах)дно отличает предлагаемое устройство для деления двоичных чисел от указан- 55 ного прототипа, так как в предлагаемом устройстве существенно ув9ли 1ивается быстродействие. Оно определяется здесь только временем переходного процесса

8

о есть устройство фактически срабатывает за один такт.

Заявленное устройство для деления двоичных чисел обладает по сравнению с известными устройствами таким преимуществом, как вьюокое быстродействие, определяемое временем переходного процесса. Применение заявленного устройства автономно или в комплексе с ЦВМ позволит существенно расширить их функциональнЫе возможности, например, обеспечить решение задач анализа и синт&за сложных динамически.х объектов управления, например летательных аппаратов, в натуральном масштабе времени. Заявляемое устройство является, таким образом, объектом, заменяющим известные устройства для деления двоичных чисел, являющееся недостаточно эффективным при необходимости решения подобных задач из-за сравнительно невысокого быстродействия.

Формула изобретения

1, Устройство для деления двоичньрс чисел, содержащее три Г1араллеяьнь х {)1+2)-разрядных сумматора и блок формирова:ния знака частного, входы которого подсоединены к шине знака делимого и шине знака делителя, ртличающе- ее я тем,что, с целью увеличения быстродействия, оно содержит ()-3) параллельных {h-i-2)-x разрядных сумматоров, (h-1) упрйвляемый и один неуправляемый (М+1)разрядньш преобразователи прямого кода в дбполнитальный, причем выход каждого 1-го разряда j-ro сумматора i 1,2,,,1т, 1,2,..,. И соединен с первьш входом (i+l)-ro разряда (j+l)-ro сумматора, второй вход (i-bl)-ro разряда cyivtматора, CJ,2,..., ti, соединен с соответствующим информационным вь1ходом (i+l)-ro разряда Ц-го управляемого (М+1)-разрядного преобразователя прямого кода в дополнительный, информационный вход которого подсоединен к {1+1)-й разрядной шине делителя, а управляющий вход каждого управляемого (h+1)-разрядного преобразователя прямого кода в дополнительный, 2, ... п, соединен с инверсным выходом старлего знакового разряда t-ro cyMMaTojia, вход (i+l)-ro разряда неуправляемого (tt+l)-разрядного преобразователя прямого кода в дополнительный, вход которого подсоединен к (i+l)-ft разрядной шине делителя, а управляющий В-ход первого управляемого (И+1)-разрядного преобразават«:я прямого кода в дополнитеш вьй связан с выходом блока формирования aUa частного, второй аход (П+2)-го разр Т-го сумматора ,...Ъ) соединен с выводом Ji+$.ro разрядного (r-D-ro . ТтоТой аход (П.2)-го разряда второго сумматора подсоединен: к вдаоду бдока формирования знака частного, второй вход. разряда первого сумматора (.... VI) подключен к 1с-ой шине двдимо го. каждый (Пн- е)гый разряд шин делителя е. . Л2. подключен ко входу младшего разряда р-го сумматора, р«2.3... П , вькод нулевого разря неуправляемого (ии)-разрядного пр образовотеля прямого кода в допопнительньй подсоединен ко входу переноса первого сумматора, 2, Устройство для деления двоичных чисаг по п. 1, о т.л и ч а ю щ е е с я тем, что в нем неуправляемый преобразователь прямого кода в дополнительный держит первый и второй генераторы едавиды и И элементов НЕ. причем вход .-го элёмеш-а НЕ (i lVi+l) связан с -Ь1М входом преобразователя, j-ый выход неуправляемого преобразователя прямого. кода в дополнительный, выходом кулевого 748 010 разряда которого го генератора вь,генератора единицы « ходом неуправляемого прямого кода в „„. 3. Ус.РОЙ-вод деления оичньа чисел по п, ° преобразова еМ, что в P iopoB по мо.тели обьедн-дудю 2. входом «ены и , „ вторые управляемо пр б аз - ; аходы „ еобразоватвпя. а модулю 2 являйся выходьтс ;: oT иoнными вьосо. . cpcrraciv-iuj.- дами.преобразователя. пами.преобразователя. Источники информации, принятые во вниманиэ при экспертизе 1.Авторское свидетельство СССР № 512469, кл. G Об F 7/52, 1974. 2.Майоров С, Д.. Новиков Т, И. Принцип организации цифровых машин. Л., „органи «« « .,- -. |1Еинос-гроение, 1974, с. ЗО4-307. Машиностроение, 1974, с, ЗО4-307. , ма во СССР 3.Авторское свидетельство СССР атл № 611507, кл. G 06 Р 7/52, 1974 (прототип).

Авторы

Даты

1980-07-15—Публикация

1978-05-04—Подача