(54) ЗАПОМИНАЮЩИЙ МОДУЛЬ ДЛЯ МАТРИЧНЫХ БЛОКОВ ПАМЯТИ

1

Изобретение относится к запоминающим устройствам.

Известен запоминающий модуль для матричных блоков памяти, содержащий двоичный запоминающий элемент с вентилями записи единицы и нуля, схему сравнения и щину опроса, причем входы схемы сравнения соединены с выходами запоминающего элемента и с шиной опроса.

В ассоциативных матрицах, построенных их таких модулей, основной операцией является поиск числа, равного заданному. Q Все другие вычислительные и информационно-логические операции осуществляются по микропрограммам, состоящим из последовательностей операций поиска и записи. В соответствии с этими микропрограммами обработка ведется последовательно по раз- 15 рядам и требует значительного времени.

Наибрлее близок к предлагаемому запоминающий модуль для матричных блоков памяти, содержащий элемент памяти, элементы И, ИЛИ и НЕ, схему сравнения, щи- д ны опроса, записи и запрета, причем первый и второй входы схемы сравнения соединены соответственно с единичным и нулевым выходами элемента памяти, а третий

и четвертый - с щиной опроса и выходом первого элемента НЕ, вход которого соединен с щиной опроса, первые входы элемента памяти подключены к щине записи, шина запрета соединена с первым входом первого элемента И, второй вход которого подключен к первому входу запоминающего модуля, а выход - к первому входу первого элемента ИЛИ, которого соединен с первым выходом запоминающего модуля, первый вход второго элемента ИЛИ соединен со вторым входом запоминающего модуля, а выход - со вторым выходом запоминающего модуля, первые входы второго и третьего элементов И соединены с третьим входом запоминающего модуля, второй и третий входы третьего элемента И соединены соответственно с щиной опроса и нулевым выходом элемента памяти, а выход третьего элемента И - со вторыми входами перйого и второго элементов ИЛИ. В ассоциативных матрицах, построенных из таких модулей, не только операция поиска по совпадению, но и ряд операций сложного поиска (поиск всех чисел, больщих заданного или меньщих заданного; поиск числа, ближайщего меньщего к заданному

поиск максимального числа; выполняются аппаратно, за одну микрокоманду. Однако и в этих ассоциативных матрицах более сложные операции (например, массовые арифметические вычисления) осуществляются с помощью микропрограмм, требующих для своего выполнения значительного времени.

Целью настоящего изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что запоминающий модуль содержит четвертый и пятый элементы И, третий, четвертый и пятый элементы ИЛИ, второй элемент НЕ и щины маскирования и настройки, причем щина маскирования соединена с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу схемы сравнения, а выход - ко второму входу второго элемента И, выход которого соединен с первыми входами четвертого элемента И и четвертого элемента ИЛИ, вторые входы которых подключены к щине настройки, соединенной также через второй элемент НЕ с первым входом пятого элемента И; выход четвертого элемента ИЛИ соединен с третьим выходом запоминающего модуля, второй вход пятого элемента И подключен к четвертому входу запоминающего модуля, а выход - к первому входу пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход - с четвертым выхрдом запоминающего модуля и со вторыми входами элемента памяти, третьи входы которого соединены с щиной запрета, а четвертые соответственно с шиной опроса и с выходом первого элемента НЕ.

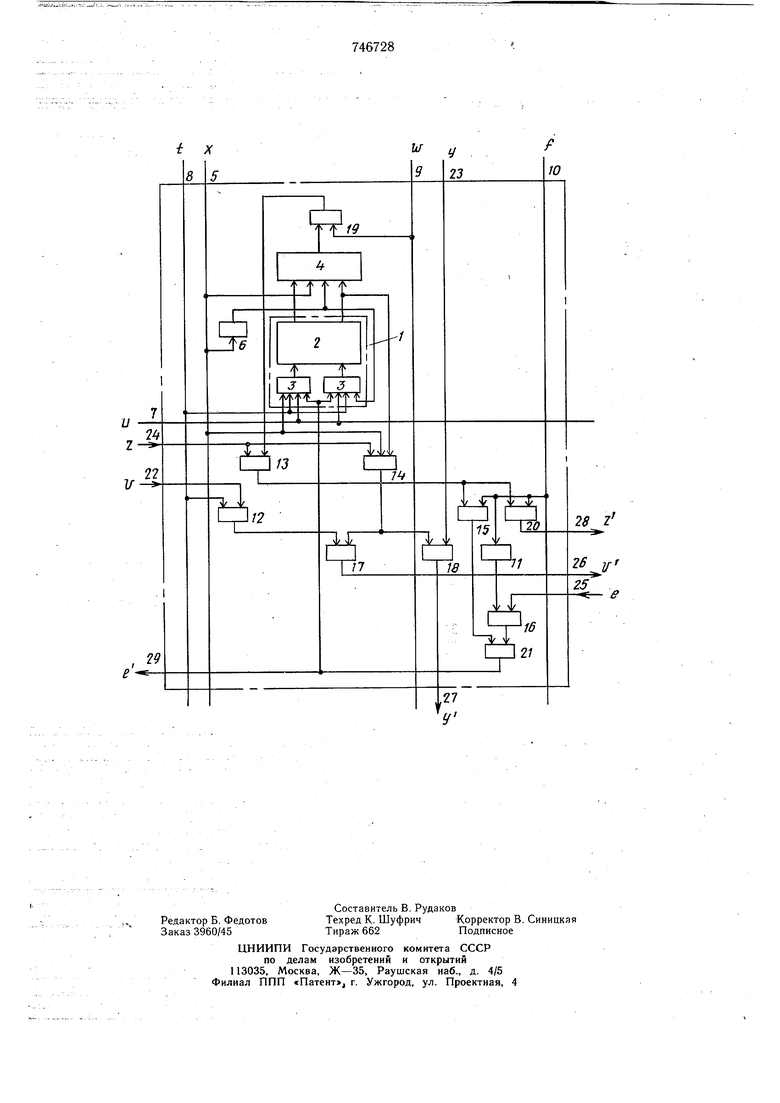

На чертеже приведена функцион;альн6логическая схема предложенного запоминающего модуля для матричных блоков памяти.

Модуль содержит элемент памяти 1, состоящий из собственно запоминающего элемента 2 и вентилей записи единицы и нуля 3, схему сравнения 4, шину опроса 5, первый элемент НЕ 6, щину записи 7, шину запрета 8, щину маскирования 9, шину настройки 10, второй элемент НЕ 11, первый 12, второй 13, третий 14, четвертый 15 и пятый 16 элементы И, первый 17, второй 18 третий 19, четвертый 20 и пятый 21 элементы ИЛИ.

Кроме того, описываемый модуль имеет входы 22-25 логических переменных v, у 2, е соответственно и выходы логических переменных v, у , z, е соответственно. Нри соединении модулей в матрицу выходы 26 и 28 каждого модуля соединяются срртветственно со входами 22 и 24 соседнего справа модуля, выход 29 со входом 25 соседнего слева модуля, а выход 27 - со входом 23 соседнего снизу модуля.

Первый и второй входы схемы сравнения 4 соединены с соответствующими выходами элемента памяти 1, а третий и чет746728

вертый входы - с шиной опроса Бис выходом элемента НЕ 6, вход которого соединен с щиной опроса 5. Шина маскирования 9 и выход схемы сравнения 4 соединены со входами элемента ИЛИ 19. Первые входы элементов И 13 и 14 соединены со входом 24. Второй вход элемента И 13 подключен к выходу элемента ИЛИ 19, а второй вход элемента И 14 - к шине опроса 5. Третий вход элемента И 14 соединен с нулевым выходом элемента памяти 1. Выход элемента И 13 соединен с первыми входами элемента И 15 и элемента ИЛИ 20, вторые входы которых подключены к шине настройки 10. Выход элемента ИЛИ 20 соединен с выходом 28, а выход элемента И 15- со вторым входом элемента ИЛИ 21, выход которого подключен к выходу 29. Первый вход элемента ИЛИ 21 соединен с выходом элемента И 16, входы которого соединень соответственно со входом 25 и через элемент НЕ 11 - с шиной настройки 10. Выход элемента И 14 соединен со вторыми входами элементов ИЛИ 17 и 18. Первый вход элемента ИЛ И 17 соединен с выходом элемента И 12, входы которого подключены соответственно ко входу 22 и к шине запрета 8. Первый вход элемента ИЛИ 18 соединен с входом 23, а выход - с выходом 27. Выход элемента ИЛИ 17 подключен к выходу 26. Первые входы элемента памяти 1 подключены к шине записи 7, вторые - к выходу элемента ИЛИ 21, третьи - к шине запрета 8, а четвертые - соответственно к шине опроса 5 и выходу элемента НЕ 6.

Как видно из чертежа, описаиный модуль

реализует следующиелогические функции:

Ь axvax(/)

z z(bva)vf(2)

v vtvzax(3)

Y Yvzax(4)

e zf(1i,vo))vef(5)

g,g XeUt(6)

g; xeut(7)

где X, f, t, (0, u соответствеино - логические переменные на шинах опроса 5, настройки 10, запрета 8, маскирования 9 и записи 7, а - состряние элемента памяти 1, V - значение двоичиой переменной на выходе схемы сравнения (предполагается, что при х а).

В ассоциативной матрице, состоящей из модулей предлагаемой конструкции, могут выполняться следующие микрокоманды:

-запись «горизонтальная,

-запись «вертикальная,

-чтение «горизонтальное,

-чтение дизъюнктивное,

-поиск по совпадению,

-поиск всех чисел, больших заданного,

-поиск всех чисел, меньших заданного. -чтение «вертикальное, -поиск ближайшего меньшего, -поиск максимального числа, -совмещенные поиск-запись. Рассмотрим в качестве примера выполнение поирка по совпадению и поиска чисел, больших (меньших) заданного. Для выполнения этих поисков на все входы 24 левой границы матрицы подаются константы «1, на все входы 22 левой границы - константы «0. На все шины 8 подаются константы «1. Состояния входов 23 и шин 10 несущественны. По шинам опроса 5 поступает поразрядно (старшими разрядами слева) код признака опроса, по шинам 9 - код маски (в маскируемых разрядах со 1). Так как, согласно (2), в каждом модуле z z(bv(o)vf, сигнал z 1 проходит в каждой строке матрицы до тех пор, пока незамаскированные разряды соответствующих чисел эквивалентны разрядам признака опроса. В частном случае, в той строке, где содержится число, равное признаку (или нескольких таких строках), на выходе 28 правой границы матрицы появится сигнал «1. Предположим, что какое-либо число совпадает с признаком опроса не по всем незамаскированным разрядам, а лишь по нескольким старшим, после чего имеется разряд, в котором а О, х 1. Ясно, что такое число меньше признака опроса, независимо от соотношения дальнейших (младших) разрядов. В том модуле, где впервые а О и X 1, схема сравнения вырабатывает Ъ О, что приводит к z 0. Однако согласно (3) в этом модуле появляется сигнал v 1, который проходит до правой границы матрицы и выдает там v 1. Итак, в любой строке матрицы, содержащей число, меньшее заданного признака, на правой границе будет z 0, v 1. Третий случай ;- число больше заданного признака. При этом нарушенне эквивалентности при просмотре слева направо происходит впервые за счет разряда, в котором а 1, X 0. В таком модуле также 1 О, z О, но v I не появляется. Следовательно, в любой строке, содержащей число, большее заданного признака, на правой границе z О, v 0. Ассоциативная матрица, построенная из описанных модулей, приобретает новые положительные свойства: в ней может выпрлняться аппаратно, с большой эффективностью, ряд информационно-логических oneраций и, кроме того, возможна независимая обработка в различных полях матрицы. ЭтМ свойства обеспечивают повышения быстродействия при решении многих задач. Формула изобретения Запоминающий модуль для матричных блоков памяти, содержащий элемент памяти, элементы И, ИЛИ и НЕ, схему сравнения, шины опроса, записи и запрета, причем первый и второй выходы схемы сравнения соединены соответственно с единичным и нулевым выходами элемента памяти, а третий и четвертый - с шиной опроса и выходом первого элемента НЕ, вход которого соединен с шиной опроса, первые входы элемента памяти подключены к шине записи, шина запрета соединена с первым входом первого элемента И, второй вход которого подключен к первому входу запоминающего модуля, а выход - к первому входу первого элемента ИЛИ, выход которого соединен с первым выходом запоминаюшего модуля, первый вход второго элемента ИЛИ соединен со вторым входом запоминающего модуля, а выход - со вторым выходом запоминающего модуля, первые входы второго и третьего элементов И соединены с третьим входом запоминающего модуля, второй и третий входы третьего элемента И соединены соответственно с щиной опроса и нулевым выходом элемента памяти, а выход третьего элемента И - со вторыми входами первого и второго элементов ИЛИ, отличающийся тем, что, с целью повышения быстродействия запоминающего модуля, он содержит четвертый и пятый ....-i. ы ,ч™..,а ,,.д ., „,,f, „« элементы И, третий, четвертый и пятый элементы ИЛИ, второй элемент НЕ и шины маскирования н настройки, причем шина маскирования соединена с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу схемы сравнения, а выход - ко второму входу второго элемента И, выход которого соединен с первыми входами четвертого элемента И и четвертого элемента ИЛИ, вторые входы которых подключены к шине настройки, соединенной также через второй элемент НЕ с первым входом пятого элемента И, выход четвертого элемента ИЛИ соединен с третьим выходом запоминающего модуля, второй вход пятого элемента И подключен к четвертому входу запоминающего модуля, а выход - к первому входу пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход - с четвертым выходом запоминающего модуля и со вторыми входами элемента памяти, третьи входы которого соединены с щиной запрета, а четвертые - соответственно с шиной опроса и с выходом первого элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

| ИЕРАРХИЧЕСКАЯ СИСТЕМА АССОЦИАТИВНОЙ ПАМЯТИ | 1992 |

|

RU2025795C1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Ассоциативная ячейка памяти | 1989 |

|

SU1635216A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| Элемент ассоциативной матрицы памяти | 1976 |

|

SU634372A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Элемент памяти ассоциативной запоминающей матрицы | 1985 |

|

SU1265857A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU842962A1 |

Авторы

Даты

1980-07-05—Публикация

1978-02-16—Подача