(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU900315A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU903983A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU907582A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1805499A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| СПОСОБ И МНОГОФУНКЦИОНАЛЬНОЕ АССОЦИАТИВНОЕ МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТРОКОВЫХ ДАННЫХ И РЕШЕНИЯ ЗАДАЧ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2582053C2 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

I

Изобретение относится к запоминающим устройствам.

Известно ассоциативное запоминающее устройство (АЗУ), содержащее элементы памяти, блоки записи, формирователи опросных токов, регистр опроса, детекторы 1.

Недостатком этого устройства являются больщие аппаратурные затраты.

Наиболее близким техническим решением к предлагаемому является АЗУ, содержащее матрицу элементов ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две группы блоков выдачи, три группы входных элементов НЕ, а также входные щины поиска (записи), щины выбора строки,, выходные щины считывания и щины результата поиска, позволяющие выполнять операции записи информации с входных щин в любые элементы ассоциативной памяти, считывание из них информации, сравнения содержимого этих элементов с информацией на входных шинах и маскирование записи и сравнение определенных столбцов памяти 2.

Однако поиск (запись) и маскирование информации производится по одним и тем

же входным щинам, что вынуждает кодировать одноразрядную информацию двумя двоичными разрядами, причем одна из четырех возможных комбинаций в этих двух разрядах является запрещенной. Кроме того, нет четкого разделения в 1 ыборе входных щин при различных режимах работы. В частности, во время режима чтения на щины поиска (записи) должен подаваться уровень логической единицы, а при режиме поиска уровень логической единицы должен подаваться на щины выбора строки. Это вызывает усложнение управлений при работе с АЗУ и ограничивает возможности его применения.

Цель изобретения - упрощение устройства и расщирение области его применения за счет обеспечения возможности отделения

s маскирующих щин от информационных и исключения запрещенной комбинации на этих входах, четкого разделения в выборе входных щин при различных режимах работы.

Поставленная цель достигается тем, что в ассоциативное запоминающее устройство, содержащее матрицу элементов памяти, первый группы элементов НЕ и блоков выдачи данных - по числу строк матрицы, вторую и третью группы элементов НЕ и вторую группу блоков выдачи данных - по числу столбцов матрицы, причем выходы элементов НЕ первой группы подключены к первым входам элементов памяти одноименных строк матрицы, выходы элементов НЕ второй и третьей групп соединены соответственно со вторыми и третьими входами элементов памяти одноименных столбцов матрицы, входы блоков выдачи данных первой и второй групп подключены соответственно к первым и вторым выходам элементов памяти одноименных строк и столбцов матрицы, введены первый и второй элементы И-НЕ, группа элементов И-НЕ и логические блоки, причем выход первого элемента И-НЕ подключен к одним из входов элементов И-НЕ группы, выходы которых соединены со входами элементов НЕ первой группы, выход второгоэлемента И-НЕ подключен к одним из входов логических блоков, выходы которых соединены со входами элементов НЕ второй и третьей групп, первые входы первого и второго элемента И-НЕ объединены и являются одним из управляющих входов устройства, -другими управляющими входами которого являются вторые входы первого и второго элементов И-НЕ и другие входы логических блоков и элементов И-НЕ группы.

При этом логический блок целесообразно выполнять в виде блока, содержащего элементы И-НЕ и элемент НЕ, выход и вход которого подключены к первым входам элементов И-НЕ, вторые и третьи входы которых объединены соответственно и являются одними из входов логического блокаГ другим входом которого является вход -элем ента НЕ, а выходы элементов И-НЕ являются выходами логического блока.

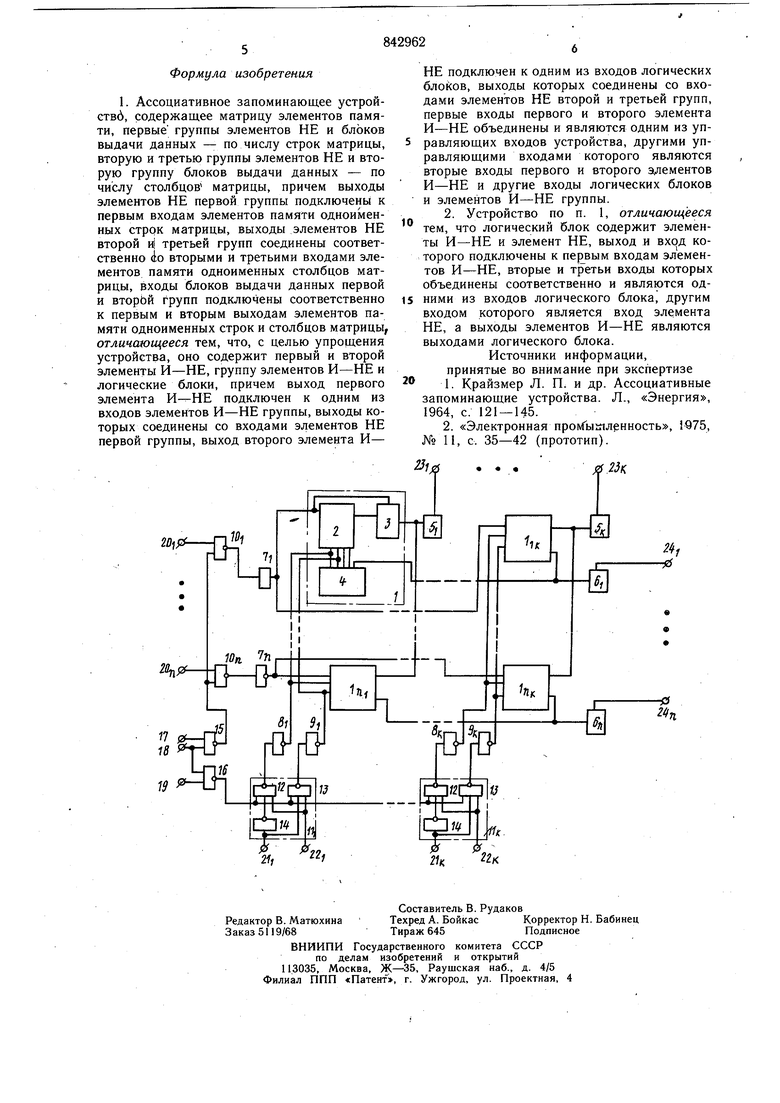

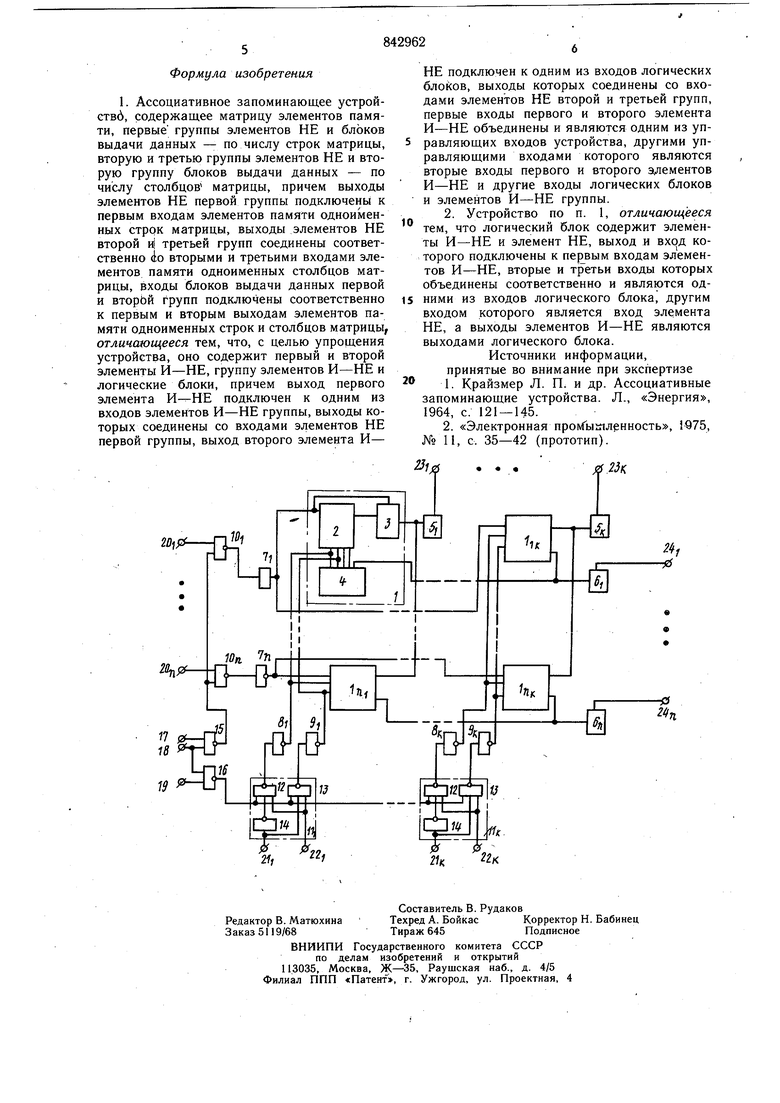

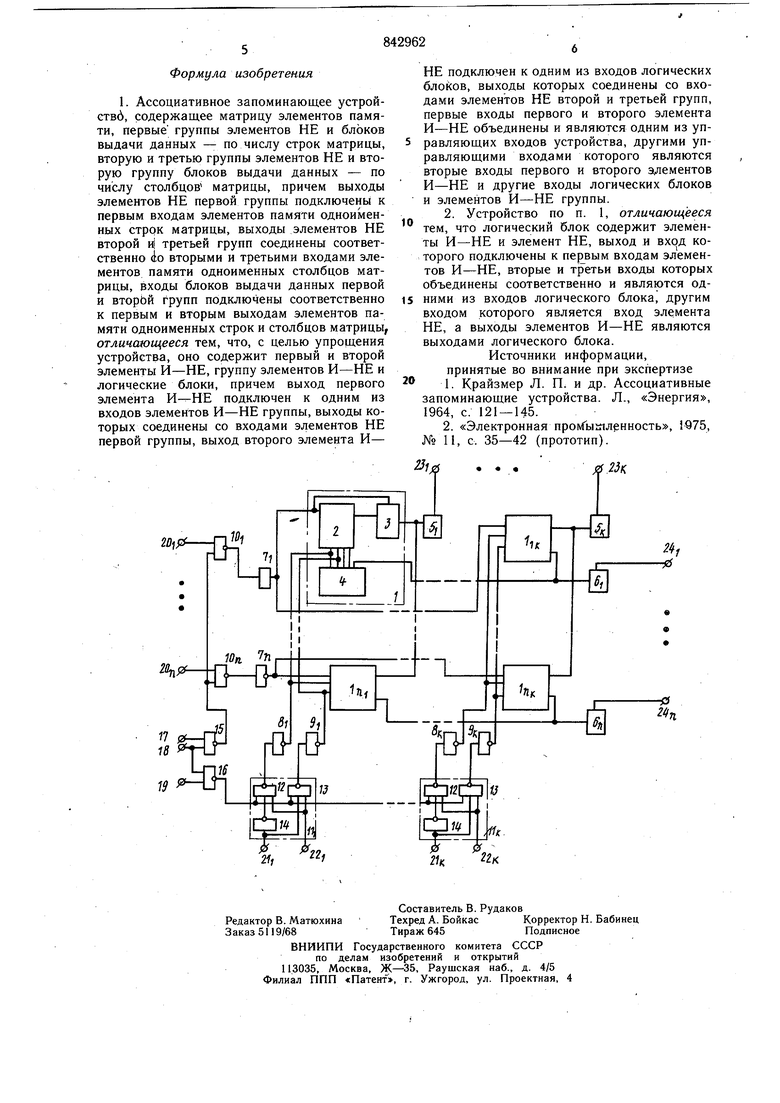

На чертеже изображена структурная схема предлагаемого АЗУ.

Устройство содержит матрицу элементов Ьх - 1пк памяти, состоящую из п строк и; К столбцов. Каждый элемент 1 памяти состоит из запоминающей ячейки 2, блока 3 считывания и схемы 4 сравнения. Устройство также содержит первую группу блоков 5/ - 5 к выдачи данных, вторую группу блоков 6/ -6 д выдачи данных, первую, вторую и третью группы элементов НЕ 7, - 7, 8,- 8к и 9| - 9д, группу элементов И-НЕ 10,- 10д, логические блоки 11| - 11, каждый из которых состоит из элементов И-НЕ 12 и 13 и элемента НЕ 14.

Устройство содержит первый 15 и второй 16 элементы И-НЕ, входные щины чтения 17 и записи 18 режимов, щины 19 поиска, щины 20 - 20и. выбора строки, информационные щины 211-2 ц, маскирующие щины 22, - 22;, выходные щины 23 - 23, считывания слова и щины 24/ - 24 результатов поиска.

Выход элемента И-НЕ 15 подключен к одним из входов элементов И-НЕ 10, - 10д,

выход элемента И-НЕ 16 подключен к одним из входов блоков. 11, - 11(, выходы которых соединены с входами элементов НЕ 8) -8,( и 9, -9к, первые входы элементов И-НЕ 15 и 16 объединены и являются одним из управляющих входов устройства, другими управляющими входами которого являются вторые входы элементов И-НЕ 15 и 16 и другие входы блоков 11, - 1U и элементов И-НЕ 10, - 10.

Каждый из блоков 11, - 11д содержит

элементы И-НЕ 12 и 13 и элемент НЕ 14, выход и вход которого подключен к первым входам элементов И-НЕ 12 и 13, вторые и третьи входы объединены соответственно и являются одними из входов блока 11, другим входом которого является вход элемента НЕ 14, а выходы элементов И-НЕ 12 и 13 являются выходами блока П.

Устройство работает следующим образом.

В режиме чтения сигнал логического «О с щины 17, проходя через элемент 15, разрещает вь|бор элементов 1 памяти любой строки. Одновременно работа с элементами памяти по информационным 21 - 21 и маскирующим 22, - 22л.щинам запрещается с выхода элемента 16. Считываемая информация из элементов 1 памяти выбранной строки через соответствующие блоки 5| - 5 поступает на выходные щины 23/ - 23«.считывания слова. В режиме записи обращение к элементам 1 памяти разрещается одновременно по щинам 20| - 20. выбора строки и по информационным 21 - 21к И маскирующим 22, - 22дщинам. В элементы 1 памяти выбранной строки записывается информация, соответствующая уровням на входных информационных щннах 21| - 21х. Причем запись информации происходит только в незамаскированных входными маскирующими щинами 22j- 22 элементах I памяти строки. В режиме поиска выбор строки запрещается с выхода элемента 15, а элемент И-НЕ 16 разрещает работу по информационным 21/ - маскирующим 22, - 22 X щинам.

Информация, -находящаяся в элементах I памяти сравнивается с информацией, поступающей на входные информационные щины 21,-2U.

Результат поиска с блоков 6, - бд поступает на выходные щины 24, - 24. Причем сравнение с входной информацией происходит только в незамаскированных входными маскирующими щинами 22, - 22 элементах 1 памяти строки.

Предлагаемое устройство по сравнению с известными обладает упрощенным управлением, раздельными щинами маскирования и

5 информации, в нем исключена запрещенная комбинация (;игналов на щинах, строго разграничен выбор входных щин при различных режимах работы.

Авторы

Даты

1981-06-30—Публикация

1979-08-21—Подача