(54) АССОЦИАТИВНЫЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающий элемент | 1980 |

|

SU928415A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ячейка ассоциативной памяти | 1990 |

|

SU1751817A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1805499A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

I

Изобретение относнгся к запоминающим устройствам.

Известен ассоциативный запоминающий элемент, содержащий триггер, адресную шину, элементы управления записью, разрядные шины нуля и единицы, элементы управления считыванием, логический вход и выход ячейки, шину нулевого потенциала, инвертор, восстанавливающий вентиль, ключевой вентиль, логический элемент ИЛИ-НЕ и параллельно соединенные чередаюшие вентили l.

Недостатком этого ассоциативного запоминающего элемента является большое число логических элементов и связей, что усложняет ячейку и матрицу ассоциативной памяти.

Наиболее близким техническим решением к предлагаемому изобретенвпо является запоминающий элемент асссщиативнсЛ матрицы, содержащий триггер с двумя входными схемами И, две схемы И считывания информации, схему ИЛИ, схему НЕ, две выходньос схемы И, две вы«

ходаых схемы ИЛИ, пять входаых и пять выходных шин Г2.

Недостатком этот-о элемента ассоциативной матрицы является большое число лся: ических элементов и связей, что усложняет ячейку и матрицу ассоаяативноА памяти и снижает быстродействие асс яватввного щэооессора при выпопненин операций чтения и асссщнативного поиска.

Цель изобретения - повышение быстро действия ассоциативного запоминающего элемента.

Поставленная цель достигается тем, что в ассоциативный запоминающий элемент, содержащий триггер, четьцзе элемента И и первый элемент ИЛИ, причем выходы первсжо я второго элементов И подключены соответственно к ёдвйнчному и нулевому входам триггера, единичный и нулевсй выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, выходы которых подключены соответственно к первому и второму входом первого эле-

мента ИЛИ, первые входы первсго и второго элементов И и третий вход первого элемента ИЛИ соединены соответственно с первыми входом и выходом, со вторыми входом и выходом и третьими входом и выходом accouHaTHBHWO запоминающего элемента, введены второй элемент ИЛИ и пятый элемент И, первый и второй входы которого подключены соответственно к выходу первого элемента ИЛИ и четвертому выходу н к четвертому входу ассоциативного запоминающего элемента, выход второго элемента ИЛИ соединен со вторым входом третьего элемента И, а первый и второй входы подключены соответственно к пятым входу и выходу и к первым входу н выходу ассоциативного запоминающего элемента, втqDoй, третий и четвертый входы первого элемента И и второй вход втфого элемента И соединены соответственно с шестым входом и выходом, со вторыми входом и выходом, с седьмыми входом и выходом и с восьмыми входом и выходом ассоциативного запоминающего элемента, а выход пятого элемента И и епи 1ичный выход триггера соответственно с девятым и с десятым выходами ассоциативного запоминающего элемента.

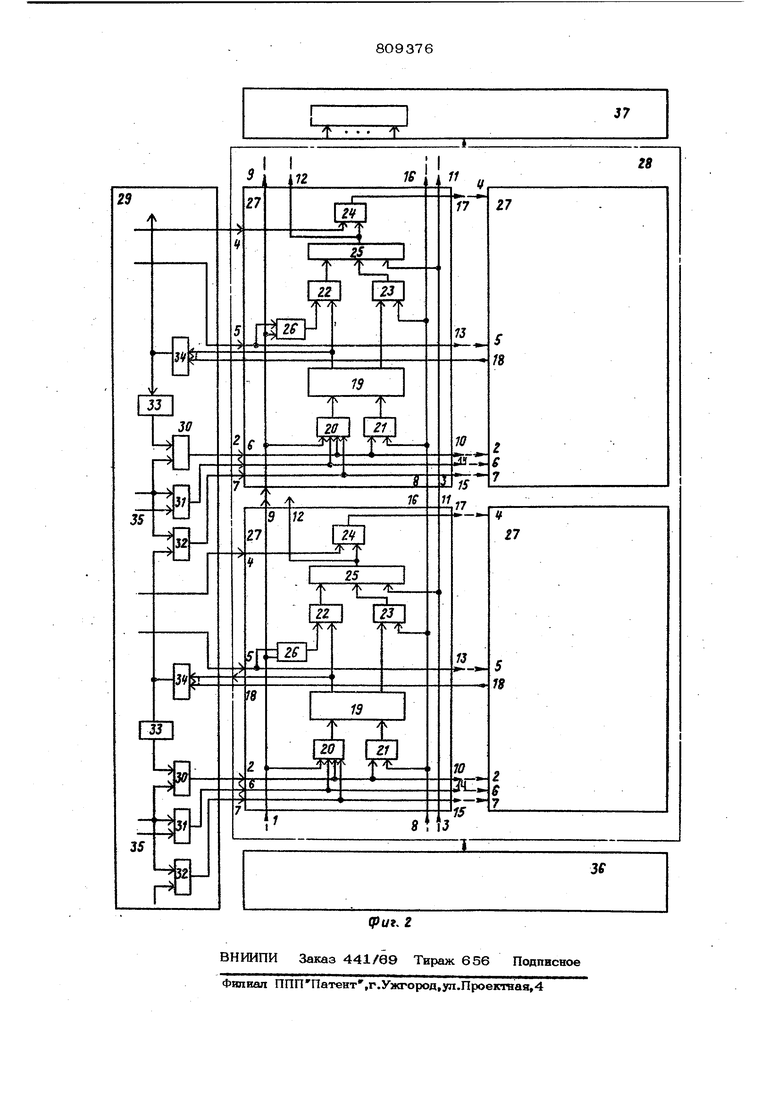

На фиг. 1 изображена структурная схема предлагаемого ассоциативного запоминающего элемента; на фиг. 2 - фунциональная схема ассоциативного процессора, в котором применяется предлагаемый элемент.

Предлагаемый элемент содержит (фиг, 1 и фиг. 2) входы 1-8, выходы 9-18, триггер 19, первый 20, второй 21, третий 22, четвертый 23 и пятый 24 элементы И, первый 25 и второй 26 элементы ИЛИ.

Выходы первого 2О и второго 21 элментов И подключены соответственно к единичному и нулевому входам триггера 19, единичный и нулевой выходы которого соединены соответственно с первыми входами третьего 22 и четвертого 23 элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента 25 ИЛИ, Первые входы первого 2О и второго 21 элементов И и третий вход первого элемента 25 ИЛИ соединены соответственно с первыми входом 1 и выходом 9, со вторыми входом 2 и выходом 1О и третьими входом 3 и выходом 11 ассоциативного запоминающего элемента. Первый и второй входы пятого

элемента 24 И подключены соответственно к .выходу первого элемента 25 ИЛИ и четвертому выходу 12 и к четвер- тому входу 4 ассоциативного запоминающего элемента. Выход второго элемента 26 ИЛИ соединен со вторым входом третьего элемента 22 И, а первый и второй входы подключены соответственно к пятым входу 5 и выходу 13 и к первым входу 1 иВЫХОДУ 9 ассоциативного запоминающего элемента. Второй, третий и четвертый входы первого элемента 20 И и второй вход второго элемента 21 И соединен соответственно с шестыми входом б и выходом 14, со вторыми входом 2 и выходом 10, с седьмыми входом 7 и выходом 15 и с восьмыми входом 8 и выходом 16 ассоциативного запоминающего элемента. Выход пятого элемента 24 И и единичный вьсход триггера 19 соединен соответственно с девятым 17 н с десятым 18 выходами ассоциативного запоминающего элемента.

Ассоциативный процессс э содержит {фиг. 2) ассоциативные запоминающие элементы 27, накопитель 28, представляющий собой матрицу, блок 29 местного управления, третий ЗО, четвертый 31 и пятый 32 элементы ИЛИ, элемент 33 НЕ и щестой 34 элемент И ЛИ-по числу строк матрицы накопителя, входящие в блок местного упраншения, шину 35 записи, блоки 36 ввода и выводы 37 информации. Первый 9, третий 11 и восьмой 16 выходы каждого предыдущего ассоциативного запоминающего элемента 27, кроме первого, соединены соответственно с первым 1, с третьим 3 и восьмым 8 входами последующего в столбце матрицы накопителя 28 ассоциативного запоминающего элемента 27, кроме последнего. Второй 1О, пятый 13, шестой 14, седьмой 15 и девятый 17 выходы каждого предыдущего ассоциативного запоминающего элемента 27 подключены соответственно ко второму 2, к пятому 5, к шестому 6, к седьмому 7 и к четвертому 4 входам последующего в строке накопителя 28 ассоциативного запоминающего элемента 27, кроме входящих в 50 первый столбец накопителя 28. Второй 2, щестой 6, и седьмой 7 входы и десятый 18 выход каждого ассмхиативного запоминающего элемента 27 первого столбца накопителя 28 соединен соответственно 55 с вькодами третьего ЗО, четвертого 31 и пятого 32 и со входом шестого 34 элементов ИЛИ, Первые 1, третьи 3 и восьмые 8 входы ассоциативных запоминающих элементов 27 первой строки накопителя 28 подключены к выходам блсжа 36 ввода. Первый вход третьего элемента ЗО ИЛИ соединен с выходом элемента 33, вход которого подключен к выходу шестого элемента 3 t ИЛИ своей строки накопителя 28 и к первому входу пятого элемента 32 ИЛИ следующей строки накопителя 28. Один из входов четвертого элемента 31 ИЛИ соединен со вторыми входами третьего ЗО и пятого 32 элементов ИЛ Элемент работает следующим образом Предлагаемый ассоциативный запомин ющий элемент позволяет реализовать ассоциативный процессор (фиг.2), имеющий пять режимов работы запись с опросом, запись без опроса, чтение, ассоциативны поиск и поиск максимума. Работу ассоциативного запоминающего элемента рассмотрим на прикгерах выполнения записи без предварительного опроса и ассоциативното поиска. Записыв емое слово подается на входы первой строки матрицы 28 таким образом, что прямой кбд каждого разряда слова посту пает на первый вход 1, а обратный код этого же разряда - на восьмой вход 8 ассоциативного запоминающего элемента 27 соответствующего столбца накопителя 28. Запись без предварительного опроса матрицы накопителя 28 производится пр поступлении новой информации, которая должна быть записана любую свободную строку матрицы накопителя 28. В каждой из занятых информацией строк матрицы накопителя 28 единичный сигнал триггера 19 какого-либо из ассо циативных запоминающих элементов 27, аройдя с выхода 18 через шестой элемент 34 ИЛИ, проинвертнруется элементом 33 НЕ. При этом через третий элемент 30 ИЛИ на вход 2 каждого из ассоциативных запоминающих элементов 27 данной строки будет подан нулевой сигна который закроет для записи информации первый 20 и второй 21 элемент И всех ассоциативных запоминающих элементов 27 этой строки. Одновременно этот же сигнал поступает на седьмые входы 7 ассоциативных запоминающих элементо 27 следующей строки, разрешая запись в нее информации. Если эта строка нако пителя 28 свободна от инфс мацин, тонулевые сигналы с выходов триггеров 19 через выходы 18 ее ассоциативных элементов пройдут как сигналы обратной СВЯЗИ 1 на вторые 2 входы своей Ьтроки, разрешая запись информации в нее. Эти же нулевые сигналы с входов триггеров 19 через шестые 34 и пятые 32 элементы ИЛИ пройдут на седьмые 7 входы ассоциативных запоминающих элементов 27 следующей строки и закроют ее для записи информации. Одновременно с шины записи 35 на вход четвертого элемента З; ИЛИ подается единичный сигнал Запись, проходящий на входы 6 всех ассоциативных запоминающих элементов 27. При этом открыта для записи только первая после занятой свободная строка накопителя 28, в которую и будет записана информация без предварительного опроса накопителя 28. При ассоциативном поиске разряды признака опроса подаются с блока 36 вводана входы нижней строки накопителя 28 таким образом, что прямой код каждого разряда признака опроса подается на вход 1, а обратный код этого же разряда - на вход 8 соответствующего столбца накопителя 28. Маскирование опроса производится путем подачи сигнала на входы 3 соответствующих столбцов матрицы 28. На все входы 4 левого столбца накопителя 28 подается сигнал . При этом сигнал появится на выходах 17. правого столбца матрицы в тех и только тех строках, в которьсх содержимое всех незамаскированных разрядов совпадает с кодами соответствующих разрядов признака опроса.-. Технико-экономическое преимущество предлагаемого ассоциативного запоминающего элемента заключается в том, что он позволяет реализовать режим записи информации в свободную строку накопителя без предварительного опроса всего накопителя, а также в сокращении числа логических элементов по сравнению с известным элементом, за счет чего повышается быстродействие при выполнении операций записи н ассоднативного поиска накопителе. Формула изобретения АссоциативньЕЙ запоминающий элемент, содержащий триггер, четыре элемента И и первый элемент ИЛИ, причем выходы первого и второго элементов И подключены соответственно к единичному и нулевому входам триггера, единичный н нуле- ой выходы KOTojioro соединены соответстВ6ННО с первыми входами трегьего и четвертого элемента И, выходы которых подклкгчены соответственно к первому и второму входам первого элемента ИЛИ, первые входы первого и второго элементов И и вход первого элемента ИЛИ соединены соответственно б первыми входом в выходом, со вторыми входом и выходом и с третьими вводом и выходом ассоаватйвного запоминающего элемента, отличающийся тем, что, с целью повышения быстродействия еж содержит второй элемент ИЛИ и пятый элемен И, первый и второй входы которого подключены соответственно к выходу первого элемента ИЛИ и четвертому выходу и к четвертому входу ассоциативного запоминающего элемента, выход второго элемента ИЛИ соединен со вторым входом третьего элемента И, а первый и второй входы подклютены соответственно к пяты

9 3

(put.f входу н выходу и к первым входу и выходу ассоциативного запоминающего элемента, второй, третий и четвертый входы первого элемента И и второй вход второго элемента И соединены соответственно с шестым входом и выходом, со вторыми входом и выходом, с седьмыми входом и вькодом и с восьмь1ми входом и выходом ассоциативного запоминающего элемента, а выход пятого элемента И и единичный .вькод триггера - соответственно с девятым и с десятым выходами ассоциативнсго запоминающего элемента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 513393, кл. Q 11 С 15/ОО 1974. 2.Авторское свидетельство СССР № 478297, кл. Q Об Р 1/ОО, 1973 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-05-11—Подача