Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано в цифровых системах обработки информации.

Цель изобретения - расширение функциональных возможностей матрицы за счет обеспечения ассоциативного цоиска слова, ближайшего к признаку поиска.

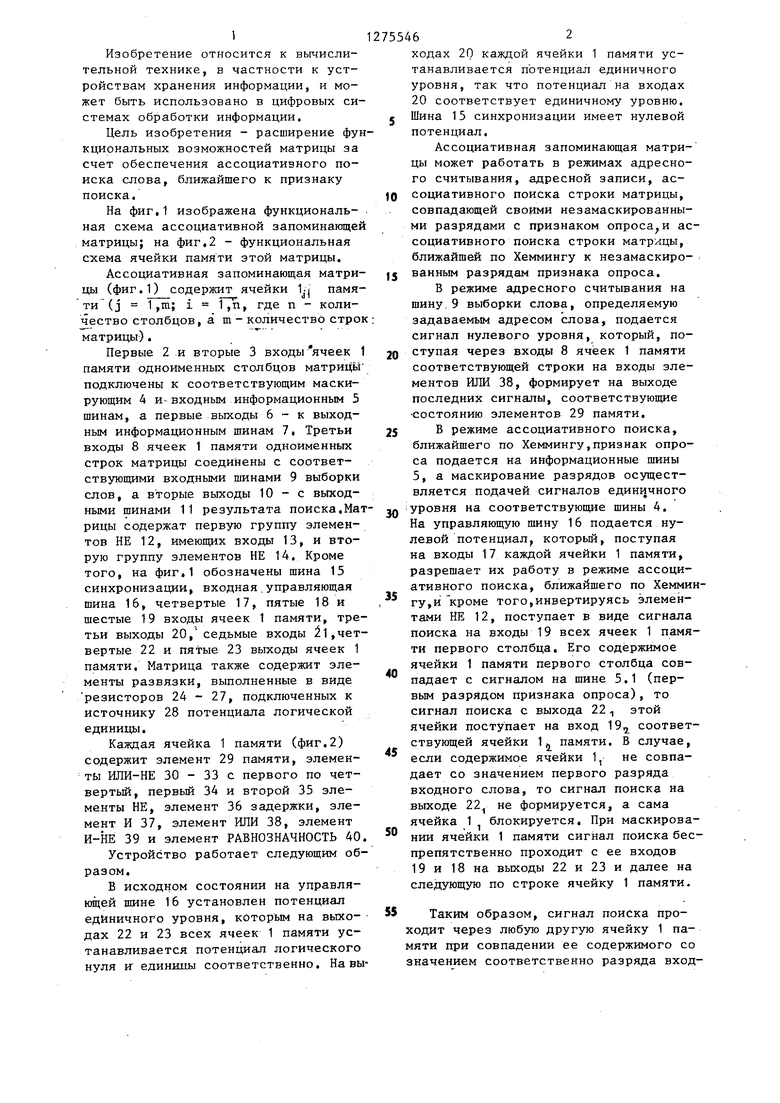

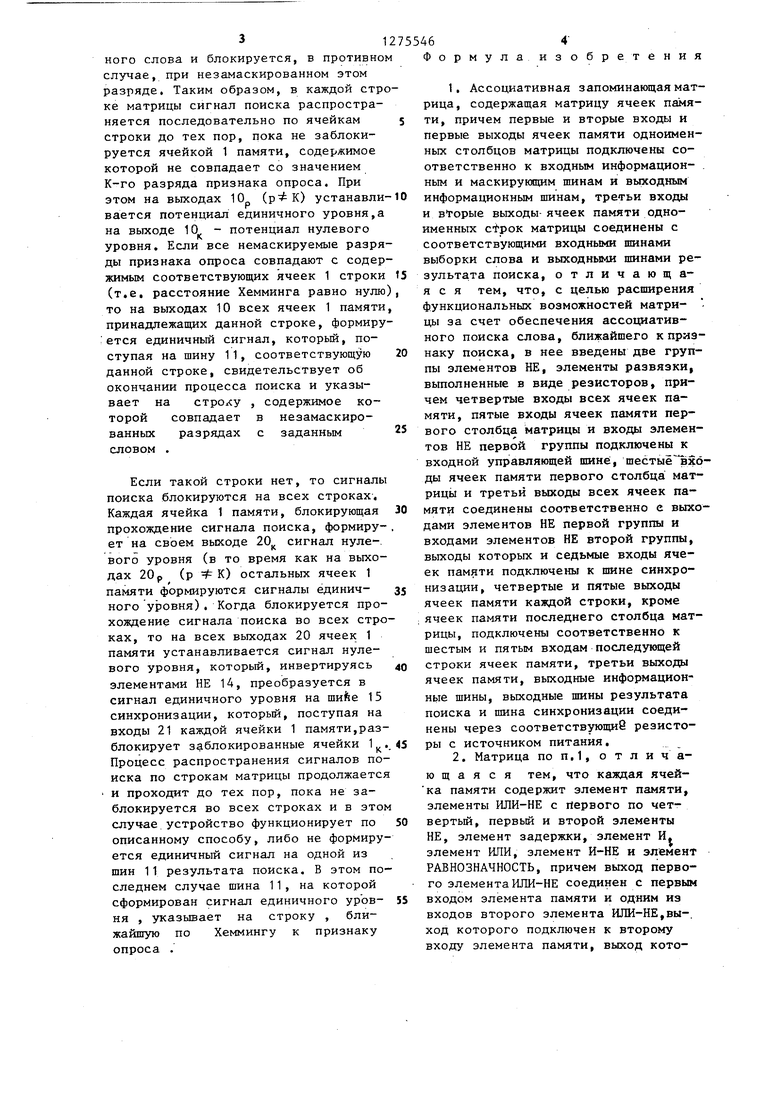

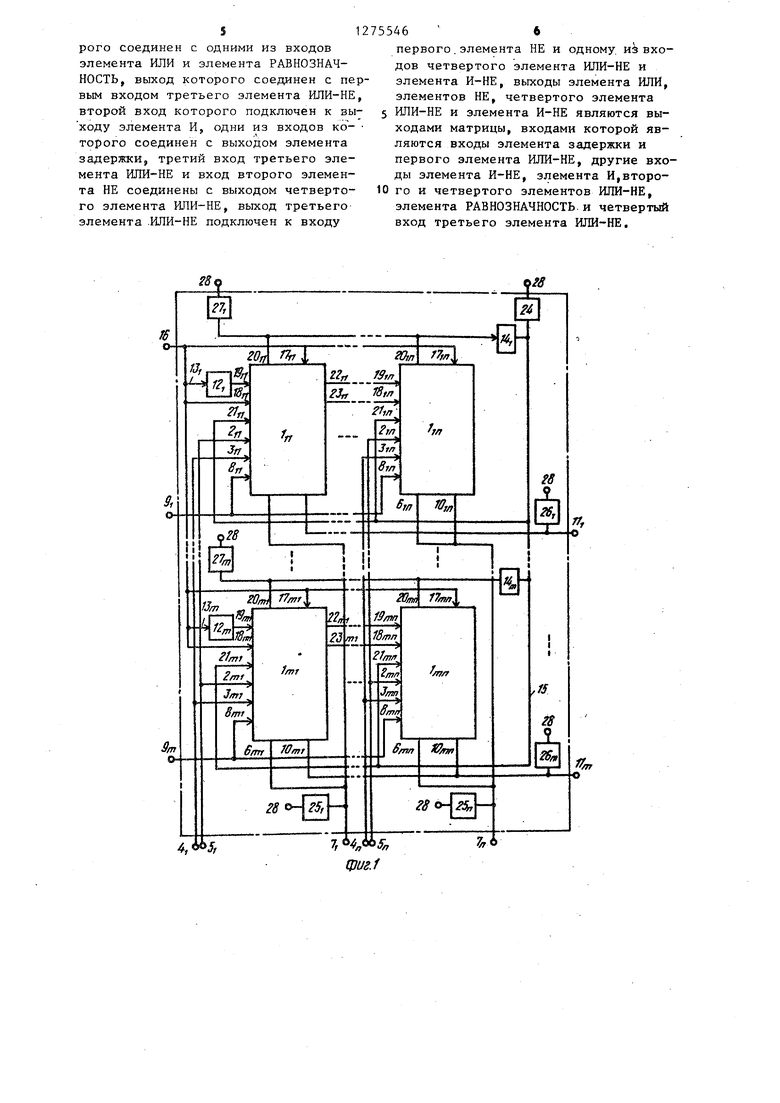

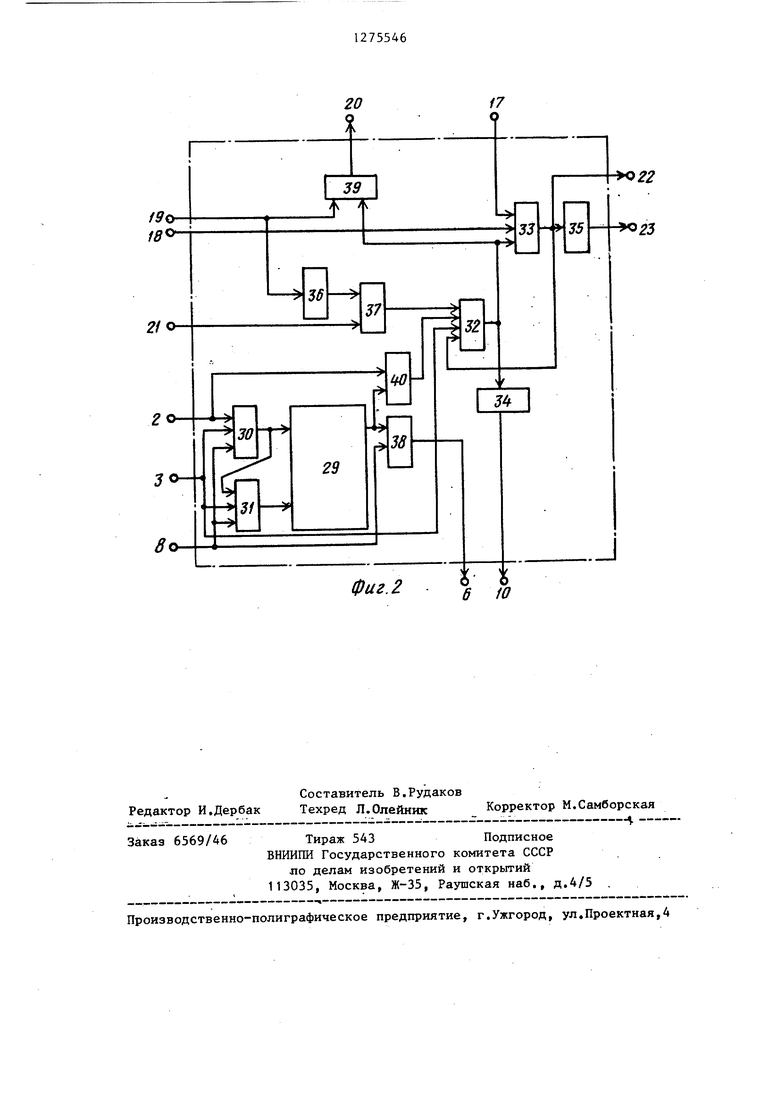

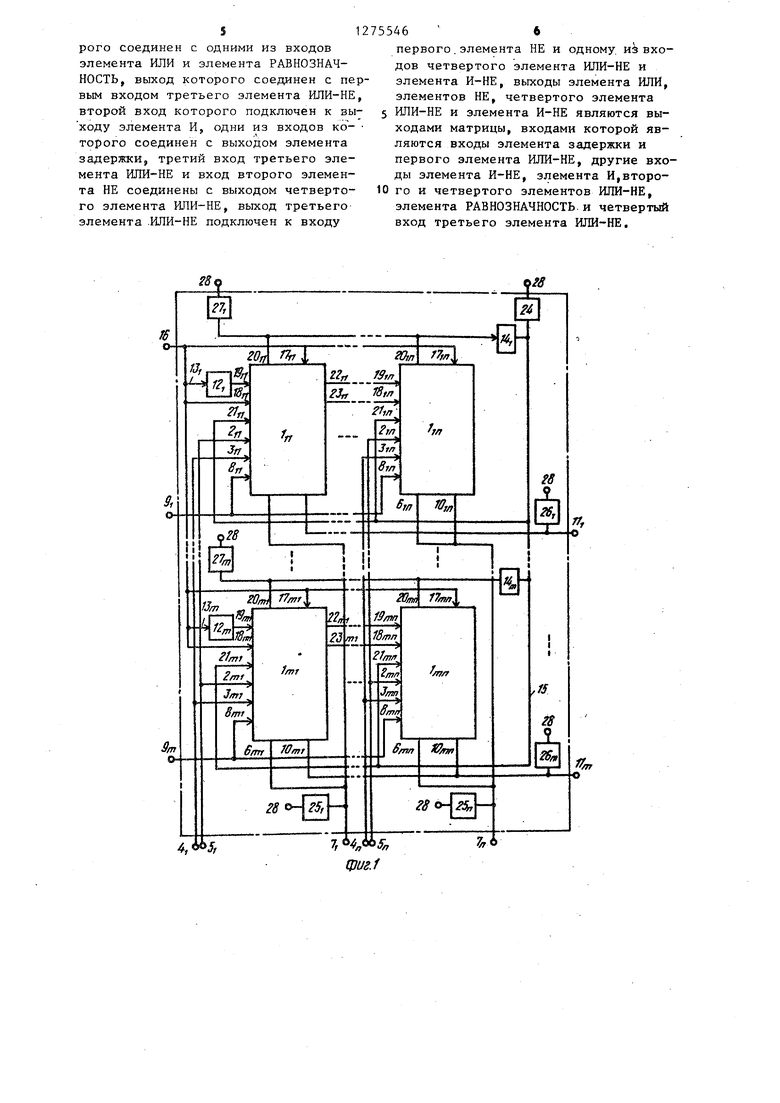

На фиг,1 изображена функциональная схема ассоциативной запоминающей матрицы; на фиг,2 - функциональная схема ячейки памяти этой матрицы.

Ассоциативная запоминающая матрицы (фиг. 1 содержит ячейки 1jj памяти (j 1 ,m; i lT где n - количество столбцов, а m - количество строк матрицы),

Первые 2 и вторые 3 входыячеек 1 памяти одноименных столбцов матрицы подключены к соответствующим маскирующим 4 и-входным информационным 5 шинам, а первые выходы 6 - к выходным информационным шинам 7, Третьи входы 8 ячеек 1 памяти одноименных строк матрицы соединены с соответствующими входными шинами 9 выборки слов, а вторые выходы 10 - с выходными шинами 11 результата поиска,Матрицы содержат первую группу элементов НЕ 12, имеющих входы 13, и вторую группу элементов НЕ 14, Кроме того, на фиг,1 обозначены шина 15 синхронизации, входная,управляющая шина 16, четвертые 17, пятые 18 и шестые 19 входы ячеек 1 памяти, третьи выходы 20, седьмые входы И1,четвертые 22 и пятые 23 выходы ячеек 1 памяти. Матрица также содержит элементы развязки, выполненные в виде резисторов 24 - 27, подключенных к источнику 28 потенциала логической единицы.

Каждая ячейка 1 памяти (фиг,2) содержит элемент 29 памяти, элемен- ты ИЛИ-НЕ 30 - 33 с первого по четвертьш, первый 34 и второй 35 элементы НЕ, элемент 36 задержки, элемент И 37, элемент ИЛИ 38, элемент И-НЕ 39 и элемент РАВНОЗНАЧНОСТЬ 40,

Устройство работает следующим образом,

В исходном состоянии на управляющей щине 16 установлен потенциал единичного уровня, которым на выходах 22 и 23 всех ячеек 1 памяти устанавливается потенциал логического нуля и единицы соответственно. На выходах 20 каждой ячейки 1 памяти устанавливается потенциал единичного уровня, так что потенциал на входах 20 соответствует единичному уровню, 5 Шина 15 синхронизации имеет нулевой потенциал.

Ассоциативная запоминающая матрицы может работать в режимах адресного считывания, адресной записи, ас0 социативного поиска строки матрицы, совпадающей своими незамаскированными разрядами с признаком опросами ассоциативного поиска строки матрицы, ближайшей по Хеммингу к незамаскироj ванным разрядам признака опроса,

В режиме адресного считывания на шину.9 выборки слова, определяемую задаваемым адресом слова, подается сигнал нулевого уровня, который, по0 ступая через входы 8 ячеек 1 памяти соответствующей строки на входы элементов ИЛИ 38, формирует на выходе последних сигналы, соответствующие состоянию элементов 29 памяти, 5 В режиме ассоциативного поиска, ближайшего по Хеммингу,признак опроса подается на информационные шины 5, а маскирование разрядов осуществляется подачей сигналов единичного л iуровня на соответствующие шины 4, На управляюшую шину 16 подается нулевой потенциал, который, поступая на входы 17 каждой ячейки 1 памяти, разрешает их работу в режиме ассоциативного поиска, ближайшего по Хеммингу, и кроме того,инвертируясь элементами НЕ 12, поступает в виде сигнала поиска на входы 19 всех ячеек 1 памяти первого столбца. Его содержимое ячейки 1 памяти первого столбца совпадает с сигналом на шине 5,1 (первым разрядом признака опроса), то сигнал поиска с выхода 22 этой ячейки поступает на вход 19 соответствующей ячейки 11 памяти, В случае, если содержимое ячейки 1, не совпадает со значением первого разряда входного слова, то сигнал поиска на выходе 22 не формируется, а сама ячейка 1 блокируется. При маскировании ячейки 1 памяти сигнал поиска беспрепятственно проходит с ее входов 19 и 18 на выходы 22 и 23 и далее на следующую по строке ячейку 1 памяти.

Таким образом, сигнал поиска проходит через любую другую ячейку 1 памяти при совпадении ее содержимого со значением соответственно разряда входного слова и блокируется, в противно случае, при незамаскированном этом разряде. Таким образом, в каждой стр ке матрицы сигнал поиска распространяется последовательно по ячейкам строки до тех пор, пока не заблокируется ячейкой 1 памяти, содержимое которой не совпадает со значением К-го разряда признака опроса. При этом на выходах 10 (р К) устанавли вается потенциал единичного уровня,а на выходе 10 - потенциал нулевого уровня. Если все немаскируемые разря ды признака опроса совпадают с содер жимым соответствующих ячеек 1 строки (т.е. расстояние Хемминга равно нулю то на выходах 10 всех ячеек 1 памяти принадлежащих данной строке, формиру ется единичный сигнал, который, поступая на шину 11, соответствующую данной строке, свидетельствует об окончании процесса поиска и указывает на , содержимое которой совпадает в незамаскированных разрядах с заданным словом . Если такой строки нет, то сигналы поиска блокируются на всех строках. Каждая ячейка 1 памяти, блокирующая прохождение сигнала поиска, формирует на своем выходе 20| сигнал нуле-, вого уровня (в то время как на выходах 20р (р К) остальных ячеек 1 памяти формируются сигналы единичного уровня). Когда блокируется прохождение сигнала поиска во всех стро ках, то на всех выходах 20 ячеек 1 памяти устанавливается сигнал нулевого уровня, который, инвертируясь элементами НЕ 14, преобразуется в сигнал единичного уровня на шийе 15 синхронизации, который, поступая на входы 21 каждой ячейки 1 памяти,разблокирует заблокированные ячейки 1 . Процесс распространения сигналов поиска по строкам матрицы продолжается и проходит до тех пор, пока не заблокируется во всех строках и в этом случае устройство функционирует по описанному способу, либо не формируется единичный сигнал на одной из шин 11 результата поиска. В этом последнем случае шина 11, на которой сформирован сигнал единичного уровня , указывает на строку , ближайшую по Хеммингу к признаку опроса . 46 Формула бре тения 1.Ассоциативная запоминающая матрица, содержащая матрицу ячеек памяти, причем первые и вторые входы и первые выходы ячеек памяти одноименных столбцов матрицы подключены соответственно к входным информацион- . ным и маскирукщим шинам и выходным информационным шинам, третьи входы и вторые выходы- ячеек памяти одноименных сфрок матрицы соединены с соответствующими входными шинами выборки слова и выходными шинами результата поиска, отличающаяся тем, что, с целью расширения функциональных возможностей матри- цы за счет обеспечения ассоциативного поиска слова, ближайшего к признаку поиска, в нее введены две группы элементов НЕ, элементы развязки, выполненные в виде резисторов, причем четвертые входы всех ячеек памяти, пятые входы ячеек памяти первого столбца матрицы и входы элементов НЕ первой группы подключены к входной управляющей шине, шестые входы ячеек памяти первого столбца матрицы и третьи выходы всех ячеек памяти соединены соответственно с выходами элементов НЕ первой группы и входами элементов НЕ второй группы, выходы которых и седьмые входы ячеек памяти подключены к шине синхронизации, четвертые и пятые выходы ячеек памяти каждой строки, кроме ячеек памяти последнего столбца матрицы, подключены соответственно к шестым и пятым входам последующей строки ячеек памяти, третьи выходы ячеек памяти, выходные информационные шины, выходные шины результата поиска и шина синхронизации соединены через соответствующие резисторы с источником питания. 2.Матрица по п.1, отличающаяся тем, что каждая ячейка памяти содержит элемент памяти, элементы ИЛИ-НЕ с rtepBoro по четвертый, первьш и второй элементы НЕ, элемент задержки, элемент И. элемент ИЛИ, элемент И-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем выход первого элемента ИЛИ-НЕ соединен с первым входом элемента памяти и одним из входов второго элемента ИЛИ-НЕ,вы-, ход которого подключен к второму входу элемента памяти, выход которого соединен с одними из входов элемента ИЛИ и элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого подключен к зыходу элемента И, одни из входов ко- торого соединен с выходом элемента задержки, третий вход третьего элемента ИЛИ-НЕ и вход второго элемента НЕ соединены с выходом четвертого элемента ИЛИ-НЕ, выход третьегоэлемента .ИЛИ-НЕ подключен к входу

первого.элемента НЕ и одному, и входов четвертого элемента ИЛИ-НЕ и элемента И-НЕ, выходы элемента ИЛИ, элементов НЕ, четвертого элемента

5 ИЛИ-НЕ и элемента И-НЕ являются выходами матрицы, входами которой являются входы элемента задержки и первого элемента ИЛИ-НЕ, другие входы элемента И-НЕ, элемента И,второ10 го и четвертого элементов ИЛИ-НЕ, элемента РАВНОЗНАЧНОСТЬ, и четвертый вход третьего элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1985 |

|

SU1277211A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Элемент памяти ассоциативной запоминающей матрицы | 1985 |

|

SU1265857A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1316048A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| Ассоциативный запоминающий элемент | 1980 |

|

SU928415A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Элемент ассоциативной матрицы | 1973 |

|

SU478297A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

Изобретение относится к вычислительной технике, в частности к устройствам хранения информации, и может быть использовано в цифровых системах обработки информации. Цель изобретения - расширение функциональных возможностей матрицы за счет обеспечения ассоциативного поиска слова, ближайщего к признаку поиска. Она содержит ячейки памяти, подключенные по строкам к входным шинам выборки слов и вькодным шинам результата поиска, а по столбцам - к маскирующим шинам, входным и выходным информациoHHbw шинам, две группы элементов НЕ и элементы развязки. Матрица может работать в следующих режимах: адресной записи, адресного считывания, ассоциативного поиска строки матрицы, совпадающей своими незамаскированными, разрядами с признаком опро(Л са, ассоциативного поиска строки матрицы, ближайшей по Хзммингу к незамаскированным разрядам признака опроса. 1 з.п. ф-лы, 2 ил.

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-07—Публикация

1985-03-01—Подача