(54) .I Изобретение относится к электросвязи и может использоваться для оценки качес ва канала по информации сигналам. Известно устройство для оценки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления и посйецовательно соединенные счетчик ошибок, мультиплексор обратный функциональный преобразователь, цемультиплексор, первый блок памяти и сумматор, второй вход которого через второй блок памяти соединен с вторым выходом демультиплексора,а также блок индикации, блок сравнения и блок упра&ления, соответствующие вь1ходы которого подключены к управляющим входам мультиплексора, демультиплексора, первого и второго блоков памяти и первого и второго элементов И, причем на первый вход блока управления подан сигнал тактовой частоты, а на его второй вход, обьеовнеяный с управляющим входом счетчика ошибок, подан сигнал пуска Ij. УСТРОЙСТВО ДЛЯ ОПЕНКИ ДОСТОВЕРНОСТИ ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ Однако такое устройство отличается сложностью, возрастающей с увеличением степени полйнбМй, аппроксимирующего зависимость аргумента сложной функции от соотношения сигнал/шум. Цель, йаобретения-упрощение устройства путем исключения блоков формирования аппроксимирующего полинома без снижения точности оценки. Это достигается тем, что в известное устройство для оценки достоверности приема дискретных сигналов введены формирователь весового коэффициента, блок вычитания, формирователь порогов дискриминации сигналов, переключатель и дополнительный сумматор , при этом выход блока автоматической регулировки усиления через последовательно соединенн 11е формирователь весового коэффициента, блок вычитания, второй вход которого соединен с выходом формирователя порогов ШСКриК внации сигналов, второй элемент И, переключатель и дополнительный сумM&fop, подключен к второму входу мупьти

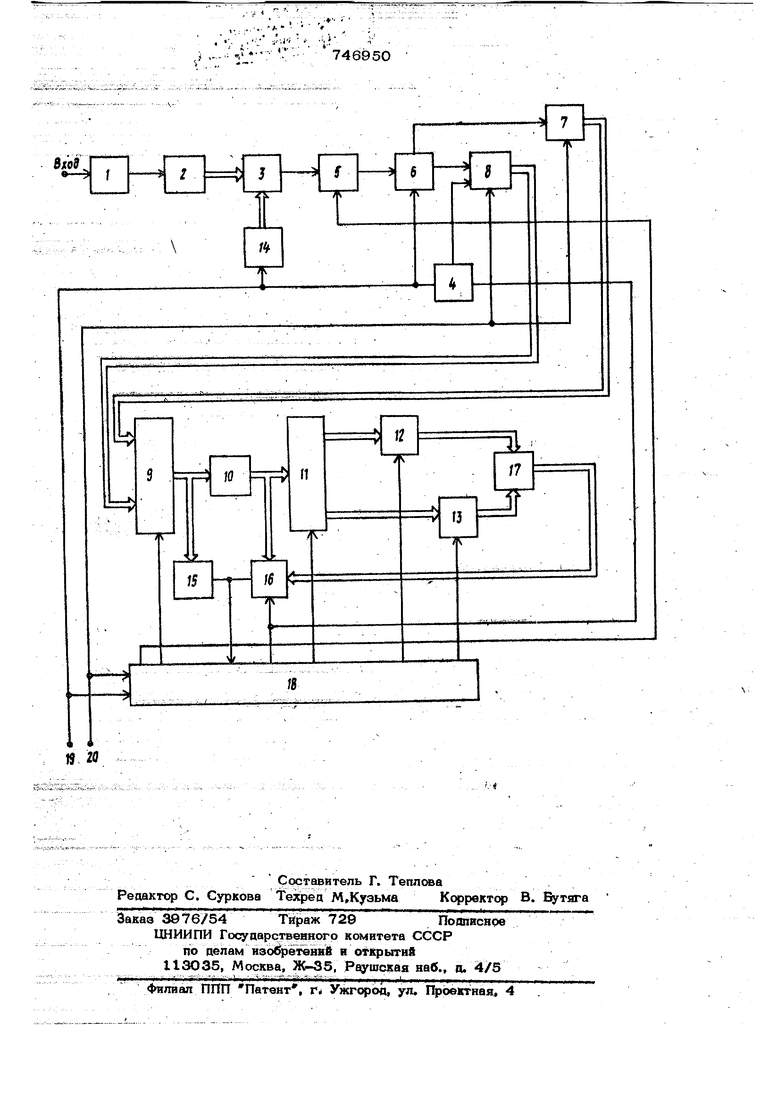

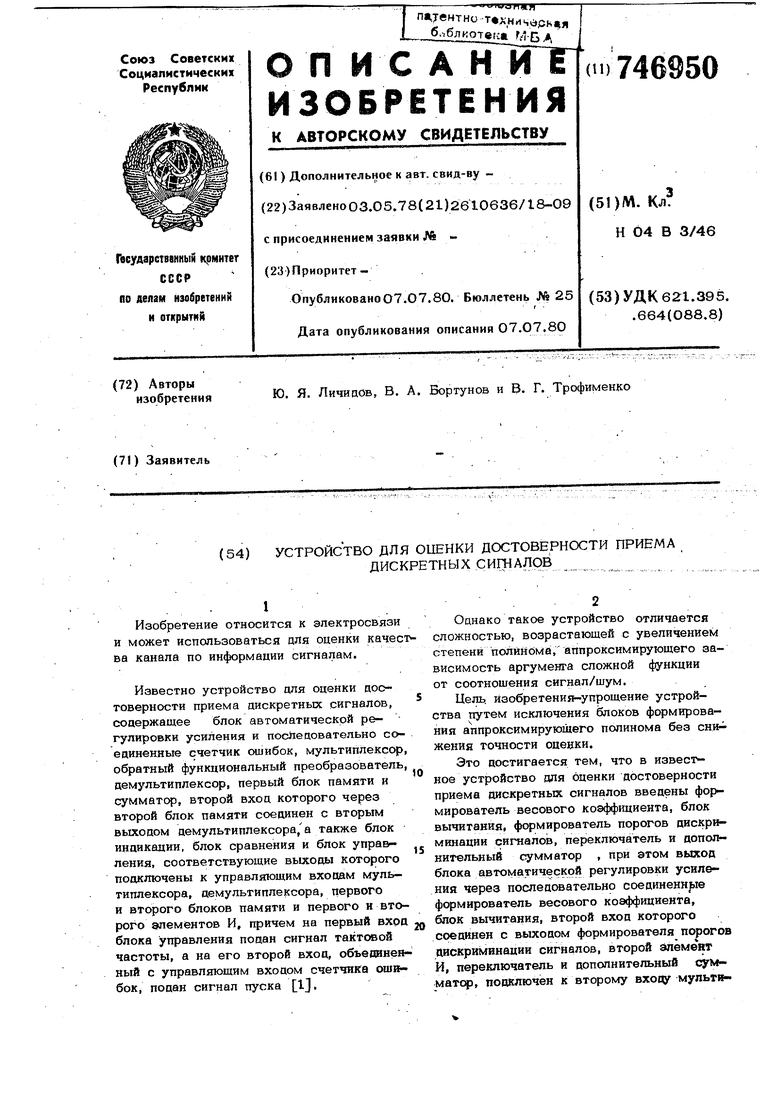

MbridiiiWi - --.- ------- -37469504лексора, выход которого поокпгочен к . Таким образом, сформированный сигвому входу блока индикации, второй входнал, пропорциональный весовому коэффикоторого соединен с третьим вхо циенту посылки, сравнивается в блоке 3 дом блока управления и выходом бло-вычитания с двумя сигналами, пропорциока сравнения, первый , второй и тре- .нальными двум порогам дискриминации тий входы которого соединены соот-сигнала, которые хранятся в формировате ветственно с выходом обратного функцио-ле 14. При этом .если первый порог диснальнрго преобразователя, выходом сумма-дискриминации принимается равным нёкотора и управляющим входом первого эле торой величине сГ , то второй порог дисмента И, выход которого подключен кюкриминации принимается .равным сГ (2-сГ второму входу дополнительного суммато-Бели какой-либо порог дискрйминара, третий вход которого объединен . сции превышает величину весового коэффивторым входом блока управления, первыйциента посылки, то блок 3 вычитания фовход которого объединен с тактовыми вхо-формирует сигнал ошибки, который через дами формирователя порогов дискримина- 15элемент И 5 и переключатель б постуций сигналов, первого элемента И и пере-пает либо на счетный вход счетчика 7, кпючателя, выход которого подключен к либона первый вход сумматора 8. Счет сигнальному входу счетчика .ошибок,.ошибок проводатся на всем объеНа чертеже .привёдёна стру1кгу1р ая алек- .ме выборки, задаваемом блоком 18 управ трическая схема предлагаемого устрой- 20ления. Когда объем выборки будет исчерпан, ства.блок 18 управления запрещает прохождеУстройство для оценки достоверностиние сигналов чбрез элемент И 5. В наприема дискретных сигналов содержитчальныймоКлент после окончания счета блок I автоматической регулировки уси-ошибок на вход обратного функциональ ления (АРУ), формирователь 2 весового 25ного преобразователя 10 поступает через коэффициента, блок 3 вычитания,мультиплексор 9 значение функции, сфорпервый и второй элементы И 4 и 5, пере-мированнсэе на счетчике 7. По этому.знаключатель 6, счетчик 7 ошибок, сумматорчению функции на выходе обратного функ8, мультиплексор 9, обратный .функцио-ционального преобразователя 10 форминальный преобразователь 10, демульти- 30руется значение аргумента, которое запоплексор 11, первый и второй блоки 12к инается в первом блоке 12 памяти. и 13 памяти, формирователь 14 пороговИмпульс, разреша1ощи й запись в блок 12 дискриминации сигналов, блок 15 инди-памяти, форм1фуется блоком 18 управлекации, блок 16 сравнения, сумматор 17,ния. После этого мультиплексор 9 по сигблок 18 управления, на первый вход 19 35налу с блока 18 управления переключаеткоторого подан сигнал тактовой частоты,ся в другое состо5шие, в котором на вход а наего второй вход 2О, объединенный собратного функционального преобразоватеуправляющим входом счетчика 7, поданля 10 коммутируется сигнал, хранимый в сигнал пуска. Вход блока 1 АРУ являет™сумматоре 8. По, этому сигналу обратный ся входом устройства. 40функциональный преобразователь 10 фqp Устройство работает следующим записывается по разрешающему сигнаразом. лу с блока 18 управления на второй блок Сигналом Пуск счетчик 7 ошибок,13 памяти. Сигналы; хранимые в блоках сумматор 8 и блок 18 управления, уста- 4512 и 13 памяти, суммируются в сумматонавливаются в исходное состояние. На-.pg 7, после чего сумма поступает на чиная с этого момента, блок 18 управ-блок 16 сравнения, ления разрешает прскождение сигналов ,... через элемент И 5. Входной сигнал посту-После этого по сигналу с блока 18 уппает на блок 1 АРУ, который стандар- 50Управления разрешается прохождение имтизует его по уровню. По этому стан дар-пульсов через элемент И 4 на второй тизированному сигналу формирователь 2,вход сумматора ё, которые последовательиспользуя тактовую частоту, вырабаты-«о уменьшают значение числа, сранимоваег на опине каждой посылки сигнал,го в нем. В соответствии . с этим изме ееличина которого пропорциональна либо jняется значение aprj мента на выходе обплошади посылки при интегральном приеме,ратного фун1сдионального преобразователя либо амплитуде сигнала при приеме . Этот процесс продолжается до тех тодрм короткого контакта. На выходе фор-.пор, пока не сравняется значение аргумирбвйтеля 2 имеется положительный сиг-Ментов на аькоде сумматора 17 и обратмирует вторре значение аргумента, котоного функционального преобразователя 10 При сравнении значений аргументов на вы блока 16 сравнения появляется сигнал, который разрешает запись значения функции на блок 15 индикации, и поступая на блок 18 управления, устанавливает устройство в .исходное состояние. Зафиксированное на блоке 15 индикации число и является оценкой достоверности приема дискретных сигналов, характеризуемой частотностью по5шления ошибок. Предлагаемое устройство позволяет значительно сократить габариты, повысить надежность и увеличить степень оценки достоверности приема дискретных сигналов по сравнению с известным. Формула изобретения Устройство для оденки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления и последовательно соединенные счетчяк ошибок, мультиплексор, обратный с|унк циональный преобразователь, демультиплексор, первый блок памяти и сумматор, второй вход которого через второй блок памяти соединен с вторым выходом демул типлексфа, а также блок индикации, блок .сравнения и блок управления, соответствующие выходы которого подключены к управляющим входам мультиплексора, демультиплексора, первого и второго блоков памяти и первого и второго элемен.тов И, причем на первый вход блока упра ления подан сигнал тактовой частоты, а на его второй вход, объединенный с управляющим входом счетчика ошибок, подан сигнал пуска, отличающееся тем, что, с целью упрощения устройства IjiyTeM исключения блоков формирования аппроксимирующего полинома без снижения точности оценки, введены формирователь весового коэффициента, блок вычита- ния, формирователь порогов дискриминации сигналов, переключатель и дополнительный сумматор, при этом выход блока автоматической регулировки усиления через последовательно соединенные формирователь весового коэффициента, блок вычитания, второй вход которого соединен с выходом формирователя порогов дискриминации сигналов, второй элемент И, переключатель и дополнительный сумматор подключен к второму входу- мультиплексора, йыход которого подключен R первому входу блока индикации, второй вход которого соединен с третьим входом блока управления и выходом блока сравнения, первый , второй и третий входы которого соединены соответственно с выходом обратного функционального преобразователя, выходом сумматора и управляющим. входом первого элемента И, выход которого подключен к второму входу дополни- тельного сумматора, третий вход которого объединен с вторым входом блока управления, первый вход которого объединен с тактовыми входами формирователя порогов диск риминации сигналов, первого элемента И и переключателя, выход которого подключен к сигнальному входу счетчика ошибок. Источники информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР по заявке N 2426910/18-09, кл. Н 04 В 3/46, 07.12.76.

/V .

Г.Г. vr-v:.

i ,... i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки достоверности приема дискретных сигналов | 1976 |

|

SU657629A1 |

| Многоканальная адаптивная цифровая система связи | 1984 |

|

SU1220133A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Многоканальное устройство для измерения температуры | 1989 |

|

SU1672239A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 2002 |

|

RU2217769C1 |

| СПОСОБ ПРИЕМА МНОГОЛУЧЕВОГО СИГНАЛА, СПОСОБ ПОИСКА И СПОСОБ ФОРМИРОВАНИЯ МЯГКИХ РЕШЕНИЙ ПРИ ПРИЕМЕ МНОГОЛУЧЕВОГО СИГНАЛА И УСТРОЙСТВА, ИХ РЕАЛИЗУЮЩИЕ | 2003 |

|

RU2251802C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| ПИРОМЕТР ИЗЛУЧЕНИЯ | 1993 |

|

RU2113696C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

Авторы

Даты

1980-07-23—Публикация

1978-05-03—Подача