(54) ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ИДЕНТИФИКАЦИИ ОБЪЕКТОВ | 2003 |

|

RU2276796C2 |

| УСТРОЙСТВО ПЕРЕДАЧИ СИГНАЛОВ УПРАВЛЕНИЯ И КОНТРОЛЯ В ЛОКАЛЬНЫХ СЕТЯХ ТЕХНОЛОГИЧЕСКОЙ СВЯЗИ | 1996 |

|

RU2120188C1 |

| Устройство для отображения гра-фичЕСКОй иНфОРМАции HA эКРАНЕэлЕКТРОННО-лучЕВОй ТРубКи | 1978 |

|

SU805402A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1030989A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| РАДИОЛОКАЦИОННОЕ ПРИЕМНОЕ УСТРОЙСТВО | 1984 |

|

SU1841013A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

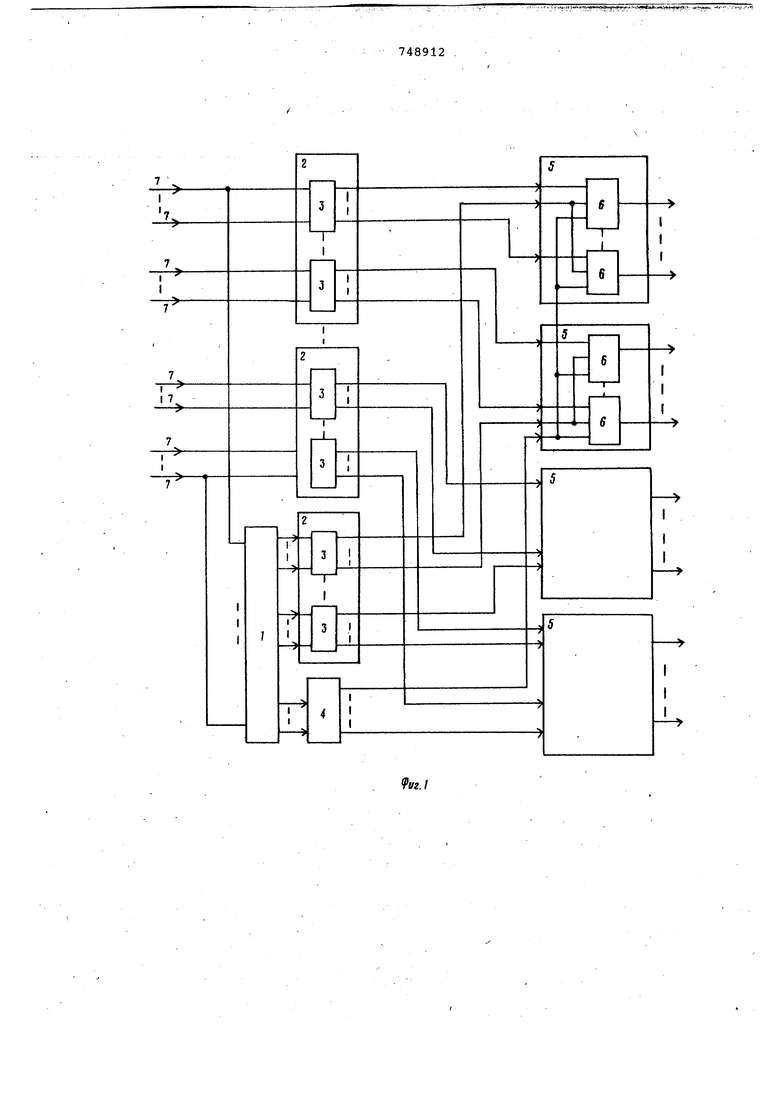

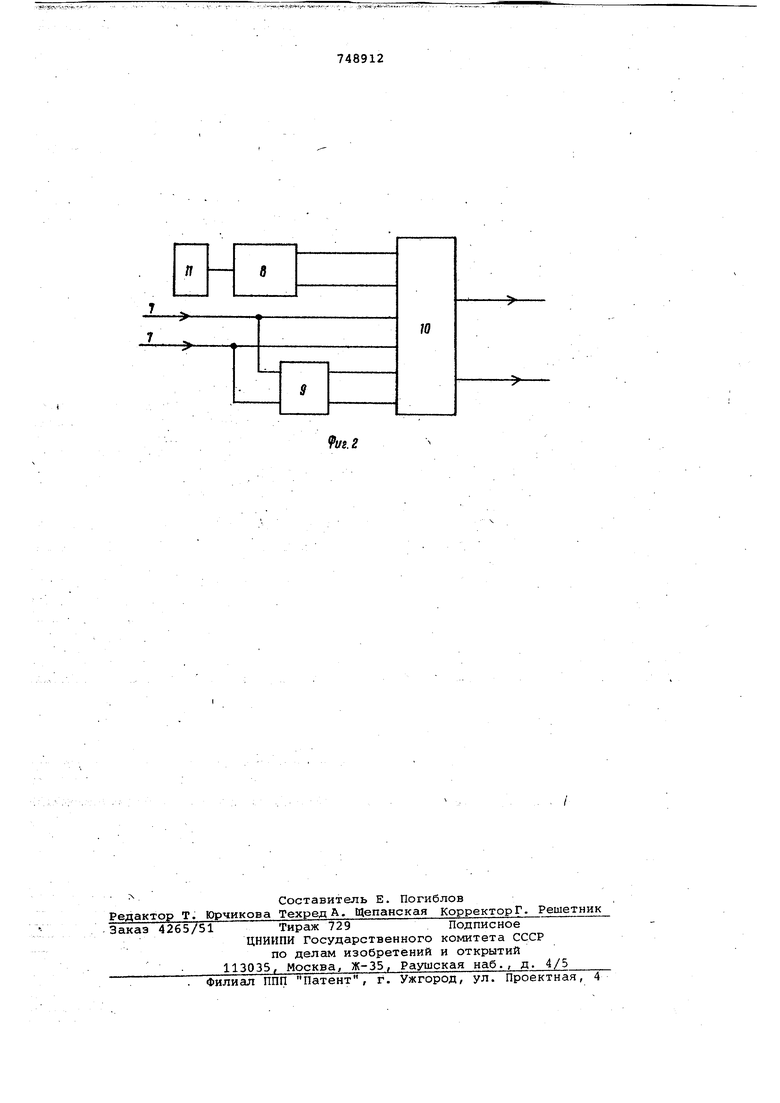

ИзоЗретение относится к телеграфии. Устройство может использоваться в блоках концентрации коммутаторов электронно-телеграфной станции. Известно избирательное устройство содержащее логические блоки, входы которых соединены с выходами соответствуклцих блоков коммутации, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами бло ков коммутации, причем входы соответствующих селекторов сигналов подключены к линиям связи 1 . Однако известное устройство имеет низкое быстродействие. Цель изобретения - повышение быст родействия. Для этого в избирательное устройство, содержащее логические блоки, входы которых соединены с выходами соответствующих блоков коммутации, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами блоков коммутации, причем вхо ды соответствунндих селекторов сигналов подключены к линиям связи, вве дены блок управления и сумматор, при .чем выходы сумматора соединены с вхр дами одного из блоков коммутации и блока управления, выходы которого под ключены к дополнительным входам соот- ветствующих логических блоков, авходы сумматора соединены с линиями свя-зи. Селектор сигналов содержит инвертор, формирователь сигналов, регистр сдвига и генератор, выходом подключенный к входу регистра сдвига, выходы которого соединены с одними входами формирователя сигналов, другие входы которого соединены соответственно с входами и выходами инвертора, при этом входы инвертора и выходы формирователя сигналов являются соответственно входами и выходами селектора сигналов. Логический блок содержит элементы И, соответствующие входы которых объединены, а входы и выходы элементов И являются соответственно входами и выходами логического блока. На фиг. 1 изображена структурная электрическая блок-схема предложенного устройства} на фиг. 2 показан вариант выполнения селектора сигналов. Устройство содержит сумматор 1, блоки 2 коммутации, каждый из которых содержит селекторы 3 сигналов, блок 4 управления, логические блоки 5, каждый из которых содержит элементы И 6, и линии связи 7. Селектор сигналов (фиг. 2) содер,жит регистр 8 сдвига, инвертор 9, фо рователь 10 сигналов и генератор . 1 Устройство работает следующим образом. При поступлении на линии связи 7 сигналов, последовательность поступления которых случайная, селекторы 3 сигналов выбирают на обслуживание од ну из обслуживаемых линий связи 7, Включенных в ксокдый селектор 3 обслуживания требований. Одновременно сигналы требований поступают, на входы сумматора 1. В результате сложения возбуждаются информационные выходы сумматора причем каждый из них соответствует сумме входов одного селектора 3 сигналов. Информационные входы включены в блок 2 коммутации, который выполняет функцию блока подготовки выбора. Каждый выход этого блока соединен с вторыми входами элементов И б соответствующего селектора сигналов. Выходы блока 2, вы полняющего функции блока подготовки выбора, подготавливают срабатывание определенных элементов И. Одйовременнр с появлением сигналов на инфор мационных выходах сумматора 1 в результате сложения входов каждого бло ка 2 сигналы возникают и на выходах посылки регистрации требований сумматора. Выходы посылки регистрации требований соединены с блоком 4 управления. Блок 4 формирует управляющий сигнал, который поступает на оди из управляемых входов логического блока 5. Управляющий сигнал по управляемому входу логического блока поступает на входы тех элементов Иб которые включеныв выходы соответствующего блока 2 ко1 &1утации. Совпадение сигналов по всем трем входам в элементе И б вызывает появление сигнала на том выходе лргического бл ка 5, который соответствует выбранно обслуж яваеьюй линии связи 7. Селектор сигналов запускается при появлении на одном или нескольких обслужив аемых линиях связи сигнала требования. Сигналы требования поступают на втррую группу входов формирователя ДО сигналов Обслуживании. Сигналы требования поступают также н входы инвертора 9 и после прохождения через него поступают на третью группу входов формирователя 10 сигналов обслуживания. На первую групп

748912 входов формирователя 10 сигналов обслуживания поступают сигналы от ге- нератора 11,преобразованные регистром 8 сдвига в параллельный код. Формирователь. 10 сигнала обслуживания формирует сигнал обслуживания на том выходе селектора 3 сигнгшов, на вход которого поступили сигнал требования и управляющий сигнал с выходив регистра 8 сдвига. J. Предложенное устройство по срав{Нению с известным имеет более высокре быстродействие за счет уменьшения количества ступеней, состоящих из блоков коммутации. Формула изобретения 1.Избирательное устройство, содержащее логические блоки, входы которых соединены с выходами соответствующих блоков коммутаций, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами блоков коммутации, причем входы соответствующих селекторов сигнашов подключены к линиям связи, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок управления и сумматрр, выходы которог;о сое«. динены с входами одного из блоков ком мутации и блока управления, выходы которого подключены к дополнительным входам соответствующих логических блоков, а входы сумматора соединены с линиями связи. 2.Устройство по п. 1, о т л и ч а ю щ е ее я тем, что селектор сигна,лов содержит инвертор, формирователь сигналов, регистр сдвига и генератор выход которого подключен к входу регистра сдвига, выходы которого соединены с одними входами формирователя сигнсшов, другие входы которого соединены соответственно с входами и выходами инв.ертора, при этом вхог,ы инвертора и выходы формирователя сигналов являются соответственно входами и выходами селектора сигналов. 3, Устройство по п. 1, отличающееся тем, что логический блок содержит элементы И, соответствующие входы которых объединены , а входы и выходы элементов И являются соответственно входами и выходами логического блока. Источники информации, принятые во внимание при экспертизе 1. Патент ФРГ № 1277935, кл. 21 а 30/01, 1969 (прототип).

Авторы

Даты

1980-07-15—Публикация

1978-04-07—Подача