00

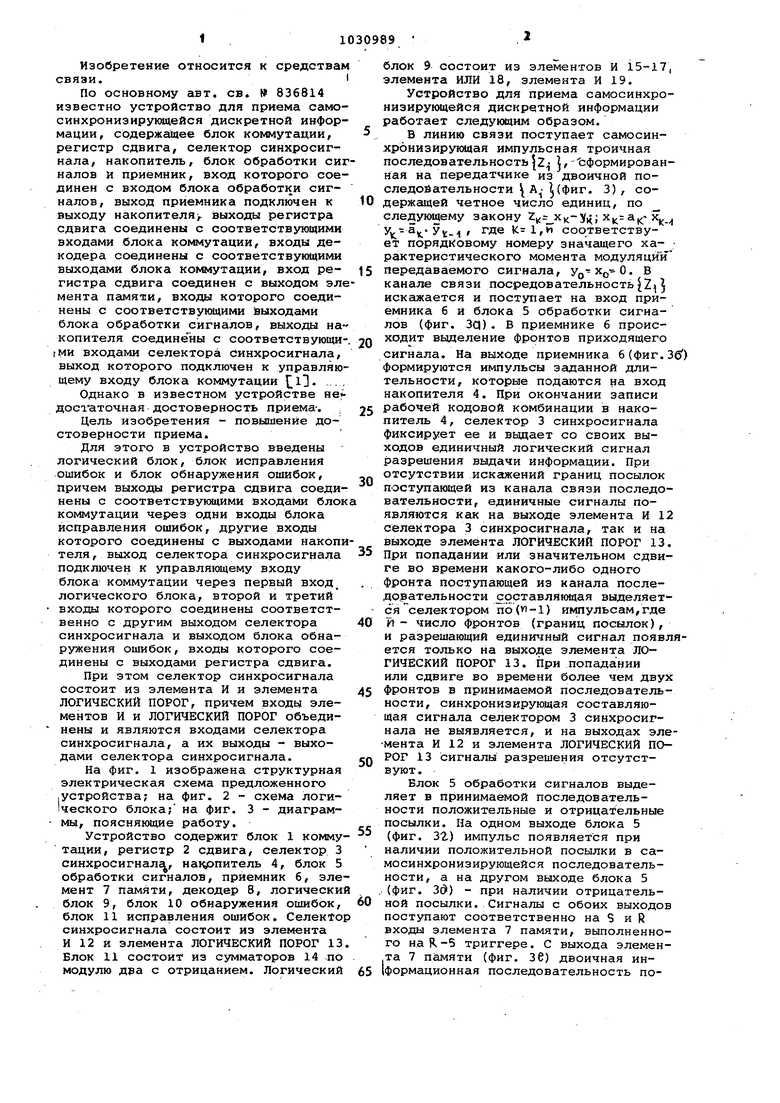

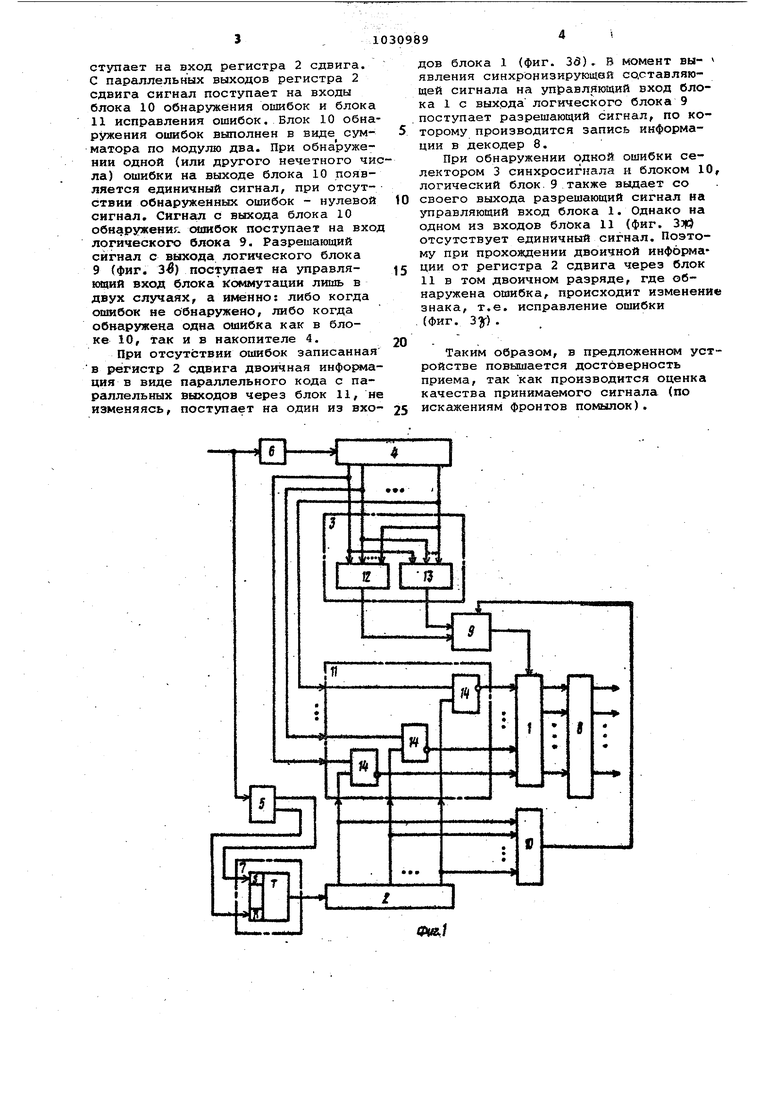

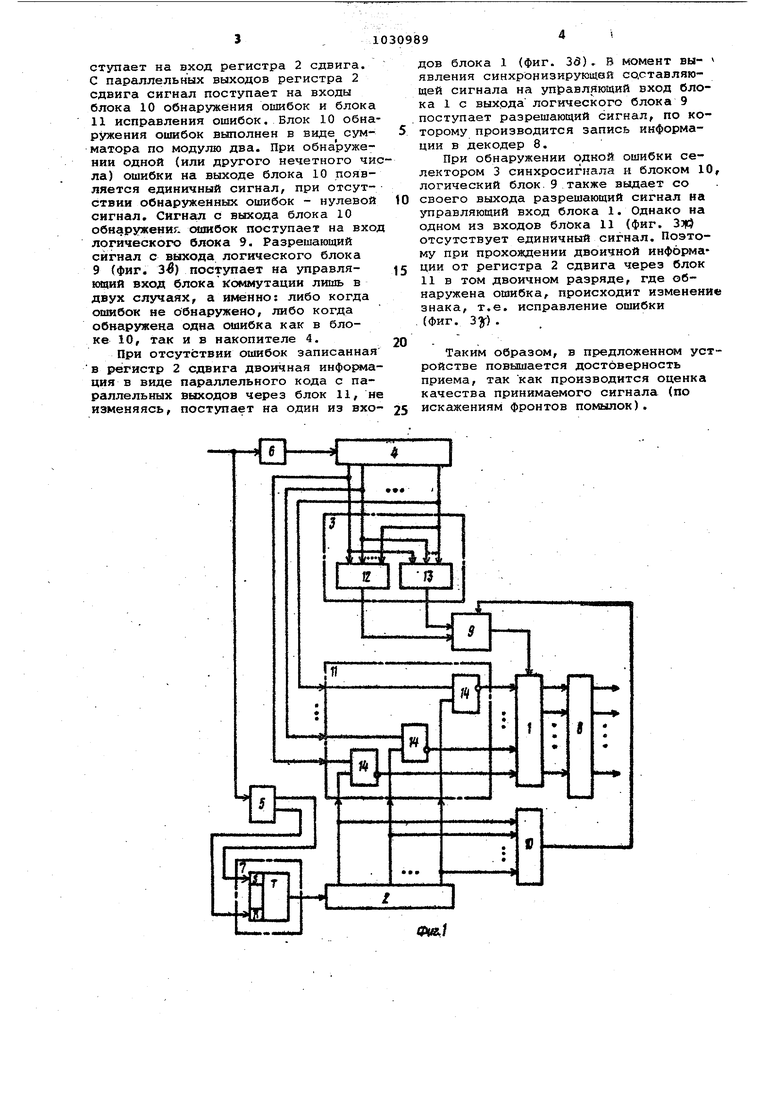

со Изобретение относится к средствам связи. По основному авт. св. ( 836814 известно устройство для приема самосинхрониэирующейся дискретной информации, содержащее блок коммутации, регистр сдвига, селектор синхросигнала, накопитель, блок обработки сиг налов и приемник, вход которого соединен с входом блока обработки сигналов, выход приемника подключен к выходу накопителя выходы регистра сдвига соединены с соответствующими входами блока коммутации, входы декодера соединены с соответствующими выходами блока кокмутации, вход регистра сдвига соединен с выходом эле мента памяти, входы которого соединены с соответствукнцими выходами блока обработки сигналов, выходы на копителя соединенны с соответствующи (МИ входами селектора синхросигнала, выход которого подключен к управляю щему входу блока коммутации l3. Однако в известном устройстве не достаточная достоверность приема-. , Цель изобретения - повышение достоверности приема. Для этого в устройство введены логический блок, блок исправления ошибок и блок обнаружения ошибок, причем выходы регистра сдвига соединены с соответствукицими входами блок коммутации через одни входы блока исправления ошибок, другие входы которого соединены с выходами накопи теля, выход селектора синхросигнала подключен к управляющему входу блока коммутации через первый вход, логического блока, второй и третий входы которого соединены соответственно с другим выходом селектора синхросигнала и выходом блока обнаружения ошибок, входы которого соединены с выходами регистра сдвига. При этом селектор синхросигнала состоит из элемента И и элемента ЛОГИЧЕСКИЙ ПОРОГ, причем входы элементов И и ЛОГИЧЕСКИЙ ПОРОГ объединены и являются входами селектора синхросигнала, а их выходы - выходами селектора синхросигнала. На фиг. 1 изображена структурная электрическая схема предложенного .устройства; на фиг. 2 - схема логического блока; на фиг. 3 - диаграммы, поясняющие работу. Устройство содержит блок 1 комму тации, регистр 2 сдвига, селектор 3 синхросигналу, накрпитель 4, блок 5 обработки сигналов, приемник б, эле мент 7 памяти, декодер 8, логически блок 9, блок 10 обнаружения ошибок, блок 11 исправления ошибок. Селекто синхросигнала состоит из элемента И 12 и элемента ЛОГИЧЕСКИЙ ПОРОГ 13 Блок 11 состоит из сумматоров 14 по модулю два с отрицанием. Логический блок 9 состоит из элементов И 15-17, элемента ИЛИ 18, элемента И 19. Устройство для приема самосинхронизирукяцейся дискретной информации работает следукяцим образом. В линию связи поступает самосинхрбнизируквдая импульсная троичная последовательность |2 I, сформированная на передатчике из двоичной последовательности (фиг. 3), содержащей четное число единиц, по следующему закону Xj, a,- . у, где ,й соответствует порядковому номеру значащего характеристического момента модуляцией передаваемого сигнала, . В канале связи посредовательность 2;) искажается и поступает на вход приемника б И блока 5 обработки сигналов (фиг. 30). В приемнике 6 происходит выделение фронтов приходящего сигнала. На выходе приемника 6 (фиг. 36) формируются импульсы заданной длительности, которые подаются на вход накопителя 4. При окончании записи рабочей кодовой комбинации в накопитель 4, селектор 3 синхросигнала фиксирует ее и вьщает со своих выходов единичный логический сигнал разрешения выдачи информации. При отсутствии искгокений границ посылок поступающей из канала связи последовательности, единичные сигналы появляются как на выходе элемента И 12 селектора 3 синхросигнала, так и на выходе элемента ЛОГИЧЕСКИЙ ПОРОГ 13. При попадании или значительном сдвиге во времени какого-либо одного фронта поступающей из канала последо:вательности составляницая выделяется селектором по (11-1) импульсам,где И - число фронтов (границ посылок), и разрешающий единичный сигнал появляется только на выходе элемента ЛОГИЧЕСКИЙ ПОРОГ 13. При попадании или сдвиге во времени более чем двух фронтов в принимаемой последовательности, синхронизирующая составляющая сигнала селектором 3 синхросигнала не выявляется, и на выходах элемента И 12 и элемента ЛОГИЧЕСКИЙ ПОРОГ 13 сигналы разрешения отсутствуют. Блок 5 обработки сигналов выделяет в принимаемой последовательности положительные и отрицательные посылки. На одном выходе блока 5 (фиг. 32.) импульс появляется при наличии положительной посылки в самосинхронизирующейся последовательности, а на другом выходе блока 5 . (фиг. 3() - при наличии отрицательной посылки. Сигналы с обоих выходов поступают соответственно на S и R входы элемента 7 памяти, выполненного наЯ-5 триггере. С выхода элемента 7 памяти (фиг. 36) двоичная информационная последовательность поступает на вход регистра 2 сдвига. С параллельных выходов регистра 2 сдвига сигнал поступает на входы блока 10 обнаружения ошибок и блока 11 исправления ошибок. Блок 10 обнаружения ошибок вьшолнен в виде сумматора по модулю два. При обнаружении одной (или другого нечетного числа) ошибки на выходе блока 10 появляется единичный сигнал, при отсутствии обнаруженных ошибок - нулевой сигнал. Сигнал с выхода блока 10 обнаружениг. ошибок поступает на вход логического блока 9. Разрешающий сигнал с выхода логического блока 9 (фиг. Зб) поступает на управлякяций вход блока коммутации лишь в двух случаях, а именно: либо когда ошибок не обнаружено, либо когда обнаружена одна ошибка как в блоке 10, так и в накопителе 4.

При отсутствии ошибок записанная в регистр 2 сдвига двоичная информация в виде параллельного кода с параллельных выходов через блок 11, не изменяясь, поступает на один из входов блока 1 (фиг. 3d), В момент выявления синхронизирующей составляющей сигнала на управляющий вход блока 1 с выхода логического блока 9 поступает разрешающий сигнал, по которому производится запись информации в декодер 8.

При обнаружении одной ошибки селектором 3 синхросигнала и блоком 10 логический блок. 9 также выдает со своего выхода разрешающий сигнал на управляющий вход блока 1. Однако на одном из входов блока 11 (фиг, Зж) отсутствует единичный сигнал. Поэтому при прохождении двоичной информации от регистра 2 сдвига через блок 11 в том двоичном разряде, где обнаружена ошибка, происходит изменени знака, т.е. исправление ошибки . (фиг. Зу) .

Таким образом, в предложенном устройстве повышается достоверность приема, так как производится оценка качества принимаемого сигнала (по искажениям фронтов помылок).

1 t t I О I О i 1 Т Q i g ГТ1

Фш.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема самосинхронизирующейся дискретной информации | 1984 |

|

SU1228296A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1080252A2 |

| Устройство для приема самосинхронизирую-щЕйСя диСКРЕТНОй иНфОРМАции | 1979 |

|

SU836814A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1980 |

|

SU924902A2 |

| Устройство для передачи и приема дескретных сообщений | 1990 |

|

SU1786669A1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Устройство приема сигналов синхронного запуска | 1973 |

|

SU543183A1 |

| Устройство выделения рекуррентного синхросигнала с исправлением ошибок | 1976 |

|

SU582578A1 |

1. УСТРОЙСТВО ДЛЯ ПРИЕМА САМОСИНХРОНИЗЙРУЮЙЩЙСЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО авт. св. 836814, о тл и ч а ю щ е е с я тем, что, с целью повышения достоверности приема, в него введены логический блок, блок исправления ошибок и блок обнаружения ошибок, причем выходы регистра сдвига соединены с соответствую- (цими входами блока коммутации через одни вход блока исправления ошибок, другие входы которого соединены с выходами накопителя выход селек- .тора синхросигнала подключен ,к управляющему входу блока коммутации через первый вход логического блока, в;горой и третий входы которого соединены соответственно с другим выходом селектора синхросигнала и выходом, блока обнаружения о(аибок, входы которого соединены с выходами регистра сдвига. 2. Устройство по п. 1, о т л и ч а ю щ ее с я тем, что селектор Иг синхросигнала состоит из элемента orW и элемента ЛОГИЧЕСКИЙ ПОРОГ, причем входы элементов И и ЛОГИЧЕСКИЙ ПОРОГ к-|С объединены и являются входами селектора синхросигнала, а их выходы выходами селектора синхросигнала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Телеобъектив-апохромат | 1979 |

|

SU836614A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-07-23—Публикация

1982-04-07—Подача