Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных (сети ПД) автоматизированной системы управления (АСУ) при управлении передачей данных по широковещательному многоточечному радиоканалу, имеющему динамическую неполносвязную структуру.

Известно устройство для управления передачей данных по радиоканалу (Авт. св. СССР N 1162058, кл. H 04 L 7/00, 1985), содержащее последовательно соединенные синхронизатор и первый элемент И, а также элемент задержки, элемент ИЛИ и последовательно соединенные счетчик и триггер цикла передачи, последовательно соединенные генератор случайных чисел, блок сравнения и триггер разрешения передачи, а также последовательно соединенные второй элемент И и формирователь импульсов, что позволяет увеличить степень использования пропускной способности канала. Однако, данное устройство обладает недостаточной скоростью передачи по радиоканалу.

Наиболее близким по технической сущности и выполняемым функциям к заявляемому является устройство для управления передачей данных по радиоканалу (Авт. св. СССР N 1319298, кл. H 04 L 7/00, опубл. 23.06.87), содержащее генератор случайных чисел и синхронизатор, первый, второй, третий и четвертый элементы И, счетчик, блок сравнения, триггер цикла передачи, триггер разрешения передачи, два формирователя импульсов, элемент ИЛИ, два элемента задержки, причем выход синхронизатора связан с первым входом первого элемента И и вторым входом второго элемента И, вход запроса передачи является третьим входом второго элемента И и связан с первым входом триггера разрешения передачи, выход которого связан с вторым входом элемента ИЛИ, входом элемента задержки и является выходом разрешения передачи, выход элемента задержки подключен к четвертому входу первого элемента И, третий вход которого связан с выходом триггера цикла передачи и первым входом второго элемента И, выход второго элемента И связан с входом формирователя импульсов и входом генератора случайных чисел, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к первому выходу счетчика, выход формирователя импульсов связан с первым входом элемента ИЛИ, второй выход счетчика соединен с вторым входом триггера цикла передачи, а вход счетчика подключен к выходу первого элемента И, выход блока сравнения подключен к входу дополнительного элемента задержки и третьему входу элемента ИЛИ, а выход элемента ИЛИ является выходом "Включение передатчика", выход дополнительного элемента задержки связан с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И соединен с выходом четвертого элемента и является выходом сигнала "Столкновение", причем выход третьего элемента И связан с вторым входом триггера разрешения передачи, а второй вход четвертого элемента И подключен к второму входу первого элемента И и первому входу триггера цикла передачи и является входом "Сигнал несущей".

При такой совокупности описанных элементов и связей достигается увеличение пропускной способности по радиоканалу.

Однако устройство-прототип имеет недостатки:

- узкую область применения, в частности оно может использоваться в каналах множественного доступа с временным разделением сигналов и не предназначено для работы в каналах множественного доступа с кодовым разделением;

- имеет невысокую пропускную способность, что обусловлено отсутствием адаптации схемы прототипа к изменению параметров нагрузки.

Целью изобретения является разработка устройства управления передачей данных по радиоканалу множественного доступа с кодовым и временным разделением сигналов, обеспечивающего повышение пропускной способности, за счет адаптации к изменению параметров нагрузки.

Поставленная цель достигается тем, что в известное устройство управления передачей данных по радиоканалу, содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, RS-триггер, второй элемент И, блок сравнения, причем управляющий вход устройства является одновременно сигнальным входом первого элемента И, а выход счетчика соединен с первым сигнальным входом блока сравнения, дополнительно введены кодер, блок преобразования, первый и второй дискретные фильтры Калмана, счетчик обслуженной нагрузки, счетчик необслуженной нагрузки, коррелятор, решающий блок, блок анализа адреса. Причем информационный вход кодера является информационным входом устройства, а его выход является сигнальным выходом устройства. Выход блока преобразования подключен в параллель к сигнальным входам кодера, генератора случайных чисел и счетчика, тактовый вход которого подключен к выходу синхронизатора, второй сигнальный вход блока сравнения подключен к выходу генератора случайных чисел, управляющий вход первого элемента И подключен к выходу второго элемента И, тактовый и управляющий входы которого подключены соответственно к выходу синхронизатора и выходу RS-триггера, S-и R-входы которого подключены соответственно к выходу блока сравнения и выходу первого элемента И, который дополнительно подключен к управляющему входу генератора случайных чисел. Второй и первый информационные выходы решающего блока подключены соответственно к счетчикам необслуженной и обслуженной нагрузки, выходы которых подключены к входам соответственно первого и второго фильтров Калмана, выходы которых подключены к первому и второму входам блока преобразования соответственно. Вход коррелятора является сигнальным входом устройства, а его выход подключен к входу решающего блока, информационно-адресный выход которого подключен к информационно- адресному входу блока анализа адреса, первый и второй управляющие выходы которого являются соответственно первым и вторым информационными выходами устройства, а выход блока сравнения является управляющим выходом устройства. Адресный вход блока анализа адреса является адресным входом устройства.

Перечисленная новая совокупность существенных признаков обеспечивает возможность использования заявленного устройства в каналах с кодовым и временным разделением благодаря введению в нее элементов, позволяющих динамически оценивать параметры нагрузки, а по результатам оценки адаптировать схему устройства.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявляемое устройство поясняется чертежами.

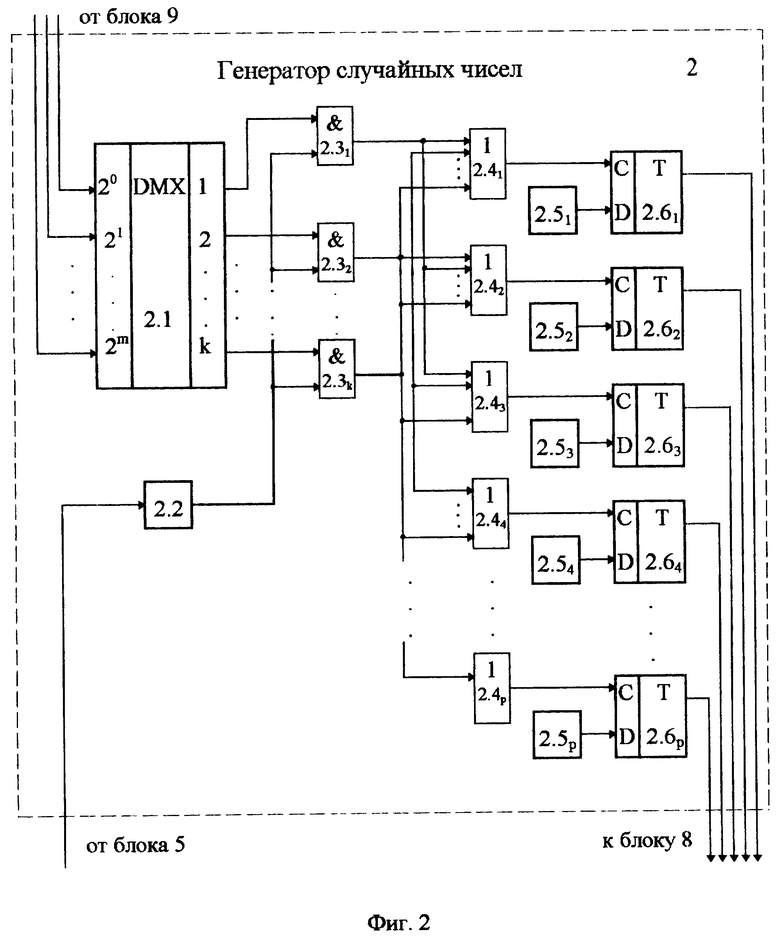

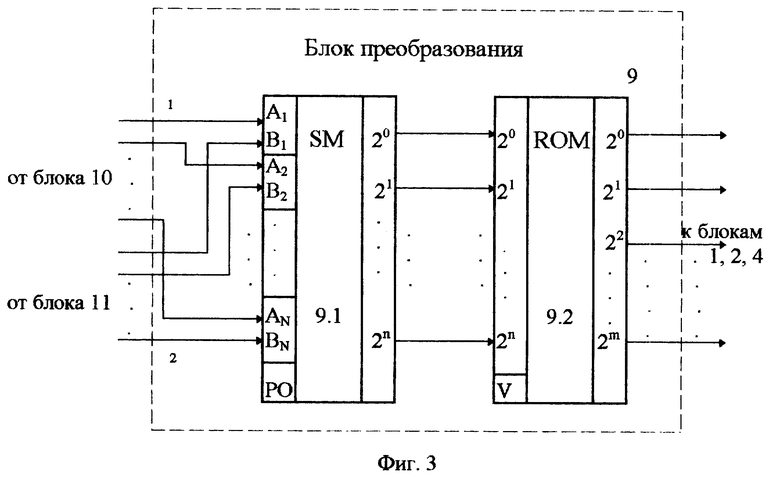

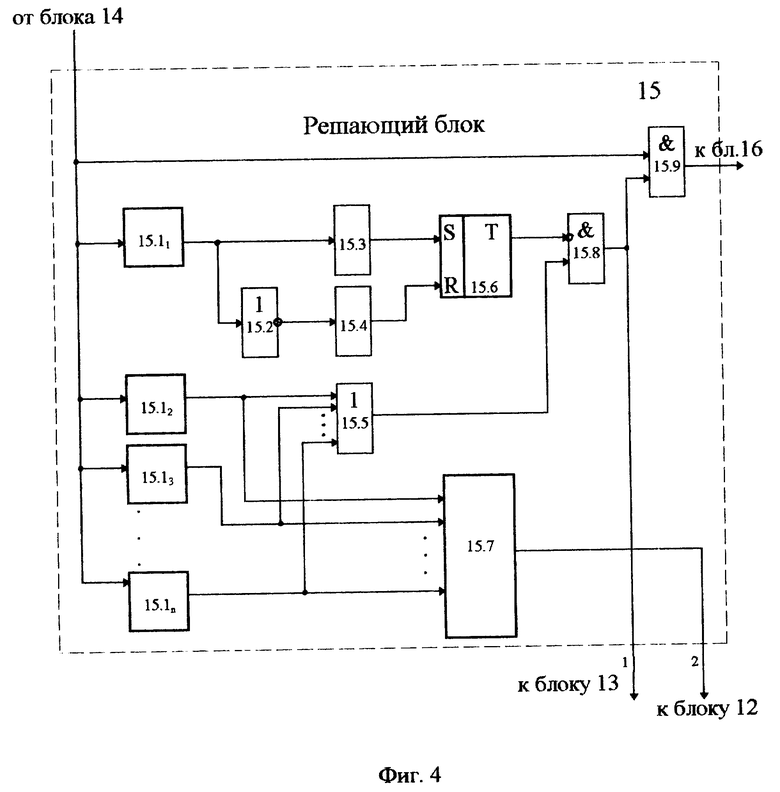

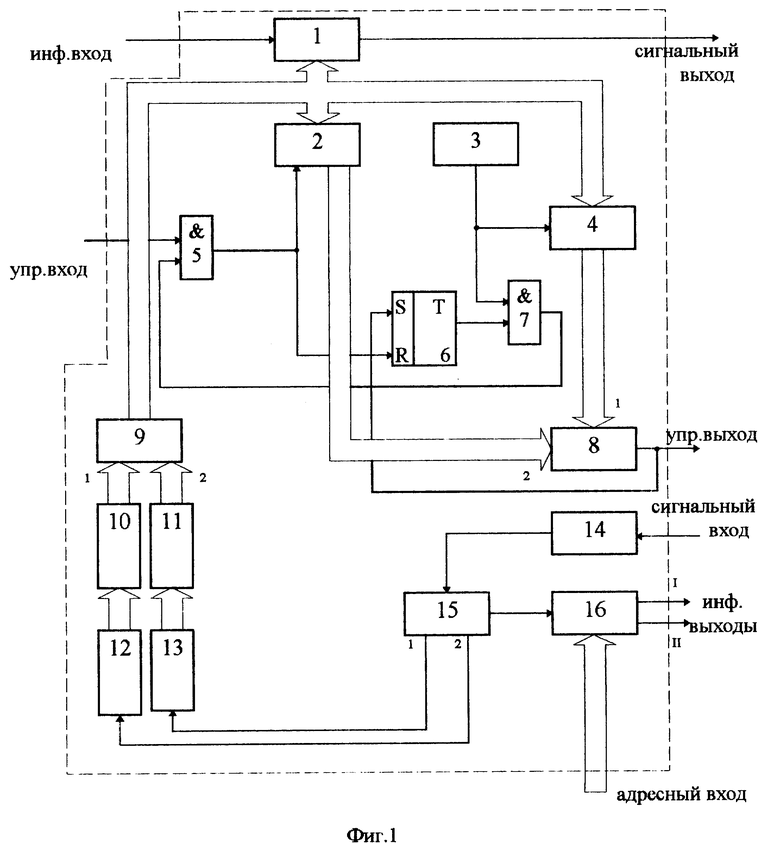

На фиг. 1 показана функциональная схема устройства управления передачей данных по радиоканалу; на фиг. 2 - схема генератора случайных чисел 2; на фиг. 3 - схема блока преобразования 9; на фиг. 4 - схема решающего блока 15; на фиг. 5 - схема блока анализа адреса 16.

Заявляемое устройство управления передачей данных по радиоканалу, показанное на фиг. 1, состоит из кодера 1, генератора случайных чисел 2, синхронизатора 3, счетчика 4, первого элемента И 5, RS-триггера 6, второго элемента И 7, блока сравнения 8, блока преобразования 9, дискретных фильтров Калмана 10 и 11, счетчика необслуженной нагрузки 12, счетчика обслуженной нагрузки 13, коррелятора 14, решающего блока 15, блока анализа адреса 16, причем управляющий вход устройства является одновременно сигнальным входом первого элемента И 5, а выход счетчика 4 соединен с первым сигнальным входом блока сравнения 8, информационный вход кодера 1 является информационным входом устройства, а его выход является сигнальным выходом устройства. Выход блока преобразования 9 подключен в параллель к сигнальным входам кодера 1, генератора случайных чисел 2 и счетчика 4, тактовый вход которого подключен к выходу синхронизатора 3. Второй сигнальный вход блока сравнения 8 подключен к выходу генератора случайных чисел 2, управляющий вход первого элемента И 5 подключен к выходу второго элемента И 7, тактовый и управляющий вход которого подключены соответственно к выходу синхронизатора 3 и выходу RS-триггера 6, S- и R-входы которого подключены соответственно к выходу блока сравнения 8 и выходу первого элемента И 5, который дополнительно подключен к управляющему входу генератора случайных чисел 2. Второй и первый информационные выходы решающего блока 15 подключены соответственно к счетчику необслуженной нагрузки 12 и счетчику обслуженной нагрузки 13, выходы которых подключены к входам соответственно первого фильтра Калмана 10 и второго фильтра Калмана 11, выходы которых подключены к первому и второму входам блока преобразования 9 соответственно. Вход коррелятора 14 является сигнальным входом устройства, а его выход подключен к входу решающего блока 15, информационно-адресный выход которого подключен к информационно-адресному входу блока анализа адреса 16, первый и второй управляющие выходы которого являются соответственно первым и вторым информационными выходами устройства. Выход блока сравнения 8 является управляющим выходом устройства. Адресный вход блока анализа адреса 16 является адресным входом устройства.

Заявляемое устройство реализуется следующим образом.

Кодер 1 предназначен для формирования сложного сигнала с фазовой манипуляцией и описан в работе "Нелинейные радиотехнические устройства", часть 1. (Н.Л.Теплова, - М.: Военное издательство министерства обороны СССР, 1982, - с. 346 - 349). Может быть реализован на ИМС серий 155, 176.

Генератор случайных чисел 2 предназначен для случайного выбора момента начала передачи в цикле передачи с переменной длиной. Может быть реализован по схеме, показанной на фиг. 2. Он состоит из демультиплексора 2.1, формирователя импульсов 2.2, k элементов И 2.3, p элементов ИЛИ 2.4, p генераторов шума 2.5, p D-триггеров 2.6, причем группа входов демультиплексора является сигнальным входом генератора случайных чисел 2, выходы демультиплексора 2.1 соединены с сигнальными входами k элементов И 2.3, управляющие входы которых объединены и соединены с выходом формирователя импульсов 2.2, вход которого является управляющим входом генератора случайных чисел 2. Выходы k элементов И 2.3 соединены с соответствующими входами элементов ИЛИ 2.4, выходы которых соединены с синхровходами D-триггеров 2.6, информационные входы которых соединены с выходами соответствующих генераторов шума 2.5. Выходы D-триггеров 2.6 являются выходом генератора случайных чисел 2.

Демультиплексор 2.1 предназначен для распределения сигналов с одного входа на несколько выходов в последовательности, определенной управляющими воздействиями блока преобразования 9 (Основы импульсной и цифровой техники. /Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - с. 152-156).

Генераторы шума 2.51 oC2.5p предназначены для формирования случайно изменяющихся во времени выходных напряжений (Б.И.Коротков Элементы радиоэлектронных устройств М.: Радио и связь, 1988, - рис. 7.24, с. 107.

D-триггеры 2.61-2.6p описаны в работе "Основы импульсной и цифровой техники"./Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - с. 90 - 91.

Синхронизатор 3 представляет собой генератор тактовых импульсов (Микросхемы и их применение: Справ. пособие. 1984, - с. 213, рис. 7.6.). Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Счетчик 4 описан в Журнале "Радио", 1987, N 1, стр. 43. Может быть реализован на ИМС КА 561 ИЕ 156 (счетчик с переменным коэффициентом деления).

Блок сравнения 8 описан в работе "Импульсные цифровые устройства" (И.О. Лебедев, А. М.Сидоров. - Л.: ВАС, 1980, - с. 51-53, рис. 2.33, 2.34). Может быть реализован на ИМС серий 133, 564.

Блок преобразования 9 предназначен для выработки решения на основе анализа текущего состояния соотношения интенсивностей обслуженного и необслуженного потоков пакетов в канале множественного доступа. Блок преобразования 9 может быть реализован, например, по схеме, показанной на фиг.3, которая включает в себя сумматор 9.1 и постоянное запоминающее устройство (ПЗУ) 9.2, причем первые и вторые входы сумматора 9.1 являются первым и вторым сигнальными входами блока преобразования 9 соответственно, n+1 выходов сумматора 9.1 соединены с n+1 входами ПЗУ 9.2, m+1 выходов которого являются выходом блока преобразования 9.

Сумматор 9.1 предназначен для суммирования кодовых комбинаций, поступающих на фильтр Калмана 10 и 11, и выдачи результата сложения на входы постоянного запоминающего устройства 9.2 (Основы импульсной и цифровой техники. /Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - рис. 5.5, с. 137-139).

Постоянное запоминающее устройство 9.2 предназначено для выдачи вариантов решения на изменение параметров кодера 1, генератора случайных чисел 2 и счетчика 4 по кодовой комбинации-адресу, поступающей от сумматора 9.1 (Основы импульсной и цифровой техники. /Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - рис. 6.10, с. 197 - 199.

Дискретные фильтры Калмана 10 и 11, предназначены для рекурсивного оценивания случайного процесса обслуживания заявок в устройстве, позволяющего получать не смещенные оценки с минимальными дисперсиями ошибок оценивания. Дискретные фильтры Калмана 10 и 11 представляют собой устройство рекурсивного оценивания нестационарного состояния системы, обеспечивая оптимальность оценок в смысле минимума среднеквадратической ошибки (Э.Сейдж, Дж.Мелс. Теория оценивания и ее применение в связи и управлении. М.: Связь, 1976, - с. 252-264). Могут быть реализованы на ИМС серий 176, 116.5.

Счетчик необслуженной нагрузки 12 и счетчик обслуженной нагрузки описаны в работе "Микросхемы и их применение". Справ. пособие. (В.А.Батушев, В.Н. Вениаминов, В.Г.Ковалев и др. - М.: Радио и связь 1984, - с. 139, рис. 4.38. 13). Могут быть реализованы на ИМС серий 133, 564.

Коррелятор 14 предназначен для согласованного приема широкополосных сигналов пользователей. Он представляет собой квазикогерентный приемник с поиском и синхронизацией по времени и по частоте. (Варакин Л.Е. Системы связи с шумоподобными сигналами. М.: Радио и связь, 1985, - с. 315- 323). Может быть реализован на ИМС серий 176, 155.

Решающий блок 15 предназначен для определения факта успешной передачи в канале или оценки кратности конфликта в противном случае и коммутации пакета на вход блока анализа адреса 16. Одним из вариантов реализации решающего блока 15 может быть схема, показанная на фиг.4, при этом он состоит из n компараторов 15.11 oC15.1n, инвертора 15.2, первого и второго формирователей импульсов 15.3, 15.4 соответственно, RS-триггера 15.6, первого и второго элементов И 15.8, 15.9, n-входового элемента ИЛИ 15.5, преобразователя параллельного кода в последовательный 15.7, причем объединенные входы n компараторов 15.11 oC15.1n и информационный вход второго элемента И 15.9 являются входом решающего блока 15, выход второго элемента И 15.9 является информационно-адресным выходом решающего блока 15, выход первого компаратора 15.11 соединен с входом первого формирователя импульсов 15.3 и входом инвертора 15.2, выход которого соединен с входом второго формирователя импульсов 15.4, выход которого соединен с R-входом триггера 15.6, S-вход которого соединен с выходом первого формирователя импульсов 15.3, выход триггера 15.6 соединен с сигнальным входом первого элемента И 15.8, второй инверсный управляющий вход которого соединен с выходами n-1 компараторов 15.12 oC15.1n n-1 входами преобразователя параллельного кода в последовательный 15.7, выход которого является вторым информационным выходом решающего блока 15, выход первого элемента И 15.8 соединен с вторым входом второго элемента И 15.9 и одновременно является первым информационным выходом решающего блока 15.

Компаратор 15.11 oC15.1n предназначен для выработки управляющего сигнала логического уровня. Может быть реализован по схеме, описанной в работе "Микросхемы и их применение: Справочное пособие" (В.А.Батушев, В.Н.Мирошниченко. - М.: Радио и связь, 1983, - рис. 2.33(б), с. 82).

Преобразователь кодов 15.7 предназначен для преобразования параллельного кода кодовой комбинации в последовательный код. Может быть реализован по схеме, описанной в работе "Полупроводниковые цифровые микросхемы. Справочник". (В.Л.Шило, Челябинск: Металлургия, 1989, рис. 2.52 a, c. 246-250).

Блок анализа адреса 16 предназначен для выделения адреса из заголовка пакета и принятия решения на дальнейшую ретрансляцию пакета в сети или вывод его абоненту. Одним из вариантов реализации блока анализа адреса 16 может быть схема, показанная на фиг. 5, которая состоит из формирователя импульсов 16.4, триггеров 16.2, 16.3, 16.14, 16.15, элементов И 16.6, 16.7, 16.12, 16.13, 16.17, 16.18, счетчиков 16.9, 16.10, регистра сдвига 16.5, элементов ИЛИ 16.8, 16.16, N сумматоров по модулю два 16.111 oC16.1N, инвертора 16.19, причем объединенные входы формирователя импульсов 16.4 и элемента И 16.17 являются информационно-адресным входом блока анализа адреса 16, выход формирователя импульсов 16.4 соединен с S-входами первого и третьего триггеров 16.2 и 16.3, выход генератора тактовых импульсов соединен с тактовыми входами элементов И 16.6, 16.7, 16.18, выход триггера 16.2 связан с сигнальным входом элемента И 16.6, а выход элемента И 16.6 соединен со счетным входом счетчика 16.9, выходы счетчика 16.9 подключены к соответствующим входам элемента И 16.12, выход которого соединен с S-входами триггеров 16.14 и 16.15 и R-входами триггера 16.2 счетчика 16.9. Выход триггера 16.14 подключен к управляющему входу элемента И 16.17, выход которого соединен с D-входом регистра сдвига 16.5. Выход триггера 16.3 связан с сигнальным входом элемента И 16.7, выход которого подключен к счетному входу счетчика 16.10, выходы которого соединены с соответствующими входами элемента И 16.13, выход которого соединен с R-входами триггеров 16.3, 16.14, 16.15 счетчика 16.10. Выход триггера 16.15 подключен к сигнальному входу элемента И 16.18, выход которого подключен к R-входу регистра сдвига 16.5, выходы 1oCN которого соединены с соответствующими входами элемента ИЛИ 16.8 и одновременно с первыми входами N сумматоров по модулю два 16.111 oC16.1N, на вторые входы которых подаются элементы кодовой комбинации собственного адреса с адресного входа блока анализа адреса, который является адресным входом устройства, выход элемента ИЛИ 16.8 соединен с R-входом регистра сдвига 16.5, выходы сумматоров 16.111 oC16.1N соединены с 1oCN входами элемента ИЛИ 16.16 соответственно, выход которого является вторым информационным выходом блока анализа адреса 16 и устройства и одновременно соединен с входом инвертора 16.19, выход которого является первым информационным выходом блока анализа адреса 16 и устройства.

Генератор тактовых импульсов 16.1 описан в работе "Микросхемы и их применение". Справ. пособие. (1984, - с. 213, рис. 7.6). Может быть реализован на интегральных микросхемах (ИМС) серий 16.101, 176.

Счетчики 16.9, 16.10 описаны в работе "Основы импульсной и цифровой техники". (Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - рис. 5.38, с. 169 - 172).

Регистр сдвига 16.5 предназначен для преобразования информации путем ее сдвига под воздействием сдвигающих (тактовых) импульсов. Может быть реализован по схеме, описанной в работе "Основы импульсной и цифровой техники". (Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - рис. 5.28, с. 158-159).

Сумматоры по модулю два 16.111 oC16.11N предназначены для суммирования по модулю два в двоичном коде двух разрядов, поступающих на входы каждого из них. Может быть реализован по схеме, описанной в работе "Импульсные и цифровые устройства. Цифровые узлы и их проектирование на микросхемах". (О.И.Лебедев, А.М.Сидоров, - Л.: ВАС, 1980, - рис. 2.9, с. 31 - 34).

Формирователи импульсов 2.2, 15.3, 15.4, 16.4, входящие в генератор случайных чисел 2, решающий блок 15 и блок анализа адреса 16, предназначены для формирования из логического уровня короткого импульса, идентичны, известны и описаны в работе "Основы цифровой техники". (Л.А.Мальцева. М.: Радио и связь, 1986, - рис. 21, с. 30).

Логические элементы И 5, 7, 2.31-2.3k 15.8, 15.9, 16.6, 16.7, 16.12, 16.13, 16.17, 16.18, входящие в описываемое устройство, генератор случайных чисел 2, решающий блок 15 и блок анализа адреса 16, идентичны, известны и описаны в работе "Основы цифровой техники". (Л.А.Мальцева, Э.М.Фромберг. - М. : Радио и связь, - с. 30-31). Могут быть реализованы на ИМС серий 133 и 564.

Логические элементы ИЛИ 2.41 oC2.4p, 15.5, 16.8, 16.16, входящие в генератор случайных чисел 2, решающий блок 15 и блок анализа адреса 16, идентичны, известны и описаны в работе "Основы импульсной и цифровой техники". (Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, - рис. 2.4, с. 39 - 41).

RS-триггеры 6, 15.6, 16.2, 16.3, 16.14, 16.15, входящие в описываемое устройство, решающий блок 15 и блок анализа адреса 16, идентичны, известны и описаны в работе "Микросхемы и их применение". (Справ. пособие. В.А.Батушев, В. Н. Вениаминов, В.Г.Ковалев и др. - М.: Радио и связь 1984, - с. 122, рис. 4.16). Могут быть реализованы на ИМС серий 133, 564.

Инверторы 15.2, 16.19 предназначены для формирования выходного напряжения с логическим уровнем, противоположным логическому уровню входного напряжения. Может быть реализован по схеме (Справочная книга радиолюбителя-конструктора: В двух книгах под ред. Н.И.Чистякова, кн.1, - М.: Радио и связь, 1993, - рис. 1.47 в, c. 30).

Заявляемое устройство работает следующим образом. Очевидно, что при функционировании системы связи нагрузка в ней будет пульсирующей и будет изменяться в зависимости от количества абонентов, интенсивности их обмена, характеристик канала связи. Наиболее динамично меняться будет нагрузка в системах подвижной связи. В этих условиях станции сети используют сигнально-кодовую конструкцию в одном цикле передачи, позволяющую вести одновременную передачу Na пакетов. Это достигается за счет использования сигналов с базой B>>1, где количество активных абонентов определяется видом модуляции, способом ортогонализации сигналов и требованиями к уровням взаимных шумов неортогональности.

Кодеры станций имеют возможность равновероятного выбора одной из Na структур сигнала, а в приемнике ретранслятора с обработкой сигнала реализуется Na ветвей приема. Поэлементная синхронизация в каждой ветви осуществляется независимо от адреса пакета, поэтому ретранслятор имеет возможность наблюдать число обслуженных, необслуженных пакетов в цикле передач. Состояние кодера станции в начале очередного цикла передачи определяет устройство динамического управления на основе оценки нагрузки. Это позволяет поддерживать вероятностно-временные характеристики доставки пакетов на уровне требований.

Функциональная схема устройства, реализующего выполнение описанных функций управления передачей данных по радиоканалу, приведена на фиг. 1.

Принцип работы предлагаемого устройства заключается в следующем.

При включении питания триггер 6 устанавливается в режим хранения логической единицы. Синхронизатор 3 выдает импульсы с интервалом, равным длительности окна (то есть равным длительности интервала передачи пакета), при этом импульсы поступают на тактовый вход второго элемента И 7 и на тактовый вход счетчика 4, вызывая последовательную смену на выходе счетчика 4 кодовых комбинаций (число кодовых комбинаций равно числу окон в цикле передачи).

При возникновении необходимости в передаче пакета на управляющий вход устройства в виде уровня логической единицы поступает сигнал запроса передачи. При этом очередной сигнал в виде импульса с уровнем логической единицы поступает с выхода синхронизатора 3 через открытый второй элемент И 7 на управляющий вход первого элемента И 5.

Так как первый элемент И 5 открыт по сигнальному входу сигналом запроса передачи, то импульс с уровнем логической единицы с выхода первого элемента И 5 поступает на вход R RS-триггера 6, переводя его в режим хранения логического нуля, а также на управляющий вход генератора случайных чисел 2, который в параллельном коде выдает со своего выхода на второй сигнальный вход блока сравнения 8 кодовую комбинацию, соответствующую номеру окна в цикле передачи, выбранному для передачи пакета. При этом RS-триггер 6 сигналом с уровнем логического нуля закрывает второй элемент И 7. В момент совпадения кодовых комбинаций на первом и втором входах блока сравнения 8 последний выдает сигнал "разрешение передачи" в виде импульса с уровнем логической единицы на управляющий выход устройства, а также переводит RS-триггер 6 в режим хранения логической единицы (сигнал "запрос передачи" с управляющего входа устройства снимается).

Таким образом, устройство готово к передаче очередного пакета.

При появлении в канале множественного доступа передаваемой информации, принятый пакет поступает в устройство через сигнальный вход на вход коррелятора 14, на выходе которого выделяется отклик поступающего сигнала. Решающий блок 15 по данному отклику позволяет определить количество корреспондентов, одновременно работающих в i-й ветви из Na ветвей приема.

Если величина отклика свидетельствует о конфликте двух и более корреспондентов, работающих в одной и той же ветви приема, то со второго информационного выхода решающего блока 15 информация о кратности конфликта (то есть о количестве конфликтующих корреспондентов) поступает на вход счетчика необслуженной нагрузка 12. Если i-ю ветвь для работы выбрал один корреспондент, то на единицу увеличивается содержимое счетчика обслуженной нагрузки 13.

При этом блок анализа адреса 16 выделяет из пакета комбинацию адреса и после его анализа выдает сигнал либо на первый информационный выход устройства (если адрес получателя совпал с собственным адресом), либо на второй информационный выход (если адрес получателя не совпал с собственным).

По окончании интервала анализа количества обслуженных и необслуженных заявок с выходов блоков 12 и 13 значения количества пакетов, попавших в конфликт и успешно переданных, подается на дискретные фильтры Калмана 10 и 11 соответственно. В них реализуется алгоритм оценивания наблюдаемых параметров в нормальных шумах канала связи для дискретного времени, определяемого длительностью цикла передачи. Этот алгоритм формирует линейную несмещенную оценку с минимальной дисперсией. Устройство и порядок функционирования дискретного фильтра Калмана представлены в работе "Оптимальное управление системами" (Э.П.Сейдж, И.С.Уайт. М.: Радио и связь. 1982, с. 216-223).

На основе оценок обслуженной и необслуженной нагрузки в блоке 9 производится расчет вероятности своевременной доставки пакета в соответствии с методикой, представленной в работе "Сборник молодых ученых за 1996 год" г. Орел, ВИПС, а также в статье "Методика оценки частного показателя эффективности линий многоканальной радиосвязи" (Е.Г.Белобров, А.Ю.Сафонов, с. 8-17). Для определения оптимальных значений позиционности сигналов и вероятности их повторной передачи, максимизирующих вероятность своевременной доставки пакета в систему связи множественного доступа, используются методы динамического программирования Белмана, заключающиеся в последовательном выполнении им пошаговой оптимизации, где оптимальное управление определяется лишь состоянием системы связи множественного доступа и целью и не зависит от состояния в предыдущие моменты времени. Устройство и принцип работы устройства дискретного динамического программирования на основе принципов Белмана рассмотрены в работе "Оптимальное управление системами" (Э.П.Сейдж, И. С.Уайт, с. 278-287).

Генератор случайных чисел 2, функциональная схема которого приведена на фиг. 2, работает следующим образом.

Изменение соотношения обслуженной и необслуженной нагрузки в канале множественного доступа приводит к изменению кодовой комбинации на входе демультиплексора 2.1. При этом сигнал с уровнем логической единицы с одного из k выходов демультиплексора 2.1 открывает по первому входу один из k элементов И 2.3, благодаря чему к выходу формирователя импульсов 2.2 оказываются подключенными соответствующие группы элементов ИЛИ 2.4 (и соответственно синхровходы соответствующих групп D-триггеров 2.6). Каждая группа D-триггеров 2.6 обеспечивает различную длину кодовой комбинации на выходе генератора случайных чисел 2. На информационных входах каждого из D-триггеров 2.6 имеют место случайно изменяющиеся во времени выходные напряжения независимых генераторов шума 2.5. Если в момент появления импульса на синхровходе i-го триггера 2.6 выходное напряжение i-го генератора шума 2.5 ниже порога срабатывания триггера, то на выходе триггера будет иметь место уровень логического нуля (в противном случае - уровень логической единицы). Случайная кодовая комбинация с выходов триггеров 2.6 поступает на второй сигнальный вход блока сравнения 8.

Блок преобразования 9, функциональная схема которого приведена на фиг. 3, работает следующим образом. Кодовые комбинации, характеризующие интенсивность потоков обслуженной и необслуженной нагрузки, поступающие на первый и второй сигнальные входы блока преобразования с выходов фильтров Калмана 10 и 11 соответственно, суммируются в сумматоре 9.1. Кодовая комбинация - результат сложения с выходов сумматора 9.1 поступает на входы ПЗУ 9.2, в котором хранятся варианты решения на изменение параметров кодера 1, генератора случайных чисел 2 и счетчика 4. Очередное решение в виде кодовой комбинации с выходов ПЗУ 9.2 поступает на выход блока преобразования 9.

Решающий блок 15, показанный на фиг. 4, работает следующим образом. Информация из канала множественного доступа с выхода коррелятора 14 поступает на вход решающего блока 15. Здесь отклик коррелятора поступает на входы компараторов 15.11 oC15.1n. Если величина отклика превышает порог срабатывания компаратора 15.11, но не превышает порога срабатывания компаратора 15.12 (то есть в канале множественного доступа работает только один корреспондент), то сигнал с уровнем логической единицы с выхода компаратора 15.11 при посредстве формирователей импульсов 15.3 и 15.4 и инвертора 15.2 переводит триггер 15.6 в режим хранения логической единицы. При этом наличие на управляющем инверсном входе элемента И 15.8 уровня логического нуля приводит к появлению на выходе элемента И 15.8 сигнала с уровнем логической единицы, что обеспечивает прохождение информации через элемент И 15.9 на информационно-адресный выход решающего блока 15. Одновременно сигнал поступает на первый информационный выход решающего блока 15 (и далее на вход счетчика обслуженной нагрузки 13). Если в канале множественного доступа произошел конфликт, то величина отклика коррелятора будет пропорциональна числу конфликтующих корреспондентов: поэтому на выходах k первых компараторов из общего числа n появляются сигналы с уровнем логической единицы, которые поступают на соответствующие входы преобразователя кодов 15.7, который с второго информационного выхода решающего блока 15 в последовательном коде передает кодовую комбинацию, соответствующую числу конфликтующих корреспондентов, на вход счетчика необслуженной нагрузки 12.

При передаче в канале множественного доступа информации содержимое пакета с информационно-адресного выхода решающего блока 15 поступает на информационно-адресный вход блока анализа адреса 16, показанного на фиг.5. При этом импульс с выхода формирователя импульсов 16.4 переводит RS-триггеры 16.2, 16.3 в единичное состояние. В результате последовательность тактовых импульсов через открытые элементы И 16.6, 16.7 поступает на счетные входы C1 счетчиков 16.9, 16.10.

Счетчик 16.9 отсчитывает количество символов заголовка, предшествующих символам адреса, после чего сигналом с уровнем логической единицы переводит RS-триггер 16.2 в нулевое состояние (поступление тактовых импульсов на вход счетчика 16.9 прекращается), а RS-триггеры 16.14, 16.15 - в единичное, при этом на вход синхронизации C регистра сдвига 16.5 поступает последовательность тактовых импульсов, а на его информационный вход D - последовательность символов заголовка пакета, начиная с первого символа адреса.

Счетчик 16.10, закончив отсчет количества символов, предшествующих символам адреса, и количества символов самого адреса, выдает сигнал с уровнем логической единицы на входы R RS-триггеров 16.14, 16.3, 16.15 и переводит их в нулевое состояние. При этом поступление информации и тактовых импульсов на входы регистра сдвига 16.5 прекращается. Кодовая комбинация адреса, выделенная из заголовка пакета, в параллельном коде поступает с выходов регистра сдвига 16.5 на входы элемента ИЛИ 16.8 (при этом сигнал с уровнем логической единицы с выхода элемента ИЛИ 16.8 поступает на вход R регистра сдвига 16.5 и переводит его в нулевое состояние), а также на первые входы сумматоров по модулю два 16.111-16.11N, при этом на вторые входы последних поступает кодовая комбинация собственного адреса. Если адрес в заголовке пакета совпал с собственным адресом, то появляется сигнал на первом информационном выходе устройства (в противном случае появляется сигнал на втором информационном выходе устройства).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2148294C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2216869C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1995 |

|

RU2099889C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных автоматизированной системы управления. Целью изобретения является разработка устройства управления передачей данных по радиоканалу множественного доступа с кодовым и временным разделением сигналов, обеспечивающего повышение пропускной способности, за счет адаптации к изменению параметров нагрузки. Устройство управления передачей данных по радиоканалу включает кодер, генератор случайных чисел, синхронизатор, счетчик, первый элемент И, RS-триггер, второй элемент И, блок сравнения, блок преобразования, дискретные фильтры Калмана, счетчик необслуженной нагрузки, счетчик обслуженной нагрузки, коррелятор, решающий блок, блок анализа адреса. Перечисленная новая совокупность существенных признаков обеспечивает технический результат - использование заявленного устройства в каналах с кодовым и временным разделением благодаря введению в нее элементов, позволяющих динамически оценивать параметры нагрузки, а по результатам оценки адаптировать схему устройства. 5 ил.

Устройство управления передачей данных по радиоканалу, содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, RS-триггер, второй элемент И, блок сравнения, причем управляющий вход устройства является одновременно сигнальным входом первого элемента И, а вход счетчика соединен с первым сигнальным входом блока сравнения, отличающееся тем, что дополнительно введен кодер, блок преобразования, первый и второй дискретные фильтры Калмана, счетчик обслуженной нагрузки, счетчик необслуженной нагрузки, коррелятор, решающий блок, блок анализа адреса, причем информационный вход кодера является информационным входом устройства, а его выход является сигнальным выходом устройства, выход блока преобразования подключен в параллель к сигнальным входам кодера, генератора случайных чисел и счетчика, тактовый вход которого подключен к выходу синхронизатора, второй сигнальный вход блока сравнения подключен к выходу генератора случайных чисел, управляющий вход первого элемента И подключен к выходу второго элемента И, тактовый и управляющий входы которого подключены соответственно к выходу синхронизатора и выходу RS-триггера, S- и R-входы которого подключены соответственно к выходу блока сравнения и выходу первого элемента И, который дополнительно подключен к управляющему входу генератора случайных чисел, второй и первый информационные выходы решающего блока подключены соответственно к счетчикам необслуженной и обслуженной нагрузки, выходы которых подключены к входам соответственно первого и второго фильтров Калмана, выходы которых подключены к первому и второму входам блока преобразования соответственно, вход коррелятора является сигнальным входом устройства, а его выход подключен к входу решающего блока, информационно-адресный выход которого подключен к информационно-адресному входу блока анализа адреса, первый и второй управляющие выходы которого являются соответственно первым и вторым информационными выходами устройства, выход блока сравнения является управляющим выходом устройства, а адресный вход блока анализа адреса является адресным входом устройства.

| SU, авторское свидетельство, 1162058, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельство, 1319298, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-07-20—Публикация

1997-08-22—Подача