(54) УСТРОЙСТВО ДЛЯ СО11РЯЖЕНИЯ ПРОЦЕССОРОВ С ВНЕШНИ.МИ АБОПЕПТ.4..АП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

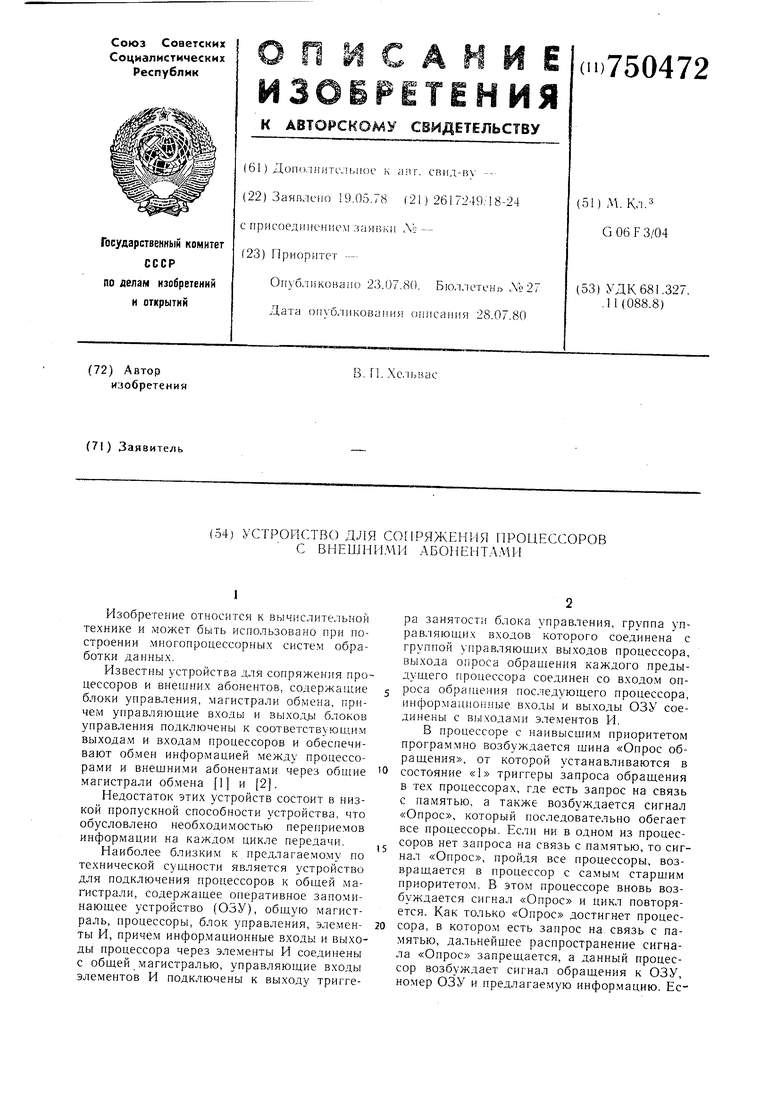

1

Изобретение относится к в.ычислительной технике и может быть использовано нри построении многопроцессорных систем обработки данных.

Известны устройства для сопряжения процессоров и внешних абонентов, содержащие блоки управления, магистрали обмена, причем управляющие входы и выход,ы блоков управления подключены к соответствующим выходам и входам процессоров и обеспечивают об.мен информацией между процессорами и внешними абонентами через общие магистрали об.мена 1 и 2.

Недостаток этих устройств состоит в низкой пропускной способности устройства, что обусловлено необходи.мостью переприемов информации на каждом цикле передачи.

Наиболее близким к предлагаемому по технической сущности является устройство для подключения процессоров к общей магистрали, содержащее оперативное запоминающее устройство (ОЗУ), общую магистраль, процессоры, блок управления, элементы И, приче.м инфор.мационные входы и выходы процессора через элементы И соединены с общей магистралью, управляющие входы элементов И подключены к выходу триггера занятости блока управления, группа управляющих входов которого соединена с группой управляющих выходов процессора, выхода опроса обрандения каждого предыдущего процессора соединен со входо.м опроса обращения последующего процессора, информационные входы и выходы ОЗУ соединены с выходами элементов И.

В процессоре с наивысшим приоритетом программно возбуждается щина «Опрос обращения, от которой устанавливаются в

О состояние «1 триггеры запроса обращения в тех процессорах, где есть запрос на связь с памятью, а также возбуждается сигнал «Опрос, который последовательно обегает все процессоры. Если ни в одном из процессоров нет запроса на связь с памятью, то сигнал «Опрос, пройдя все процессоры, возвращается в процессор с самы.м старщим приоритетом. В этом процессоре вновь возбуждается сигнал «Опрос и цикл повторяется. Как только «Опрос достигнет процессора, в котором есть запрос на, связь с памятью, дальнейшее распространение сигнала «Опрос запрещается, а данный процессор возбуждает сигнал обращения к ОЗУ, номер ОЗУ и предлагаемую информацию. Если ОЗУ, которому адресовано это обржцение, не занято внутренним циклом qTciiHH или зг.-пясн, то л, процессор нст :эс т в сеанс связи с этим ОЗУ, и осу1иеств.1яется передача информации. Если ОЗУ, которому адресовано обращение, занято ииутренним циклом чтения или записи oi нре;|,Ь;-дущего занроса, то данный процессор, н; л чив си. «Отпет занят()стк,-. форын;)ует сигнал «Опрос, который г;род,олжает )асгространяться далее к другим процессорам 3. Недостатком известно о устройства является его низкая пропускная сиособяость. Цель изобретения -- повып-ение пропускной способности устройства. Поставленная цель достигается те.м, что я устройство ;;::1я сопряжения процессоров с внеанилн обонентамн, содержащее М коммутаторов процессоров. ка.:Кдый из котор1зг. содержит блок уцравлен.и:я, ггервая /ззуцпа управляющк.к в.ходов и выходов 1;})изнака нецрогэаммированной команды которого соединены соответственно с первой группой управляюЦих вь ходов и входом признака команды соответствующего процессора, .руппы информационных входов и выходов котоpoio соединены соответственно с гру11пой информац 1онных вь ходов первой группы э.чементов И, соединенной группой зходов с магистралью ввода информации от BHCUJHUX абонентов, и с груцпой информацион.ньгх УХО ДОВ второй группы элементов И, подк;по-:е 1ной группой выходов к .магистрали вывода информации на внеплние абоненты, управляющие входы первой и второй групп элементов И подключены к выходу цодключе.чия процессора блока управления, первые ) :оритетные вход и выход блока управленк;; -го коммутатора процессора соедине;1ы соответственно со вторыми ,:лОМ И ВХОДОМ приоритета блока управления i -h 1-го ко.ммутатора процессора (i 1,М), в хажаы); коммутатор процессора заеден блок буферной памяти, соединеньный груп1ками инс эормационных входов и выходов соответственно с групной информационных выходов кроцессора и магистралью вывода икформапии на внегпние абоненты, группой управляющих входов - со второй грунпой управлнюгцих выходов блока управления, группой адресных входов - с груцпой адресн1 1х выходов процессора, группой выходов непрограммированной команды - с группой входов непрограммированной команды процессора. а первым ,и вторым управляющими выход,ами - соответственно с первым и вторым входами синхронизации блока управления. Кроме того блок буферной памяти содержит реверсивный регистр сдвига, W инфор.мационных регистров, шифратор, четыре элемента И, пять элементов ИЛИ, элемент НЕ, два элемента задержки, причем группа информационных входов блока соединена с группой информационных входов первого элемента IL группа выходов которого подключена к первой группе входов первого элемента ИЛИ. вторая группа входов которого соединепа с группой выходов второго элемента И, соединенного группой входов с группой адресных входов блока, а группа выходов -- с первой группой входов информацио) регистров, выходы i-ro (i 2, W) ин())(;;;манио}1иого регистра, кроме первого, соединены со второй группой входов i-1-го информационного регистра, группа выходов iiepBoro информационного регистра соединена с гругнтой входов третьего и четвертого элементов И, а выход последнего разряда первого информационного регистра соединен с первым управляющим выходом блока, входы второго и третьего элементов ИЛИ первые входы четвертого и пятого элементов ИЛИ, управляющие входы первого, второго и третьего элементов И и вход шифратора подключены к соответствующим входам гр пт1ы у травлйюших входов блока, выход второго элемента ИЛИ соединен со вторым входом четвертого элемента ИЛИ, выход коTopoio через первый элемент задержки подключс -; к первому синхронизируюпге.му вхо.ду peiHCTpa С;:1,вига, выход третьего элемента ИЛИ соединен с управляюпдим входом , 1.;от 1ертого элемента И и вторым входом пягого элемента ИЛИ, выход которого через второй элемент задержки еоединен со вторь м сп 1хронизирующим входом регистра и с сиь.схронизирующи и входами информационных регистров, выход каждого разряда регистра сдвига подключен к управляющему входу соответствующего информационного регистра, а выход первого разряда - через элемент НЕ со вторы.м управлгиощим выходом б.лока, группа выходов шифратора и группа выходов третьего эле.Чтента И подклкэчены к группе комаг1дных блока, группа выходов четвертого э.лемепта И сое.:1.инена с группой информационных выходов блока. Введ,ение блока буферной па.мяти. поззоляет повысить пропускную способность устройства, за счет того, что при обращении процессора к абонентам и занятости магистралей передачей информации со стороны другого процессора, информация обмена запоминается в блоке буферной памяти и в порядке приоритета посту 1ает на общие информационные магистрали, обеспечивая передачу необходи.мой информации. Таким образом, не нроисходит приостановки рабочей пр01раммы процессора в ожидании обмена. На сриг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока буферной памяти; на фиг. 4 и 5 - временные диаграммы операций программного вывода и ввода инфор.мании процессора; на фиг. 6 - структура управляющего слова; на фиг. 7 и 8 - вре.менные диаграммы работы устройства.

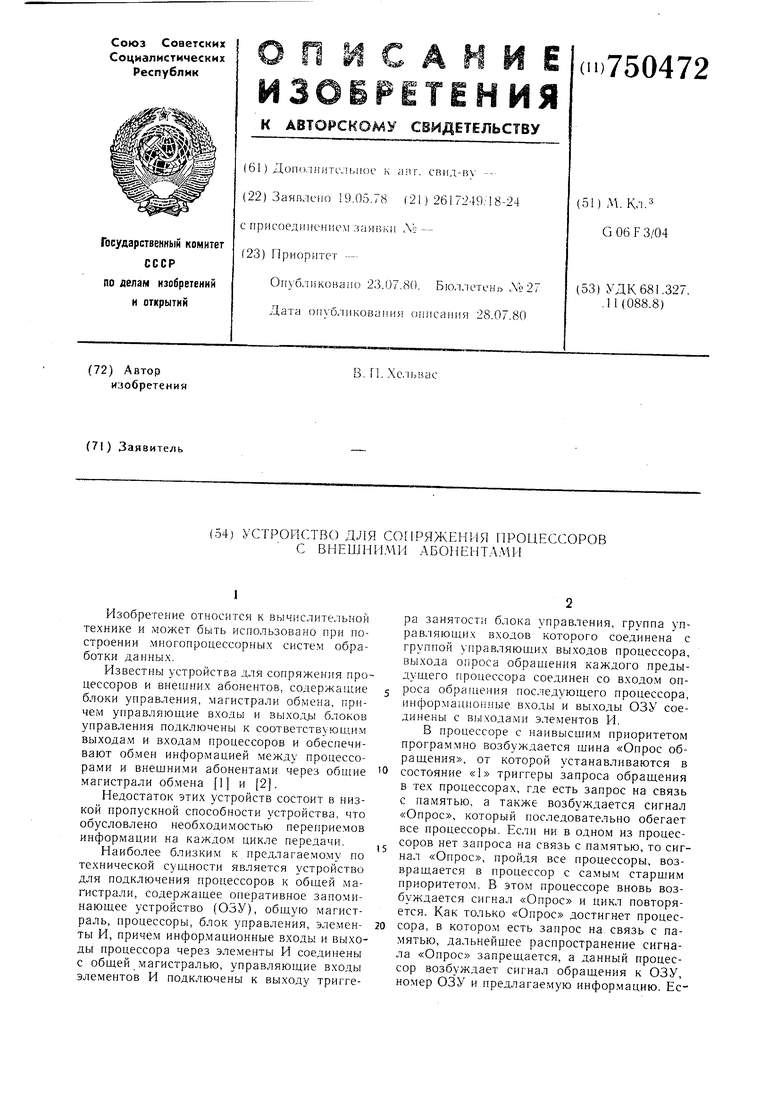

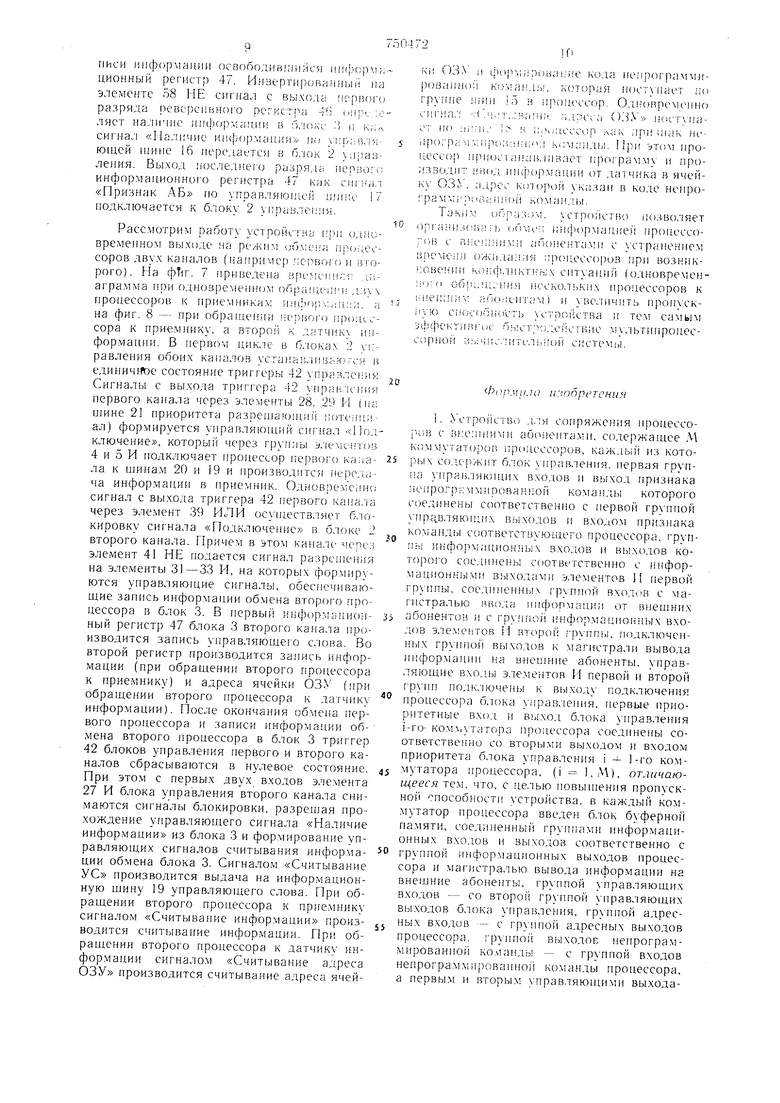

Схемы (фиг. 1) содержат процессоры I, блоки 2 управления, блоки 3 буферной памяти, первые 4 и вторые 5 группы элементов И, датчики 6 инфор.мации и приемники 7 информации, синхронизатор 8 группы 9 кодовых шин вывода, группы 10 кодовых шин ввода, первые группы 11 управляющих шин. группы 12 адресных шин процессора, шины

13подключения процессора, вторые группы

14управляюших шин, группы шин 15 нецрограммированной команды, первые 6 и вторые 17 управляющие шины, шины 18 признака непрограммированной команды, шины 19 и 20 информационных магистралей, шины 21-24 приоритета.

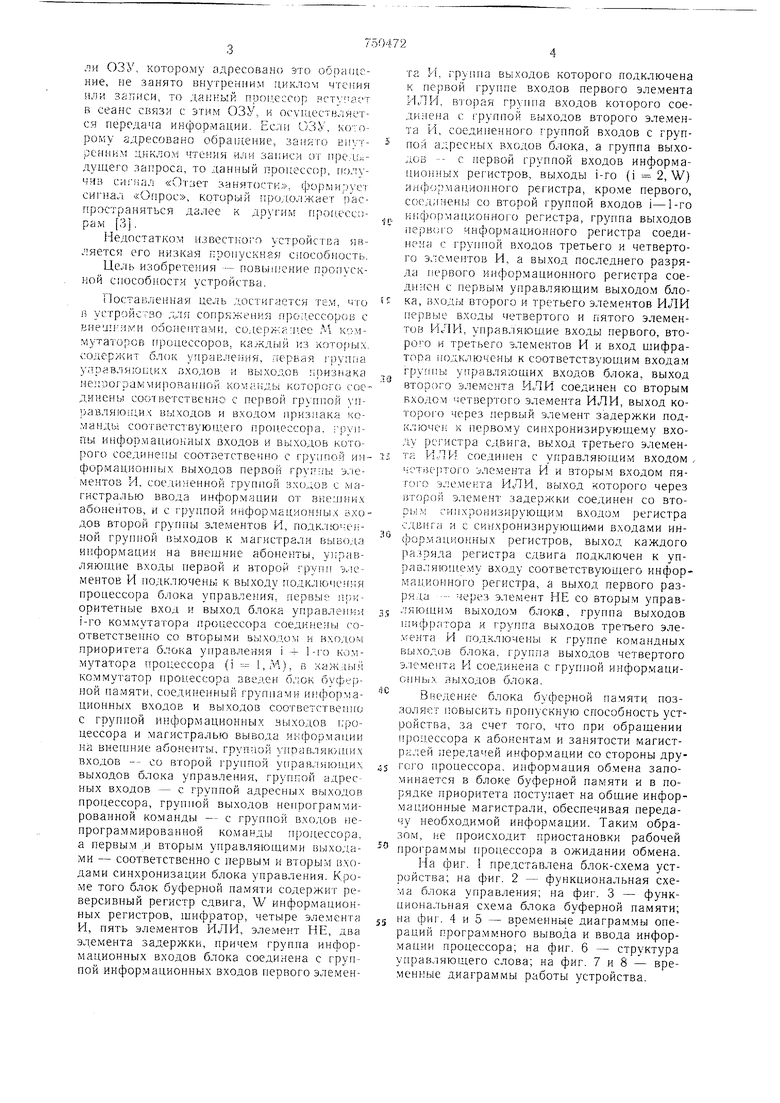

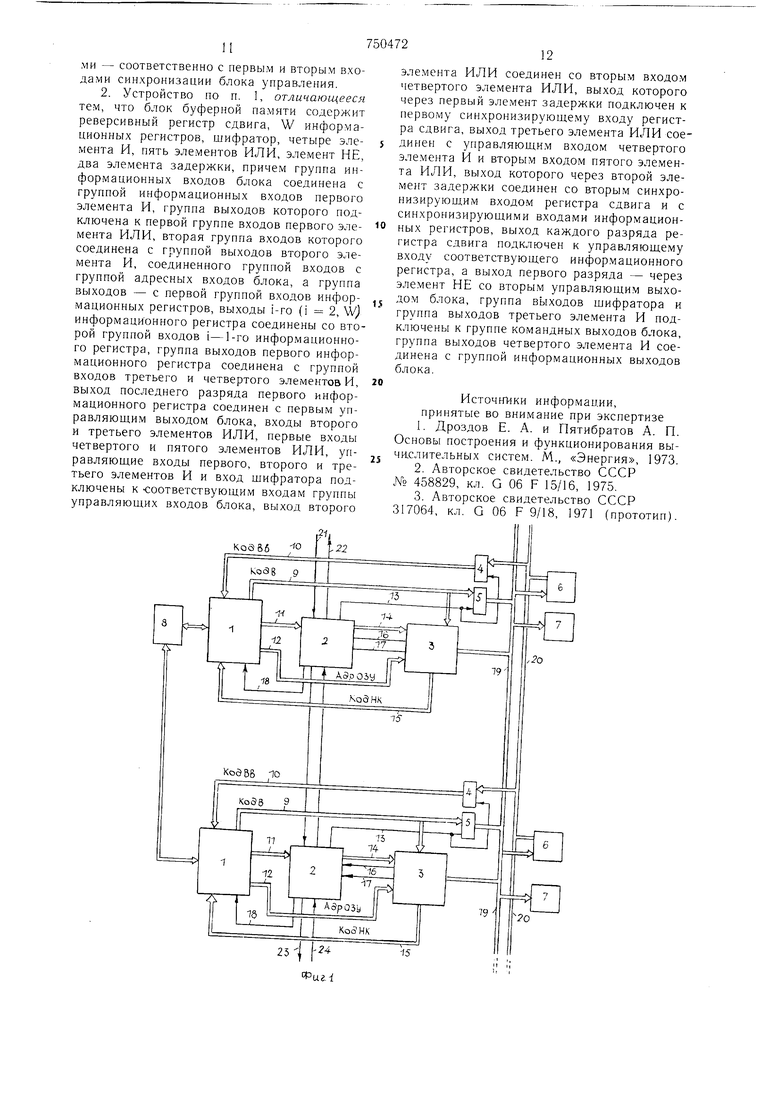

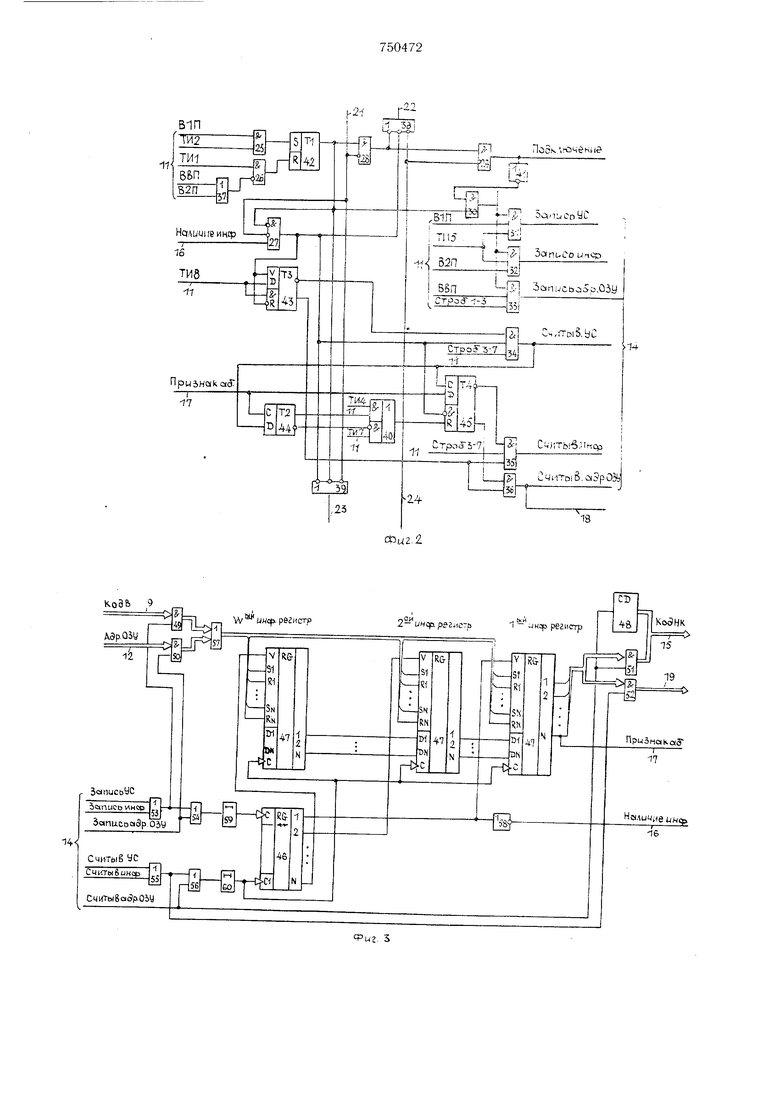

Кроме того содержат (фиг. 2) элементы 25-36 И, элементы 37-39 ИЛИ, элемент 40 И-ИЛИ, элемент 41 НЕ, триггеры 42- 44 управления и триггер 45 признака абонента реверсивный регистр 46 сдвига, информационные регистры 47, шифратор 48, элементы 49-52 И, элементы 53-57 ИЛИ, элемент 58 НЕ и элементы 59 и 60 задержки (фиг. 3).

Устройство работает следующим образом.

Процессоры 1 всех каналов обработки информации работают синхронно (тактовые сетки всех процессоров совпадают) и выполняют различные (или одинаковые) рабочие программы с общими для всех каналов внешними абонента.ми 6 и 7. В общем случае возможно подключение к общим информационным магистралям абонентов, которые обслуживаются только одним (или несколькими) каналами. Синхронность работы процессоров обеспечивается синхронизатором 8, конструкция и работа которого описана в прототипе. Передача информации между процессорами 1 и абонентами 6 и 7 осуществляется программой процессоров. Для устранения конфликтных ситуаций, возникающих при одновременно. обращении двух и более процессоров к общи.м шинам 19 и 20 обмена, все процессоры и.меют фиксированный уровень приоритета. При одповре.мснном выходе на режим обмена нескольких процессоров к .магистралям подключается процессор с высшим уровне.м приоритета. При этом информация обмена от процессоров с более низким уровнем приоритета размещается в соответствующем блоке 3, который в порядке приоритета подключается к информационной магистрали и передает управляющие слова и информацию соответствующе.му абоненту. Блок 3 имеет уровень приоритета на единицу меньше приоритета соответствующего процессора 1, т. е. при одновременном обращении в одном канале процессора и его блока 3 к абонентам сначала подключается процессор, а затем блок 3. Анализ состояния шин 19 и 20 информационных магистралей (заняты-свободны) и подключение процессора 1 при обмене либо к

ним, либо к б.юку 3 осуществляет блок 2 управле ия соответствующего канала.

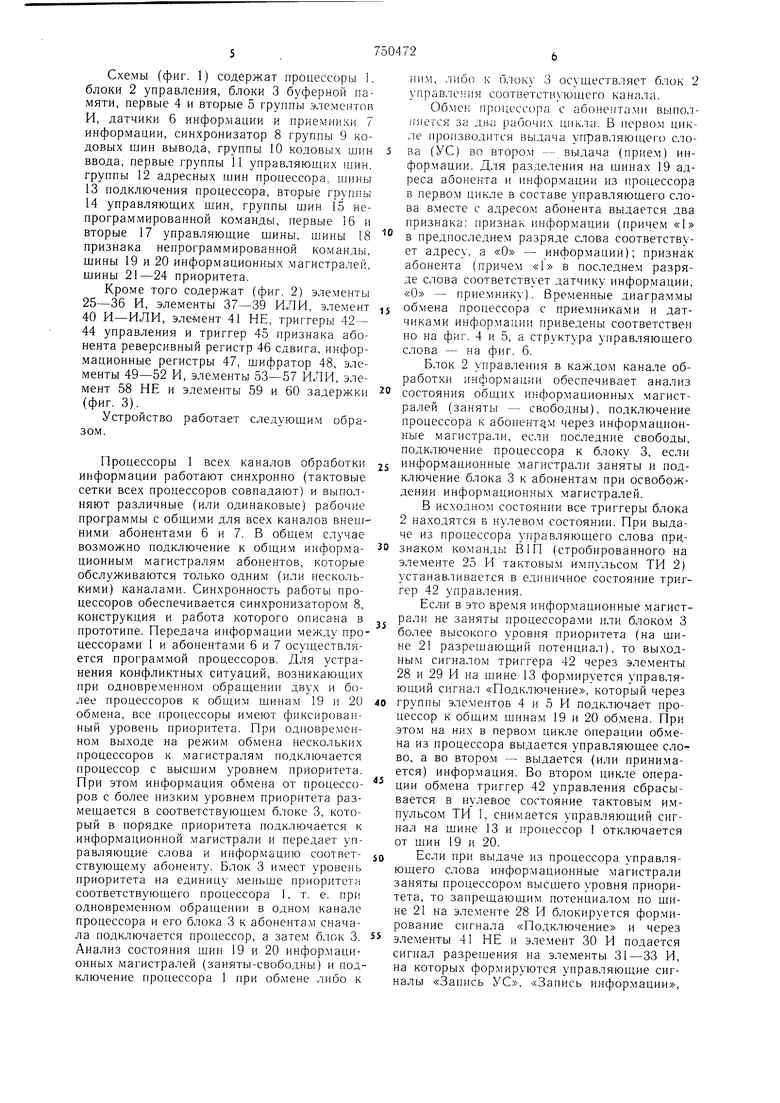

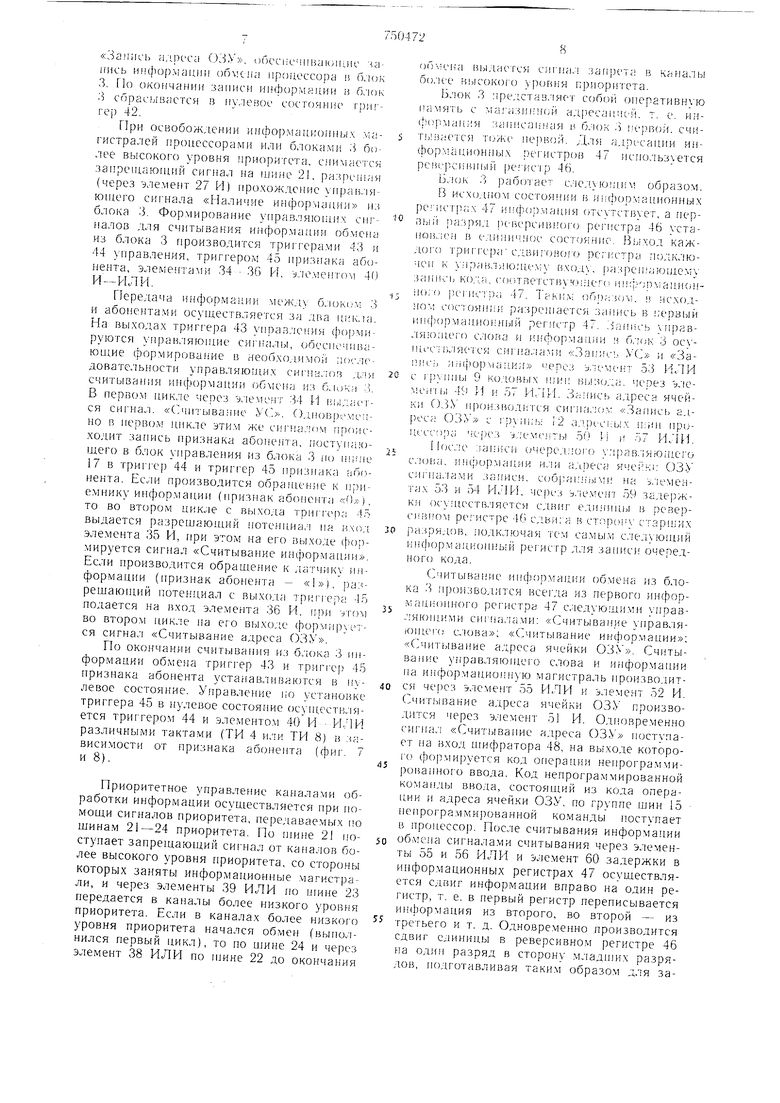

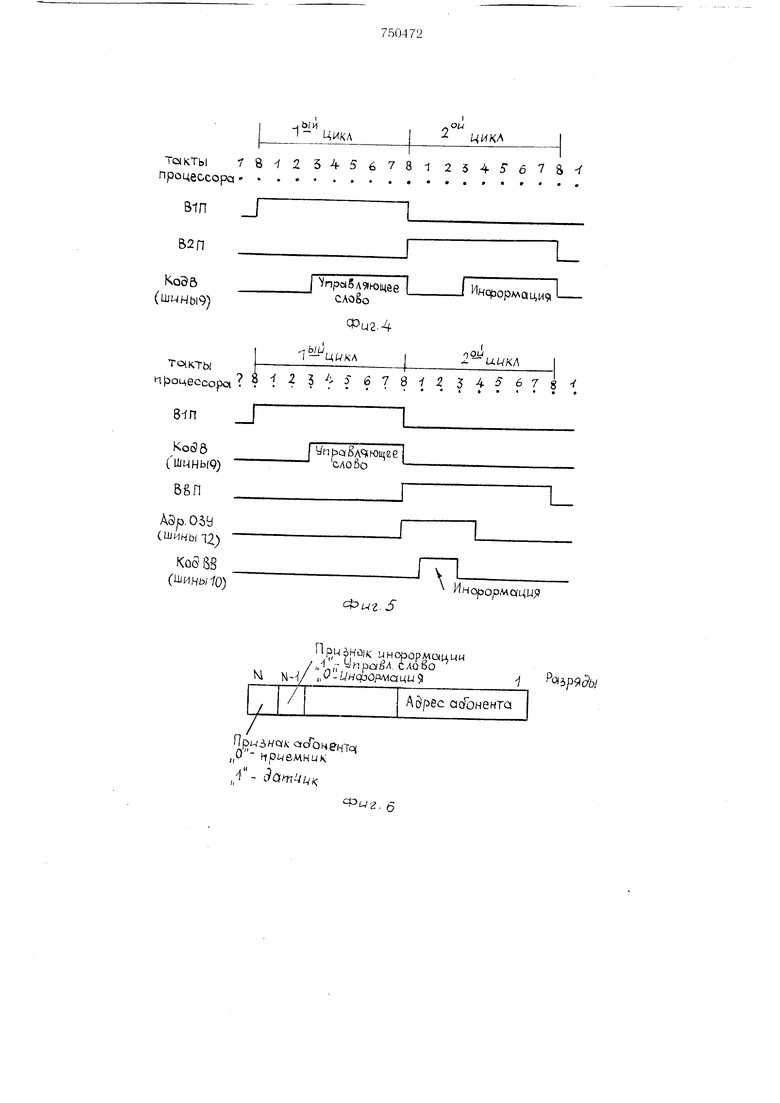

Обмен процессора с абонентами выпольяетск за два рабочих цикла. В первом цикле производится выдача управ.),его слова (УС) во втором - выдача (прием) информации. Для разделения на шинах 19 адреса абонента и инфор.мации из процессора в первом цикле в составе управляющего слова вместе с адресом абонента выдается два признака: 11ризнак информации (причем «1 в предпоследнем разряде слова соответствует адресу, а «О - информации); признак абонента (причем «I в последнем разряде слова соответствует датчику информации, «О - приемнику). Временные диаграммы обмена процессора с прие.мника.ми и датчика.ми информации приведены соответствен но на фиг. 4 и 5, а структура управляющего слова - на фиг. 6.

Блок 2 управления в каждом канале обработки информации обеспечивает анализ состояния общих информационных магистралей (заняты - свободны), подключение процессора к абонентам через информационные магистрали, если последние свободы, подключение процессора к блоку 3, если информационные магистрали заняты и подключение блока 3 к абонентам при освобождении информационных магистралей.

В исходном состоянии все триггеры блока 2 находятся в нулево.м состоянии. При выдаче из процессора управляющего слова признаком команды ЕЗIП (стробированного на элементе 25 И тактовы.м импульсом ТИ 2) устанавливается в единичное состояние триггер 42 управления.

Если в это время информационные магистрали не заняты процессорами или блоком 3 более высокого уровня приоритета (на шине 21 разрешающий потенциал), то выходным сигналом триггера 42 через элементы 28 и 29 И на шине 13 формируется управляющий сигнал «Подключение, который через группы элементов 4 и 5 И подключает процессор к общим шинам 19 и 20 об.мена. При это.м на них в первом цикле операции об.мена из процессора выдается управляющее слово, а во втором - выдается (или принимается) информация. Во второ.м цикле операции обмена триггер 42 управления сбрасывается в нулевое состояние тактовым импульсом ТИ 1, снимается управляющий сигнал на шине 13 и процессор 1 отключается от шин 19 и 20.

Если при выдаче из процессора управляющего слова информационные магистрали заняты процессоро.м высшего уровня приоритета, то запрешаюшим потенциалом по шине 21 на элементе 28 И блокируется формирование сигнала «Подключение и через элементы 41 НЕ и элемент 30 И подается сигнал разрешения на элементы 31-33 И, на которых формируются управляющие сигналы «Запись УС, «Запись информации.

«За.иись алрссс , (бесисчш ующие -запись HiKJiofj.vanHii () npoiieccopa к б.кж 3. о окончании записи .мацин и б.юк о сбрасывается в fiv.ieiioe состгкчиис гри.гге) 42.

При освобождеиии информациолиых магистралей процессорами или блокам); .i более высокого уровня приоритета, сни 1ается запреихаюший сигнал на 1иине 21, разрешая (через элел1е 1т 27 И) ирохожлсние .тиюи1его сигнала «Наличие иисрормаиии из блока ,. Формирование управляющих сигналов для считывания информации обмена из блока 3 производится триггерами 43 и 44 управления, триггером 45 иризнака абонента, элементами 34 - 36 И, улелкмггом 40 И--ИЛИ.

Передача информации между бл(;к1;м 3 и абонентами оеуществляется за два ппкла. На выходах трипера 43 хнразленин формируются управляющие сигналы, обеспечивающие формирование в нeoбxoдимoi :1осл(довательности управлиюидих сигна/юв для считываиия (пирормании обмена из блока ;-., В первом цикле через э.темент 34 Н -ылается си1Д1ал. «(дпггывание УС.. О.шовремепно в иерво.м цикле эти.м же .лом происходит запись иризнака aOoneirra, поступающего в блок управления из блока 3 ио ni:;iie 17 в трипер 44 и триггер 45 прнзиака абонента. Если производится обращение к прие.миику ипфор.мации (признак абопонта «ГЬ), то во втором цикле с выхо.ча тригччмта 45 выдается разрещающий нотеиниа, па нхо.т элемента 35 И, при этом на его выходе (формируется сигнал «Считывание информации. Если производится обращение к датчику информации (признак абонента - «I), jja.решающий потенциал с выхода триггера -15 подается на элемента 36 И, при 4ii во второ.м цикле на его вьгходе (()ормир ется сигна.т «Считывание адреса ОЗУ.

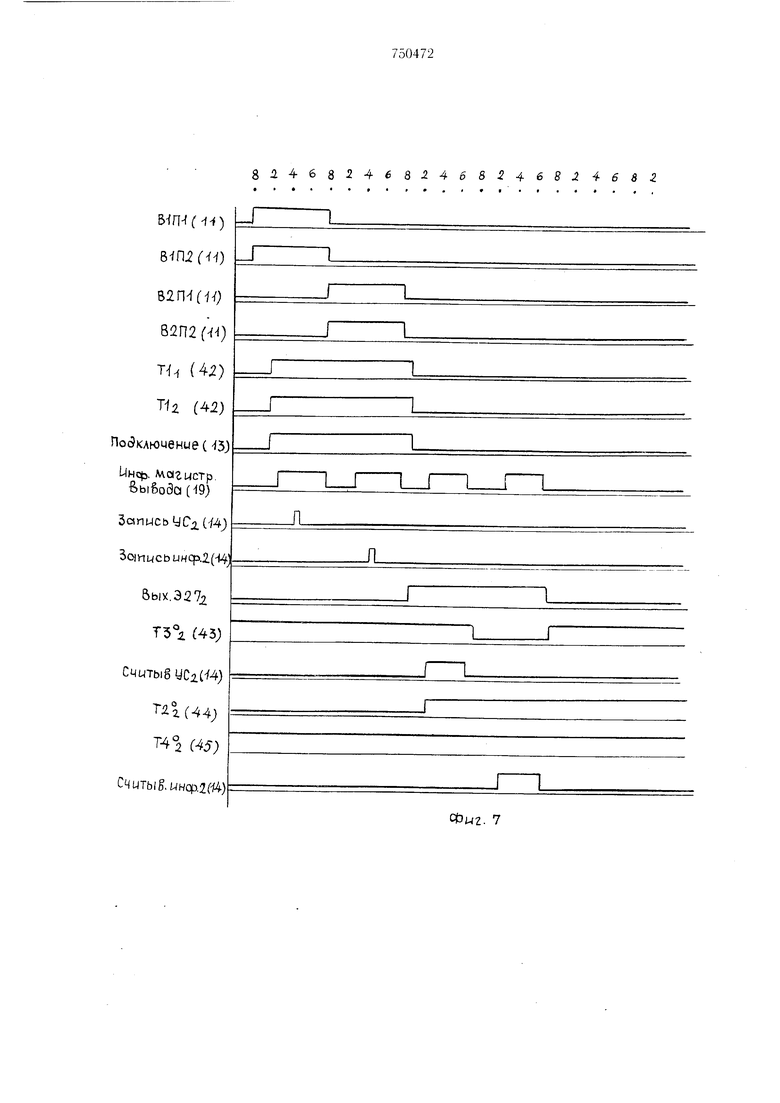

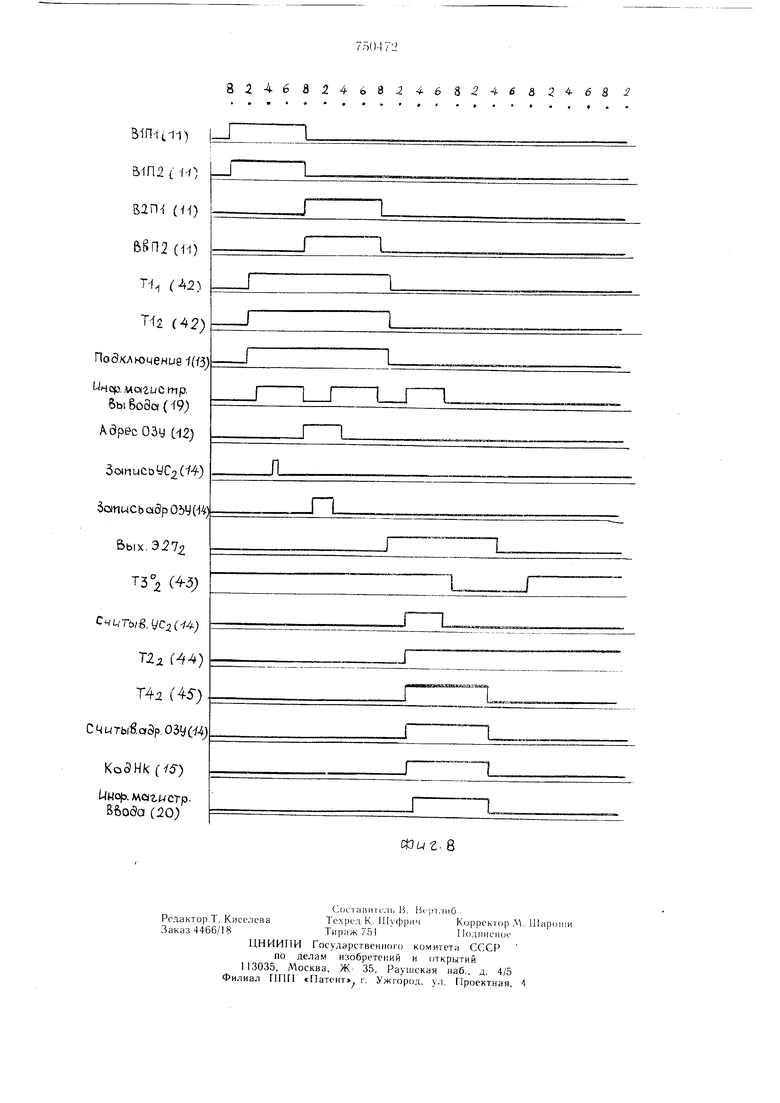

Но окончании считывания из б.юка 3 iniформации обмена триггер 43 и трип-ер 45 признака абонента устанавливаются в пулевое состояние. Управление но установке триггера 45 в нулевое состояние осу|цествляетея триггером 44 и элементом 40 И - ИЛИ различными тактами (ТИ 4 или ТИ 8) в зависимости от признака абонента (фиг. 7 и 8).

Приоритетное управление каналами обработки информации осуществляется при помощи сигналов приоритета, передаваемых шина.м 21-24 приоритета. По njHne 21 поступает запрещаюидий си1д1ал от каналов более высокого уровня приоритета, со стороны которых заняты информационные магистрали, и через эле.менты 39 ИЛИ но ищне 23 передается в каналы более низкого уровня приоритета. Если в каналах более низкого уровня приоритета начался об.мен (в 51полнился первый шкл), то по щине 24 и через элемент 38 ИЛИ по 22 до окончания

o6 ;eiia выдается cniiia; )ета в каналы более в|)1сокогч) vpoBr;H приоритета.

Блок 3 .чредстаз.тяет собой оператпвн ю 1 амять с ма1ази1;ной ад|)есаписй. т. е. (; о - мац;:я :и1ппса1:1 ая it блок 3 г ервои. счит|,.аетея тоже первой. Для адресации ип(Ьормациониьгх Пегистров 47 иеио.чьзчетея рев-;.рСпв1П)1Й |)e.Tic-ip 46.

ij.ioj 3 |)аботает следлющтгм образо.м.

3 исходном соетомпии в гги Ьсуолкшионных )еги(трах 47 игф(рмация ()тс тст1зует, а иер;51. разряд рччирсивггого регистра 46 стаnoB.KMi Б едп. состоянне. }3ыход каждого трнгге)а сдвигОР.ого реггстра .подключен к управл; ю;це:чу входу, )а:-1рени15ощел; защкЧ) кг)д;(, соптБетств ()1Дег( им;p;n ;aци(ili;iov: состоят -; разрешается .запись в |;ервыи ип(| ормаппонный регистр 47. Запись т1рав.-щкхцег-о елог(а и информации з блюь: 3 осуiHkC; 1;.1яе-|ся . «Запис.. УСЗ и ;1п1|) через з.- емеш- 53 ИЛИ

20

ме.пы -Hi И и 5, И,лИ. За-цись a;ipeca ячейки О. (л- звод1;-гся CHi-na.-o.: «Запись ед)еса L гру1п;ь; 12 a;if)ecrbix процессор;; чс)сз -элементы 50 11 и 57 И.1И.

11г)сле ; ai;iiC i cJчepeд. -:1)ав.-1яющего слова. ин(|)ормации и.ти адреса нчсйк ; си1-|1а.-1ами записи, co6pai:i) па з,-|емен-j-ax 53 и 54 ИЛИ, через э.чемент 59 задержки осуцествляется сдвиг единицы в реверс)иом региетре 46 сдвига в c-roponv- с-гарщих разрядов, .подключая i-e.vi самьгм следующий ннформациощый рег-истр для записи очередного кода.

(Считывание ипформацпи об.мена из блока 3 1.)оизводмтся всегда из первого информацг:он1-(ого регистра 47 с.тедую.дими управ..ЯЮИ1ИМИ еи|-па,.1и: «Считывание -правляющего с.. «Считывание инфор.мации ; «Считывание адреса ячейки ОЗлЗ. Считывание у.иравляющего слова и информации ца И11фор.1ацио)иую магистраль производится че|)ез эле.мент 55 ИЛИ и элемент 52 И. (л и-гывание адреса ячейки ОЗУ производится через элемент 51 И. Одновременно сигна.л «Считывание адреса ОЗУ н(;ст пает на вход шифратора 48, на вьгходе которого (|)ор.ми)уется код операции непрогра.ммировапног-о ввода. Код непрогра.ммированной комапд1з1 ввода, состоящий из кода операции и адреса ячейки ОЗУ, по группе щин 15 пепрограммированной команды поступает в i-ipoiieccop. Носле считывания информации обмена сигналами считывания через элементы 55 и 56 ИЛИ и элемент 60 задержки в информационных регистрах 47 осуществляется сдвиг информации вправо на один регистр, т. е. в первый регистр переписывается ин(Ьормация из второго, во второй - из тре-гьего и т. д. Одновременно производится сдвиг единицы в реверсивно.м региетре 46 на один разряд в сторону млади1их разрядов, подготавливая таки.м образо.м д.тя заrihcn информации освободившийся iHKJ.JfjjiM;.ционный регистр 47. Инвертир( на элементе 58 НЕ сигнал с вылола .4cpi5oic) разряда pcBopciiBHOio регкст 1а 46 ( :еляст наличие гПкЬормании в о.ижс -5 и к;;,-, сигна; «Пал1 чие им(.1анки но 1.м);;в,1яющей 1нине 16 передается в O/KJK 2 ;1|)аГ)леиия. Выход 1|ослел11е1о разряда nepBOJo информационного регистра 47 как си1-н:ал «Признак АБ но управляклие -; тине 17 подключается к блоку 2 управления.

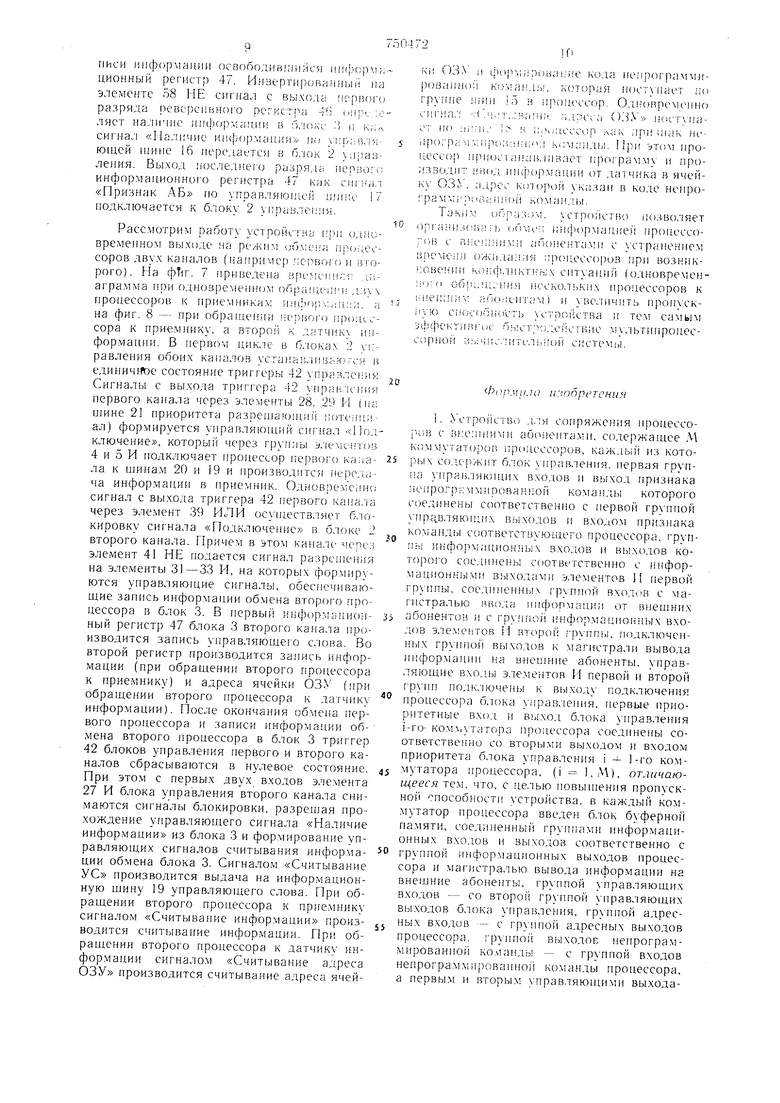

Рассмотрим работу уетро.йетва i.pH одновре.менно.м вы.ходе на ре/ким ьб. Hpoiiecсоров дву.х каналов (liaifpHMCp .первого и вгорого). На . 7 нриведеиа Bpi-.Mei -::: .г, аграм.ма одиовре.менном обранцчни д. ироцеесоров к нриемника.м HMi.,-iii;;;. а на фиг. 8 -- при обран1ен.ии первого нронсссора к нриемнику, а второй к датчику информации. В нервом цикле в б.юках 2 управления обоих каналов уетаиав,;1ивйк)г(;н Р, единишЛе соетояние триггеры 42 унравлеп.ия Сигналы с вы.хода триггера 42 уиравлс Н1я первого канала через элементы 28. 29 Н (на ишне 2 приоритета разре1нак)И1иГ1 поте.нц; ал) фор.мируется уиравляющий сшлшл Нод ключение, который через г)униы э.1еме1пч.)в 4 и 5 И подключает нронессор нервого капала к шииам 20 и 19 и нроизводится неред.с;ча иифор.мации в ирие.мник. Одновре.мсннс; сигнал с вы.хода триггера 42 нервого канала через элемент 39 ИЛИ осуществляет блокировку сигнала «Подключение в блоке 2 второго канала. Причем в этом канале чере:-; элемент 41 НЕ нодаетея сигнал разрешен.ия на элементы 31-33 И, на которых формир ютея унравляю1цие сигналы, обееиечиваюшие запись информации обмена второго процессора в блок 3. В первый информационный регистр 47 блока 3 второго канала нроизводится запись унравляюнтего слова. Во второй регистр нроизводится занись пнфктрмации (при обращении второго процессора к нриемнику) и адреса ячейки ОЗУ (при обращении второго нроцессора к датчику информации). После окончания об.мена первого процессора и записи инфорглации обмена второго процессора в блок 3 триггер 42 блоков управления нервого и второго каналов сбрасываются в нулевое соетояние. При это.м с первых двух входов эле.мента 27 И блока управления второго канала снимаются сигналы блокировки, разрец;ая нрохождение унравляюн его сигнала «Наличие информации из блока 3 и фор.мирование управляющих сигналов считывания инфор.мации обмена блока 3. Сигналом «Считывание УС нроизводится выдача на информационную щину 19 управляющего слова. При обращении второго процессора к прггемнику сигналом «Считывание информации нроизводится считывание информации. При обращении второго процессора к датчику информации сигналом «Считывание адреса ОЗУ производится считывание адреса ячейF ii O3 i ф(п;ир1)ваiiHe ко.та иепрограммировапно; коландь. ксторая иостхнает по rpyiifie iiJHH in в iipoueccop. Одновременно ,i .,:Haiiiit а.юееа () нс1ст иает 1(1 iii;;, 1 .. iijHiueccoii как ; ри;пак неlifKirpj: i;v;i:pci;i: i;iii:i команды. При этим процессор iiiiiiX.ic i ан:п1ливает г.рограмму и производит нвод ип(р(1рмации от датчика в ячейKV ОЗо, адрес которой указан в коде HeiijK)()|;а1П()й командт 1.

()6fi;i3;)M. ттр()йство 1()зво,1яет ()pia:-ni3(B;i :ь ио;;,,:; информацией нроцеесогов с RiieiiniHMii абоиенталп с ттраиеннем ожидания ; роцесео|)ов при возник :oBt -ini К().чфликть:ь;х ситуаций (одновременм); п . нсекольких npoiieccopoB к апснентам) и увеличить пропуекii K) ciiocnoHfiiTb стройства н тем самым 1|.фект.()е б;,1ст;м)дейсгвие м хльти пронессорЬ1ОЙ .;итель;;()й ciiCTeMiji.

Ф

2-f

элемента ИЛИ соединен со вторым входом четвертого элемента ИЛИ, выход которого через первый элемент задержки подключен к первому синхронизирующему входу регистра сдвига, выход третьего элемента ИЛИ соединен с управляющим входом четвертого элемента И и вторым входом пятого элемента ИЛИ, выход которого через второй элемент задержки соединен со вторым синхронизирующим входом регистра сдвига и с синхронизирующими входами информационных регистров, выход каждого разряда регистра сдвига подключен к управляющему входу соответствующего информационного регистра, а выход первого разряда - через элемент НЕ со вторым управляющим выхо, дом блока, группа вЫходов щифратора и группа выходов третьего элемента И подключены к группе командных выходов блока, группа выходов четвертого элемента И соединена с группой информационных выходов блока.

Источники информации, принятые во внимание при экспертизе

нЬ(и

Т Цикл

такты /8/2 3456781 254 6l&-f процессора . .

В1П Г

В2П

VnpoiSA9iK)iHee

КоЭа

САОбо (ШКНЫ9}

23 5-678iff54:5-678Y

Кой 5

(ющЕе (ШМНЫ9)

ВБП

АЭр.ОЗЙ (ш инь/12)

Ко8 8S (u nHw/O)

П;

МрийНйк ыноьормац /„-i -Умра)/. (Глобо М N-V

(/v о1сГоц0 -|-с ,,0- преемник

.

о

- цикл

И,

«формации

Фи2.4

UWKA

И

нс ормаци5

W2. J

ын

-/ Лър9ды

W2. в

8Д468246

Г

&-(П (М )

) в2П(ся;

8202(-1) Я (4) T-f2 (42)

о(9кАК)иение( -f5J

UHofj. Алагистр. ftbigoSa (IQ)

Запись УСд (-/4) Запись инср.2(Н4)

&ЫХ.Э272 (43;

Считыб УС2(-/4} Г2| (4; Т4°2 (45)

C4UTbig,UHop.204)

В24бВ24бд2

2 4

Фыг. 7

Авторы

Даты

1980-07-23—Публикация

1978-05-19—Подача